# A First Step for an INL Spectral-Based BIST: The Memory Optimization

Vincent Kerzérho, Serge Bernard, Philippe Cauvet, Jean-Marie Janik

### ▶ To cite this version:

Vincent Kerzérho, Serge Bernard, Philippe Cauvet, Jean-Marie Janik. A First Step for an INL Spectral-Based BIST: The Memory Optimization. Journal of Electronic Testing:: Theory and Applications, 2006, 22 (4), pp.351-357. 10.1007/s10836-006-0186-z. lirmm-00178634

## HAL Id: lirmm-00178634 https://hal-lirmm.ccsd.cnrs.fr/lirmm-00178634v1

Submitted on 1 Oct 2015

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## A First Step for an INL Spectral-Based BIST: The Memory Optimization

#### V. KERZÉRHO AND S. BERNARD

LIRMM, University of Montpellier, CNRS-161 rue Ada, Montpellier 34392, France vincent.kerzerho@nxp.com

bernard@lirmm.fr

#### V. KERZÉRHO AND P. CAUVET

NXP Semiconductors, 2 Rue de la Girafe B.P. 5120, Caen Cedex 5 14079, France vincent.kerzerho@nxp.com

philippe.cauvet@nxp.com

#### J. M. JANIK

GREYC-CNRS UMR 6072, University of Caen, 6 Bd Marechal Juin , Caen 14050, France Jean-Marie. Janik@greyc.ensicaen.fr

Received September 8, 2005; Revised July 6, 2006; Published Online December 8, 2006

Editor: A. Richardson

**Abstract.** Integral non-linearity (INL) is the main static parameter of analog-to-digital converter. This paper presents a comparison between different INL test techniques based on INL estimation from the spectrum of the converted signal. The most common technique is based on polynomial fitting of the INL curve. This technique is well suited to the estimation of a smooth INL curve without sharp transitions. The new method described in the paper is based on a Fourier series expansion of the INL curve. We demonstrate that this new technique allows a more efficient INL estimation. The comparison between the two techniques has been realized thanks to a metrics that considers the uncertainty of production test measurements. Finally, we propose a first step of the study of implementation feasibility of the INL estimation technique. This study focus only on the optimization of required memory.

**Keywords:** analog-to-digital converter testing, integral non-linearity, polynomial fitting, Fourier series expansion, fast Fourier transform

#### 1. Introduction

Because of the explosive evolution of very large scale integration and the increase of systems speed, mixed-signal devices' testing becomes increasingly complex and expensive. Analog-to-digital converters (ADC), a fundamental element of any mixed-signal system, is characterized by two different kinds of parameters which cannot be obtained by a single test. First, the static parameters (offset, gain errors and non-linearity) related to the ADC transfer function are measured by the histogram-based test procedure [5]. Then, a fast Fourier transform (FFT) test technique [7] is used to evaluate the dynamic performances (SFDR, SINAD, THD).

Actually, every static parameter has not the same importance and in many cases the evaluation of integral nonlinearity is enough. But, as long as the resolution of ADCs and the specified accuracy are increasing, the histogram-based method used to evaluate INL can lead to very long test times. For instance, considering a 14-bit ADC, the test can take several seconds, which is unacceptable in an industrial environment.

Consequently, in the past few years, many published papers have developed alternative methods and tried to integrate them onto the chip to propose an optimal built-in self test (BIST) architecture. The authors in [11] and [9] present a very attractive BIST application for analog and mixed-signal circuits. But this technique can't be applied to the test of ADC, because it is only usable on analog signal.

An attractive idea is to use the link between static and dynamic parameters. In particular, INL strongly influences the dynamic performances through harmonic generation. The information given by the spectral analysis could thus be used to extract INL values with a shorter testing time. This method requires much less samples than the histogram-based one, thus the time for processing, so the test time, can be significantly shortened. Two very different approaches can be used to evaluate the relationship between static and dynamic specifications: a) a statistical approach proposed in [2] consists in detecting devices whose one of functional parameter is overrun specifications, but this kind of statistical method is not viable in a BIST context; b) an analytical approach that consists in identifying the Fourier coefficients obtained with the classical FFT, with the parameters that describe the INL curve. Most of proposed techniques are based on polynomial interpolation of INL [1, 3, 10, 12], a more recent one [6] is based on the Fourier series expansion of the INL.

In this paper we focus on the analytical approach and our objective is to choose the best technique for fitting the INL and investigate if the implantation in a BIST architecture is possible.

In the second section INL fitting methods are described. The third section is dedicated to the comparison of the test methods based on polynomial fitting or on Fourier series expansion. Then, the last section describes an optimization of the algorithm based on Fourier series expansion to help implementation.

# 2. Methods for INL Extraction from Spectral Analysis

As mentioned above, the technique consists in determining an analytic expression of the relation between some spectral information of the converted signal and the integral non-linearity. Indeed, INL is closely related to the different harmonics of the converted signal for a sine wave as stimulus.

In order to define this analytic expression the idea is to describe the INL with function g based on a well-known mathematical form defined with  $\alpha_i$  coefficients:

$$INL \approx g(\alpha_1, \alpha_1, ... \alpha_{k \max})$$

(1)

Based on this function g, we have to find the direct relationship between the  $\alpha_i$  coefficients and the harmonic amplitudes in the converted signal as illustrate by the following equation:

$$[\alpha_0 \cdots \alpha_{K \text{max}}] = A \times \begin{bmatrix} S_0 \\ \vdots \\ S_{H \text{ max}} \end{bmatrix}$$

(2)

where A is the correlation matrix,  $S_0$  is the amplitude of the fundamental and  $S_i$  the amplitude of ith harmonic.

The first step of these kinds of technique consists thus in choosing the mathematical form allowing the best fit of the INL.

#### 2.1. Polynomial Fitting Technique

The more used technique is the polynomial fitting method [2, 9, 10, 12]. This technique consists in describing the INL (or the transfer function of the ADC) as an *n*-order polynomial:

$$INL(x) = \sum_{k=0}^{n} \alpha_k x^k$$

(3)

where  $x = 0...2^N - 1$  is the digital output code of the *N*-bit converter. In [3, 10], an low order polynomial is proposed. In [3], the wobbling technique is used to stabilize the harmonic bins during the correlation phase between polynomial coefficients and harmonic amplitudes. In [10], to identify the polynomial coefficients a piece-wise approximation is used to reduce the processing and thus optimize the hardware resources needed to plan on integrating it. The methods described in [1, 12] are based on high order polynomial. The extraction on the polynomial coefficients is performed by identification on the output signal spectrum [12] or using an analytical expression based on Chebychev polynomials [1].

All of these methods are based on polynomial interpolation. Obviously, the higher the degree of the polynomial, the more accurate the fitting is. In Section 3, we evaluate the efficiency of this kind of interpolation for a real INL measured by the histogram-based test procedure.

#### 2.2. Discrete Fourier Series Expansion

More recently, a method based on discrete Fourier series has been proposed [6]. A curve must be periodic to be expressed with a discrete Fourier series. In order to make the INL periodic, we use an extension of INL curve given by the following equations:

$$INL(x), 0 \le x \le 2^N - 1 INL(x + p.2^N) = INL(x), p \in Z$$

(4)

where  $x=0...2^N-1$  is the digital output code of the converter.

The periodic extension of the INL function leads to the following expression of the discrete Fourier series expansion:

INL(x)

$$\approx \frac{a_0}{2}$$

$$+ \sum_{k=1}^{2^N - 1} \left[ a_k \cos\left(2\pi \frac{k}{2^N} x\right) + b_k \sin\left(2\pi \frac{k}{2^N} x\right) \right]$$

(5)

The coefficients  $a_k$  and  $b_k$  can be computed from the kth complex Fourier coefficient  $c_k$  given by

$$c_k = \sum_{x=0}^{2^N - 1} INL(x) \cdot e^{\left(-j\frac{2\pi}{2^N - 1}kx\right)}$$

(6)

with

$$a_k = \frac{2}{2^N - 1} \text{Re}[c_k] \quad \text{and} \quad b_k = \frac{-2}{2^N - 1} \text{Im}[c_k]$$

(7)

where  $Re[c_k]$  and  $Im[c_k]$  are respectively the real and imaginary parts of the complex Fourier coefficient  $c_k$ .

The expression of the relationship between the Fourier coefficients  $a_k$ ,  $b_k$  of the INL interpolation and spectral components of the converted signal, which is more complex than in the case of polynomial interpolation, will be described in the following.

#### 3. Fitting Methods vs Real INL

The methods presented in the previous section are based on an INL interpolation by a polynomial or a discrete

Fourier series expansion. Before further optimization of the technique, we have to choose the best interpolation technique to fit a real INL.

#### 3.1. Comparison between the Two Fitting Methods

Our objective is to compare the INL measured by the histogram-based test technique and the estimated INL obtained by interpolation. The techniques proposed in [1, 3, 10, 12] are validated on low resolution ADC or with additional noise to smooth the INL. In this study, we focus on real 12-bit ADC TDA8769 from NXP [4].

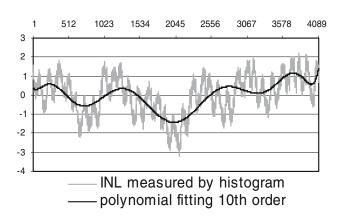

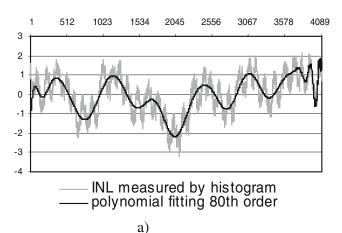

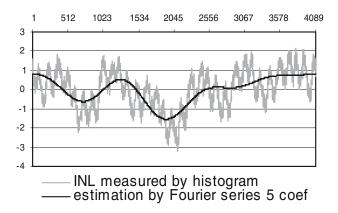

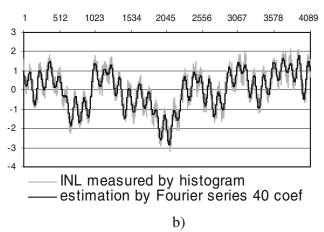

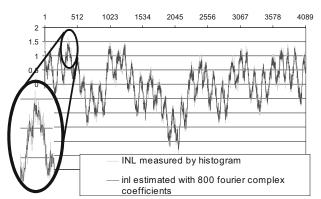

In order to compare estimation methods based on polynomials or Fourier series expansion in terms of hardware resource requirements, we consider N/2 complex coefficients (that correspond to N/2 real and N/2 imaginary coefficients) to compare with a Nth-order polynomial interpolation. We have conducted several experiments varying the values of N. Figure 1 gives some examples (N=10 and N=80) of comparison between INL estimations and INL measured using a histogram-based test procedure.

Two main observations arise from the analysis of these results. Firstly, for a low number of coefficients (N = 10)

Fig. 1. (a) Comparison between the INL curve for the histogram test realized on the DA8769 and the polynomial interpolation. (b) Comparison between the INL curve for the histogram test realized on the TDA8769 and the estimation by Fourier series expansion.

the results obtained with polynomial interpolation or discrete Fourier expansion are similar. The two methods allows to fit the smooth feature of INL curve, but from test point of view the results of the two methods in this case are not accurate enough to give a good evaluation of extreme values  $INL_{max}$  and  $INL_{min}$  needed for the test of ADC.

Secondly, when the number of coefficients increases we can observe a great change of efficiency of the two interpolation techniques. The polynomial interpolation only fits the smooth INL variations due to low order harmonics whereas the Fourier series expansion, also gives a good estimation the sharp variations of the INL curve.

Indeed, with a brief analysis, a Nth-order polynomial has only a maximum of N-1 local extremes that corresponds to a limited number of possible sharp variations. In contrast, a Fourier series with N/2 complex coefficients is composed (by definition) with N sine waves with different amplitude and phase and the sum of these sine waves allowing a larger variety of possible variations.

To conclude, polynomial model allows a good representation in the case of a smooth curve but because the actual INL curves have sharp transitions, for ADC testing, the Fourier series expansion seems to be the best solution to evaluate precisely the datasheet specifications:  $INL_{max}$  and  $INL_{min}$ . In the following section we make a deep evaluation of this technique.

# 3.2. Quantitative Evaluation of Fitting Technique Based on Discrete Fourier Series

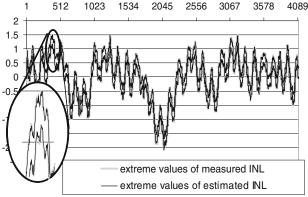

We have seen that fitting techniques based on discrete Fourier series achieve significantly better results than the method based on polynomials. Now, we have to evaluate precisely the estimation error for a real INL. Figure 2 shows the INL measured by histogram-based test technique on the TDA8769 converter and estimated with a very long discrete Fourier series (800 complex coefficients).

From a superficial observation, the INL seems to fit perfectly the measured INL, but when we zoom in the

Fig. 2. Comparison between INL measured by the histogram test and INL estimated by Fourier series expansion with 800 complex coefficients.

Table 1. Measured and estimated INL.

|                    | Measurement (LSB) | Estimation (LSB) | Error (%) |

|--------------------|-------------------|------------------|-----------|

| INL <sub>max</sub> | 1.64              | 1.42             | 13.4      |

| $INL_{min} \\$     | -2.45             | -2.29            | 6.5       |

curve (Fig. 2), we can observe that in spite of we use a very long Fourier series the estimated INL cannot follows all INL sharp variations. This might involve a large error on the estimated maximal value of INL needed for the test. In our study case, the standard deviation is as low as 0.12 LSB but the error on estimated maximal value of the INL is quite large. The Table 1 summarizes these results.

The error of estimation of the maximal INL value might be of 13.4% that might appeared as a very large error in a test context.

But in practice, the histogram-based test technique is sensitive to noise [8]. The measured INL is not the real INL but the real INL plus noise; that is why the results obtained with histogram-based test technique are not perfectly repeatable. To avoid this drawback some solutions based on dithering or averaging on different measurements are generally used.

But in our case, if we perform a large number of histogram-based test procedure on the same device and with the same test conditions we obtained a measurement dispersion of INL. Let us consider this dispersion as a measurement uncertainty.

Figure 3 gives the results of measured and estimated INL for 100 successive test procedures.

We can observe that when we take into account the measurement uncertainty, the estimated INL is globally inside the tolerance measurement. Now, if we focus on the maximal values of INL we obtained results given in Table 2.

The Fourier series expansion acts as an averaging of the histogram-based measurements. In other words, the Fourier series expansion offers a better repeatability of the INL estimation than the measurement itself by the histogram-based test.

Fig. 3. Comparison between extreme values of INL measured by the histogram test and INL estimated by Fourier series expansion with 800 complex coefficients.

Table 2. Measured and estimated INL and uncertainties.

|                    | Measure.<br>(LSB) | Measure.<br>uncertainty<br>(LSB) | Estimation (LSB) | Estimation uncertainty (LSB) |

|--------------------|-------------------|----------------------------------|------------------|------------------------------|

| INL <sub>max</sub> | 1.30              | 0.19                             | 1.34             | 0.16                         |

| $INL_{min}$        | -2.37             | 0.20                             | -2.38            | 0.18                         |

#### 4. Fourier Series Expansion Based Test

#### 4.1. Theory

The technique described in [6] consists in finding the analytic expression linking the interpolated INL based on Fourier series with the spectral information of the converted signal. Let us consider a sine wave as stimulus:

$$x(t) = V_0 \cos(2\pi f_0 t + \theta_0) + V_{DC}$$

(8)

where  $f_0$  is the frequency,  $V_0$  the amplitude,  $\theta_0$  the initial phase and  $V_{\rm DC}$  is the offset of the input signal. Now, if we consider the sampled signal "seen" by the ADC, we obtain the following expression.

$$x(n) = 2^{N} \left(\frac{V_0}{V_{FS}}\right) \cos\left(\theta n\right) + 2^{N} \frac{V_{DC}}{V_{FS}}$$

(9)

where

$$\theta_n = 2\pi \left(\frac{J}{M}\right)n + \theta_0$$

(10)

$V_{\rm FS}$  the full scale amplitude of the converter, J is the number of cycles and M the number of samples. After conversion through ADC, we obtain the distorted signal s(n):

$$s(n) = x(n) + INL(x(n))$$

$$= x(n) + \frac{a_0}{2} + \sum_{k=1}^{2^{N-1}} a_k \cos \begin{bmatrix} 2\pi k \left(\frac{V_0}{V_{FS}}\right) \cos\left(\theta_n\right) \\ + 2\pi k \left(\frac{V_{DC}}{V_{FS}}\right) \end{bmatrix}$$

$$+ \sum_{k=1}^{2^{N-1}} b_k \sin \left[ 2\pi k \left(\frac{V_0}{V_{FS}}\right) \cos\left(\theta_n\right) + 2\pi k \left(\frac{V_{DC}}{V_{FS}}\right) \right]$$

(11)

INL (x) is the Fourier series expansion (Eq. 5) of the INL. This equation can be expressed as following:

$$s(n) = x(n) + \sum_{h>0} S_h \cos(h\theta_n)$$

(12)

where  $S_h$  is the theoretical amplitude of the hth harmonic. The analytic expression of  $S_h$  depends whether h is even or odd:

$$S_{2h'} = 2(-1)^{h'} \sum_{k=1}^{2^{N}-1} [a_k \cos(k\alpha_2) + b_k \sin(k\alpha_2)] J_{2h'}(k\alpha_1)$$

$$S_{2h'+1} = 2(-1)^{h'} \sum_{k=1}^{2^{N}-1} [b_k \cos(k\alpha_2) - a_k \sin(k\alpha_2)] J_{2h+1'}(k\alpha_1)$$

(13)

where  $J_p(x)$  is the Bessel function of the pth order

$$J_p(x) = \sum_{n=0}^{\infty} \frac{(-1)^n x^{p+2n}}{n!(n+p)! 2^{p+2n}}$$

(14)

and

$$\alpha_1 = 2\pi \frac{V_0}{V_{\rm FS}}, \alpha_2 = 2\pi \frac{V_{\rm DC}}{V_{\rm FS}}$$

(15)

To reach the maximum dynamic range,  $V_{\rm DC} = V_{\rm FS}/2$ , thus  $\alpha_2 = \pi$ , and Eq. 13 can be simplified. This gives the following expression:

$$S_{2h'} = 2(-1)^{h'} \sum_{k=1}^{2^{N}-1} a_k (-1)^k J_{2h'}(k\alpha_1)$$

$$S_{2h'} = 2(-1)^{h'} \sum_{k=1}^{2^{N}-1} b_k (-1)^k J_{2h'+1}(k\alpha_1)$$

(16)

According to the Eq. 16 the analytical expression linking the interpolated INL with the spectral information of the converted signal can be expressed as follows:

$$[a_0...a_{k \max}, b_1...b_{K \max}]^T = T_{KMAX}^{-1} \begin{bmatrix} S_0 \\ \vdots \\ S_{H \max} \end{bmatrix}$$

(17)

where  $[S_0...S_{H\text{max}}]$  is the vector composed with the fundamental and the harmonics of the output signal, the vector  $[a_0...a_{K\text{max}}, b_1...b_{k\text{max}}]$  corresponds to coefficients of the Fourier series expansion (Eq. 5) of the INL,  $K_{\text{max}}$  is the order of the Fourier series expansion,  $H_{\text{max}}$  is the number of harmonics values extracted from FFT and  $T_{K\text{MAX}}$  is the following matrix:

$T_{KMAX}$

$$= \begin{pmatrix} 1/2 & A_{1}^{0} & \cdots & A_{K\,\text{max}}^{0} & B_{1}^{0} & \cdots & B_{K\,\text{max}}^{0} \\ 0 & A_{1}^{1} & \cdots & A_{K\,\text{max}}^{1} & B_{1}^{1} & \cdots & B_{K\,\text{max}}^{1} \\ \vdots & \vdots & \vdots & \vdots & \vdots & \vdots & \vdots \\ 0 & A_{1}^{H\,\text{max}} & \cdots & A_{K\,\text{max}}^{H\,\text{max}} & B_{H\,\text{max}}^{1} & \cdots & B_{K\,\text{max}}^{H\,\text{max}} \end{pmatrix}$$

$$\tag{18}$$

where

$$A_{k}^{0} = (-1)^{k} J_{0}(k\alpha_{1})$$

$$A_{k}^{2.p+1} = 0 \qquad \forall p \ge 0$$

$$A_{k}^{2.p} = (-1)^{p+k} .2 J_{2.p}(k\alpha_{1}) \qquad \forall p \ge 1$$

$$B_{k}^{2.p} = 0 \qquad \forall p \ge 0$$

$$B_{k}^{2.p+1} = (-1)^{p+k} .2 J_{2.p+1}(k\alpha_{1}) \qquad \forall p \ge 0$$

$$(19)$$

We do not want to describe the theory more in detail. Our objective is to evaluate the feasibility of the integration of this technique in terms of hardware resource requirements.

#### 4.2. Optimization

An INL BIST architecture based on the Fourier series expansion technique involves a pre-processing of the  $T_{K\rm MAX}^{-1}$  and the storage of this matrix. Then, we have to

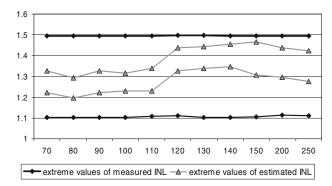

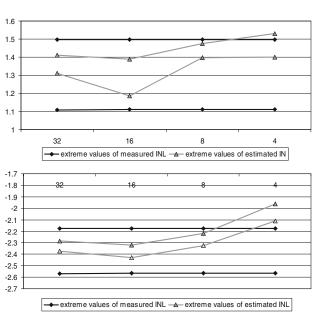

Fig. 4. Extreme values of both measured and estimated INL versus  $H_{\text{max}} = K_{\text{max}}$ .

extract spectral bins by FFT processing and perform the multiplication with  $T_{K\rm MAX}^{-1}$  matrix.

The two main hardware requirements are thus the FFT processing (or equivalent) and the storage of the matrix  $T_{K\rm MAX}^{-1}$  on-chip. In this study we only focus on the memory issue.

If we consider a Fourier series expansion of INL with 800 complex coefficients and using 800 spectral bins that correspond to the 800 first harmonics of the converted signal, the matrix  $T_{KMAX}$  would be composed of 641,200 different terms to be stored in N-bit words. This corresponds to an unacceptable memory size for a BIST solution.

Our objective is to simplify the matrix together with preserving the estimation accuracy. In practice, we take care to keep the estimated INL inside the measurement uncertainty of the histogram-based test.

## 4.2.1. Size Reduction of $T_{K\max}^{-1}$ Matrix.

The first step of the matrix optimization concerns its size defined by the number of harmonics ( $H_{\text{max}}$ ) and the number of coefficients ( $K_{\text{max}}$ ) in the Fourier series expansion.

As described in Section 3, the more Fourier series coefficients you use for the INL estimation, the better results you get. But the estimation also depends directly on the number of harmonics used in the spectrum of the ADC output signal. In practice, we have only access to the harmonics with frequency lower than the Nyquist frequency. In this study, we consider a number of 250 harmonics, which is quite realistic.

In this context, we have conducted several experiments varying the values of  $K_{\text{max}}$  and  $H_{\text{max}}$  from 70 to 250. Fig. 4 gives the estimation and measurement with the related uncertainty versus couples  $H_{\text{max}} = K_{\text{max}}$ .

As expected, we can observe that the estimation of the INL is not included in the measurement uncertainty for low number of considered coefficients. But from these results we can conclude that the value  $H_{\rm max} = K_{\rm max} = 110$  is enough in terms of estimation accuracy for a test application. This corresponds to  $111 \times 221$  matrix and 12,100 coefficients to be stored. In comparison to the initial situation, it is a significant reduction. But the memory size also depends on the size of stored words.

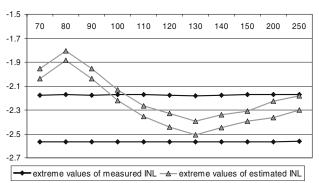

#### 4.2.2. Size Reduction of Stored Words.

Until now, all the computations were performed with floating point number with 64-bit IEEE double precision. In embedded circuitry context, we can use only fixed decimal with *N*-bit resolution. In order to reduce the memory size we have to optimize *N*, the length of used words. In the same way as previously, we search the limit value for which the estimated INL are beyond the measurement uncertainties. Fig. 5 shows the positive and negative extreme value of INL according to word size from 4 bits to 32 bits.

We can observe that only 8-bit word is needed to store the matrix. Thus finally, we need to store 12,100 words of 8 bits.

In practice, because we use low precision words, very few different values are needed in our process. It might be possible to store only this value and to use additional process to decompress these data for the INL estimation procedure. In our case study, there are only 126 different values in the matrix. So, in an extreme case, we need a very small memory of 126 words of 8 bits to store values

Fig. 5. Positive and negative extreme values of both measured and estimated INL versus word length.

needed for the INL estimation from the spectral analysis of the ADC output signal.

#### 5. Conclusion

We have shown that the polynomial fitting technique does not allow an efficient estimation of INL in the case of real medium or high resolution converter. These kinds of techniques give a good estimation of a smooth feature of INL variations but are not able to follow sharp variations of a real INL. In contrast, we have shown that the INL estimation based on Fourier series is suitable for test application and we have optimized the size of memory needed for the storage of the matrix used to extract INL characteristics from the spectral domain. Finally, we need to store only 126 different values of 8 bits for a 111 × 221 size matrix.

We are presently in the process of validating the matrix simplification on several types (resolution, architecture) of real ADCs and we investigate what is the most appropriate solution for an on-chip extraction of spectral characteristics from a temporal ADC output signal.

#### References

- F. Adamo, F. Attivissimo, N. Giaquinto, and M. Savino, "FFT Test of A/D Converters to Determine the Integral Nonlinearity," *IEEE Trans. Instrum. Meas.*, vol. 51, no. 5, pp. 1050–1054, Oct. 2002.

- S. Bernard, M. Comte, F. Azaïs, Y. Bertrand, and M. Renovell, "A New Methodology for ADC Test Flow Optimization," *Proc. IEEE International Test Conference*, pp. 201–209, 2003.

- N. Csizmadia and A.J.E.M. Janssen, "Estimating the Integral Non-Linearity of AD-Converters via the Frequency Domain," *Proc.* IEEE International Test Conference, pp. 757–761, 1999.

- Datasheet of TDA8769 converter: http://www.nxp.com/pip/ TDA8769HW\_8\_C1.html.

- J. Doernberg, H.S. Lee, and D.A. Hodges, "Full-Speed Testing of A/D Converters," *IEEE J. Solid-State Circuits*, vol. SC-19, no. 6, pp. 820–827, 1984.

- J.M. Janik, "Estimation of A/D Converter Nonlinearities from complex Spectrum," Proc. International Workshop on ADC Modeling and Testing, pp. 8–10, September 2003.

- M. Mahoney, "DSP-Based Testing of Analog and Mixed-signal Circuits," *IEEE Computer Society Press*, ISBN 0-8186-0785-8, 1987.

- 8. S. Max, "Fast Accurate and Complete ADC Testing," *Proc IEEE International Test Conference*, pp. 111–117, 1989.

- G. Prenat, S. Mir, D. Vasquez, L. Rolindez, "A Low-Cost Digital Frequency Testing Approach for Mixed-Signal Devices Using σΔ Modulation", Proc. IEEE International Mixed Signal Testing Workshop, pp. 1080–1090, 2004.

- S.K. Sunter and N. Nagi, "A Simplified Polynomial-fitting Algorithm for DAC and ADC BIST," Proc. IEEE International Test Conference, pp. 389–395, 1997.

- 11. D. Vasquez, G. Leger, G. Huertas, A. Rueda, and J.L. Huerteas, "A

- Method for Parameter Extraction of Analog Sine-wave Signals for Mixed-signal Built-in-Self-Test Applications," *Proc. IEEE Design, Automation and Test in Europe Conference*, pp. 298–303, 2004.

- F. Xu, "A New Approach for the Nonlinearity Test of ADCs/DACs and its application for BIST," *Proc. IEEE European Test Workshop*, pp. 34–39, 1999.

**Vincent Kerzérho** was born in 1979. He received the M.S. degree in computer science from the ISIM, Montpellier, France in 2003. He is currently pursuing the Ph.D. degree in a collaboration between the University of Montpellier and NXP. His research topics is the test of A/D and D/A converters.

Serge Bernard received the M.S. degree in Electrical Engineering from the University of Paris XI, France in 1998 and the Ph.D. degree in Electrical Engineering from the University of Montpellier, France in 2001. He is a researcher of the National Council of Scientific Research (CNRS) in the Microelectronics Department of the Laboratory of Computer Science, Robotics and Microelectronics of Montpellier (LIRMM). He is the co-director of the joint Institute for System Testing ISyTest between the LIRMM and NXP semi-conductors. His main research interests include Test, Design-For-Testability and Built-In-Self-Test for mixed-signal circuits and SiP and Design-For-Reliability for medical application ICs.

Philippe Cauvet is a senior principal engineer at NXP Semi-conductors Caen, France. He received his M.S. in physics—instrumentation from the Conservatoire National des Arts et Métiers in 1989. After several years in the automotive industry, he joined Philips Semiconductors in 1994 as a test engineer for high-speed data converters. He developed advanced test techniques, focusing on solutions for jitter and noise issues, which were presented in several international conferences and applied in commercial products. In 2004, he moved to a new group of Philips Semi-conductors (now NXP Semiconductors), where he is in charge of the development of advanced techniques for System-in-Package technologies. Aside from being a regular lecturer in engineering schools and of internal courses, he is the co-director of ISyTest (Institute for System Testing), the joint LIRMM–NXP institute created in year 2006.

Jean-Marie Janik was born in 1974. He received the engineering degree from the ENSICAEN, Caen, France in 1997 and the Ph.D. degree in digital signal processing from the University of Caen in 2002. In 1997, he joined Philips Semiconductors, where he worked as characterization engineer for high-speed A/D and D/A converters. Part of this activity led to the analyze and to compensate the defaults introduced by the test setup in order to improve the robustness of characterization procedures. In 2004, he joined the University of Caen, where he is now an associate professor of industrial computer science.