# Test Data Compression and TAM Design

Julien Dalmasso, Marie-Lise Flottes, Bruno Rouzeyre

## ▶ To cite this version:

Julien Dalmasso, Marie-Lise Flottes, Bruno Rouzeyre. Test Data Compression and TAM Design. VLSI-SoC 2007 - IFIP International Conference on Very Large Scale Integration, Oct 2007, Atlanta, GA, United States. pp.178-183, 10.1109/VLSISOC.2007.4402494. lirmm-00186171

# HAL Id: lirmm-00186171 https://hal-lirmm.ccsd.cnrs.fr/lirmm-00186171

Submitted on 4 Oct 2022

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **Test Data Compression and TAM Design**

Julien DALMASSO, Marie-Lise FLOTTES, Bruno ROUZEYRE LIRMM, Univ. Montpellier II/CNRS 161 rue Ada, 34932 Montpellier cedex 5, France {dalmasso, flottes, rouzeyre}@lirmm.fr, tel: (33)467418525, fax: 33)467418500

#### Abstract

Test Data Compression (TDC) techniques have been developed for reducing requirements in terms of Automatic Test Equipment resources. These techniques generally deal with stand alone circuits. In this paper, we explore the benefits of using TDC techniques in the context of core-based SoCs. TDC is used to reduce the test time by improving the parallelism of core tests without the expense of additional ATE channels. We first detail the constraints on test architectures and on the design flow inferred by the use of TDC. We propose a method for seeking an optimal architecture in terms of total test application time. The method is independent of the compression scheme used for reduction of core test data. The gain in terms of test application time for the SoC is over 50% compared to a test scheme without compression.

**Keywords**: System-on-Chip test, test resource partitioning, test data compression

#### 1. Introduction

Testing a SoC mainly consists in testing each core in the system. In order to provide accessibility to cores, the SoC architecture is completed by a Test Access Mechanism (TAM) and wrappers interfacing cores with the TAM (IEEE 1500 standard [1]). The TAM is generally a bus whose bitwidth fits the number of SoC test IOs. The TAM and the wrappers must be codesigned in order to reduce the global Test Application Time (TAT) according to the available Automatic Test Equipment (ATE) channels and to the cores test parameters such as the number of internal scan chains. The best trade-off between number of buses, bus bitwidth, wrappers size in terms of I/Os number and test parallelism must be established. This can be formulated as an optimization problem and several methods have been proposed to solve it (e.g. [2], [3], [4], [5], [6]).

In the meanwhile, as the complexity of SoCs designs keeps on growing, testing becomes more and more expensive with regard to test time and test pins requirement. While increasing the number of scan chains helps to reduce the test time of a given core, it also increases the bitwidth of the interfaces between wrappers and TAM. As a consequence, it also increases the bitwidth of the interface between the SoC and ATE or decreases test parallelism.

Several Test Data Compression (TDC) techniques aiming at reducing the number of visible scan chains have been developed for stand alone cores. Concerning test pattern compression (also called horizontal compression), they consist in compressing test patterns off line (i.e. reducing their bitwidth), storing the

compressed test data in the ATE, and decompressing test data on-chip for restoring initial test patterns; Input-data compression schemes rely on the fact that test patterns originally contain don't-care bits. These don't care bits do not have to be stored into ATE but can be supplied on-chip in some other ways. LFSRs [7][8], Xor networks [9] [10], ring generator [11], RAM [12] [13], arithmetic units [14] and test pattern broadcasting among multiple scan chains [15] [16] [17] constitute a range of solutions for minimizing the number of data to be stored into ATE. All these methods reduce therefore the number  $W_{\rm ATE}$  of necessary ATE channels required to test a stand alone core including N scan chains with N>  $W_{\rm ATE}$ .

Considering a parallel interface where W<sub>ATE</sub>=N, increasing the number of internal scan chains and the interface bitwidth allows reducing the test time of a core since the resulting test scheme requires fewer scan-in clock cycles. However, for a fixed number N of scan chains, the reduction of  $W_{\text{ATE}}$  with the help of a compression scheme (WATE < N), may result in additional test time compared to a solution where the number of ATE channels equals the number of scan chains (WATE =N). In fact, in this case, there is no more a one-to-one mapping between the ATE channels and the scan chains. Indeed, no matter the TDC technique is used, the TAT may increase because compressing the N-bits vectors on W<sub>ATE</sub>-bits words stored into ATE is not always possible. For keeping the fault coverage obtained with the original non compressed test sequence, it is then necessary to serialize the non-compressible patterns and to add a decompressor bypass mechanism or to look for additional compressible test patterns. In any case, a sideeffect is an increase in TAT.

Concerning test responses, several methods have been proposed (e.g. [18], [19]). Conversely to TDC, those test responses compaction techniques do not impact TAT and are independent of the core netlist and of the test responses sequence. Thus, they can be directly employed in the framework of SoCs design. In the remainder of this paper, we focus on test pattern compression only.

Only few studies on the use of TDC at system level have been published. In [20], [21], [22] TAM architectures using TDC have been presented but they rely on specific TDC techniques. Moreover, all architectural solutions are not considered since these techniques essentially target TAM architectures with a single decompressor for all cores or architectures with a dedicated decompressor per core (or connected to duplicated versions of the same core).

We propose here a method for exploring all TAM/TDC architectures including dedicated and shared decompressors. The final goal is to generate test

architectures and test schedules that minimize the system TAT. The proposed technique is independent of the adopted compression scheme.

Section 2 discusses the implication of TDC insertion at SoC level. The problem formulation as well as notations are given is Section 3. The algorithm is detailed is Section 4 whereas experimental results are reported in Section 5. Finally, Section 6 draws some conclusions.

#### 2. SoC test architecture and compression

A SoC test architecture is proposed by the IEEE 1500 Standard. It mainly consists of a TAM bus and wrappers around cores. The TAM links the SoC's test IOs and the cores. Each core wrapper interfaces the core and the TAM bus. The test time of a core depends, among other things, on the size of its wrapper in terms I/Os interfaces with the TAM

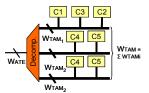

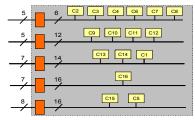

As in [2] and [3], we assume a TAM architecture organized around a partitioned test bus, each core being connected to one sub-bus, as depicted in Figure 1 in which the TAM is split into three sub-buses. Cores connected to the same sub-bus are tested serially (e.g. C1, C2, C3), cores assigned to different TAMs can be tested in parallel (e.g. C1 and C4 or C1 and C5). We do not make any assumptions about the wrappers of the cores: either the wrappers of the cores have been already designed (wrapper1500-ready cores), or they have to be designed when building the test infrastructure.

Figure 1: TAM architecture

In the rest of this paper,  $W_{TAM}$  denotes the TAM bitwidth, and  $W_{TAM i}$  the bitwidth of each sub-bus.

Without changing  $W_{\rm ATE}$ , the TAM bitwidth can be increased thanks to the use of TDC techniques. The tests parallelism can be therefore increased resulting in a shorter test time.

However, as explained in the introduction, TDC may also increase test time of individual cores. More precisely, for a fixed number N of scan chains (or equivalently for a fixed wrapper size), the test time of a core increases when the number of bits  $W_{ATE}$  at the input of the decompressor gets smaller. For instance, using the TDC technique presented in [14], the test of the S38417 benchmarks circuit with N=16 scan chains needs 21451 clock cycles when  $W_{ATE}=10$  and 38867 clocks cycles when  $W_{ATE}=3$  (see for instance, results given in Figure 7). In the remaining, the ratio  $W_{ATE}/N$  is denoted by  $\rho$ .

In this paper, we question the benefit of using TDC in the context of the design of test infrastructure for SoCs.

Let's recall that, under the chosen TAM model, building the test infrastructure mainly consists in: 1) finding a partition of the bus into p sub-buses and determining their bitwidth, 2) assigning the cores to the p sub-buses, and designing their wrappers 3) deriving a test schedule so that the total test time is minimized. An underlying data of these tasks is the test times of cores.

The test time of a core also depends on the size and the structure of its wrapper (size means here the number of visible scan chains). The wrapper size must be narrower than the sub-bus to which the core is connected to.

The use of TDC impacts the building of the test infrastructure in two aspects:

- 1) Since TDC modifies the test times of individual cores, the decompression ratios  $\rho$  must be established *during* the design of the test infrastructure and not after.

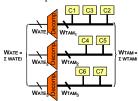

- 2) Decompressor sharing can be envisaged in two ways. Either a decompressor feeds several sub-buses (Figure 2.a) or feeds a single sub-bus (in Figure 2.b).

a) One decompressor for several sub-buses

b) A single decompressor per sub-bus

Figure 2: TAM/decompressors architectures

The first architecture style leads to prohibitive CPU time when exploring architectural solutions. Indeed the evaluation of a solution (its test time) requires to define bus partitioning, core assignment, test parallelism, test sequence definition and finally compression of this sequence. Figure 2.a for instance depicts only one bus partitioning and core assignment possibility. It includes several test parallelism solutions (e.g. either C1 and C4 tested in parallel or C1 and C5). In turn, each one necessitates building the actual test sequence by concatenating the test sequences of the cores tested in parallel. Finally the resulting test sequence has to be compressed in order to obtain the actual test time. Another way of dealing with this model is 1) to build the optimal test infrastructure and related test schedule without looking at compression 2) derive the whole SoC test sequence and compress it. Doing so, there is no chance to obtain an optimal solution: the test infrastructure (without decompressor) is built given the test times of cores which are modified by the compression. We did such an experiment with the example given in section 5. Doing so, the obtained test time is 65699 cycles while a solution with 57941 cycles has been obtained using the method we propose here.

Conversely, the cores connected downstream a decompressor in the second architecture style are tested one after the other. The test sequences to compress are simply those of the cores and not issued from the concatenation of several ones. The compression of the test sequences can therefore be done independently of the test infrastructure building process. This alleviates the problems raised by the first model.

So in the remaining, we consider the second architecture style and we propose a method for conjunctly building up the TAM, the wrappers (if needed) and the decompressors.

Each path for the ATE channels, through a decompressor, up to sub-bus is called a line. The architecture depicted in Figure 2.b is composed of three lines. It must be noted that within this architectural model, and in the absence of additional constraints such as power limit for instance, the test scheduling is trivial (as without compression). The test time on a line is simply the sum of the individual test times of the cores since there is no test parallelism on the line. The total TAT is the maximal test times over the lines.

#### 3. Problem statement and notations

We state the problem of building the test infrastructure with decompressors as an optimization problem. Given the number of available ATE channels, the bitwidth of the TAM, and the test patterns, we want to determine the best partition of the test infrastructure into p lines and the interconnection of the cores to the sub-buses so that the TAT is minimized.

In the remaining, we will use the following notations. Let n be the number of cores under test, we the number of visible scan chains for every core c=1...n. Let p be the number of lines, and let  $W_{ATE\_i}$  and  $W_{TAM\_i}$ , i=1,...,p be respectively the number of ATE channels and the bitwitdh of sub-bus on line i. Let  $\rho_i=W_{ATE\ i}/W_{TAM\ i}$  be the decompression ratio of line i Let's  $t_{w_c,\rho}^c$  denote the

test time of core c with a  $w_c$  bits wrapper for a ratio  $\rho$ .

The problem is to determine:

- the line number p

- the bitwidths  $W_{ATE i}$  and  $W_{TAM i}$  for i=1,...,p;

- an assignment of the cores to the lines;

- optionally, the wrapper size w<sub>c</sub> of each core,

- and a test schedule so that TAT is minimal;

The following constraints must be obeyed:

$$W_{ATE} = \sum_{i=1,\dots,p} W_{ATE\_i}$$

cons.1

$$W_{TAM} \ge \sum_{i=1,\dots,p} W_{TAM\_i}$$

cons.2

$$W_{TAM} \ge \sum_{i=1,\dots,p} W_{TAM_i}$$

cons.2

$$W_{TAM i} \ge W_{ATE i}$$

, i=1,..,p cons.3

$$w_c \le W_{TAM-i}$$

if c is connected to line i. cons.4

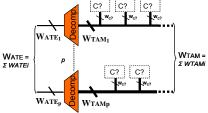

Variables to be determined are depicted in bold in Figure 3.

Figure 3: Problem statement

Concerning core wrappers, there are two cases: either the cores are wrapper-ready or their wrappers have to be designed. In the later case, it must be noted first that 1≤w<sub>c</sub>≤max(#PIs,#POs)+ #scan chains. Secondly, once w<sub>c</sub> is determined, designing the wrapper so that the test time

of the core is minimized resumes simply to balance the lengths of the visible scan chains. This won't be detailed in the remaining.

In the scenario where the wrappers are already fixed, if a core is assigned to a line i for which W<sub>TAM i</sub> is strictly greater than the wrapper size w<sub>c</sub>, only w<sub>c</sub> bits of TAM\_i are connected to the wrapper, the test time of the core is considered to be the same as if TAM i was w<sub>c</sub> bits wide. For instance, and for a core c with  $w_c = 4$ , its test time  $t_{w_c,\rho}^c$  is the same whether it is assigned to a line with  $W_{ATE} = 2$  and  $W_{TAM} = 6$ , or to a line with  $W_{ATE} = 2$  and  $W_{TAM} = 4$ , i.e.  $\rho = 2/4$ .

The test time  $t_{w_c,\rho}^c$  of a core c must be pre-computed for all possible values of  $\rho$  (from 1 to  $1/w_{\text{c}}$ ). (cf. section 4 to see how this process can be speeded up). For examining the benefit of using TDC when designing the test infrastructure of a SoC, we developed the heuristic presented hereafter.

#### 4. Algorithm

The general flow chart of the method is depicted in Figure 4. First, all the possible combinations of lines are explored (line 1 and 2). The ATE channels partition can be easily determined knowing the total WATE width and the number of lines p by applying the formula of the partition of integer numbers. Namely, the number X(n,p)of partitions of a set of n elements into p subsets can be

$$X(n, p) = \sum_{k=1}^{p} X(n-p, k)$$

with  $X(n, n) = X(n, 1) = 1$

and X(n,p) = 0 if p > n

For instance, 10 ATE channels can be partitioned into p=3 subsets in X(10,3)=8 different ways (1+1+8, 1+2+7, 1+2+7, 1+2+7)1+3+6, etc...).

Then for each ATE channels partition, all the compatible partitions of the TAM are calculated. A partition of the TAM is said to be compatible with a partition of the ATE channels if cons.3 is verified for all p lines. Furthermore, if cores are wrapper-ready i.e. w<sub>c</sub> are fixed, the number of TAM partitions to be explored can be further reduced by considering cons.4. In other words, the narrowest TAM must be large enough to support the narrowest wrapper. It must be noticed that if W<sub>TAM i</sub>=W<sub>ATE i</sub>, no decompressor is present on this line. For a pair of partition, (ATE channels partition and TAM partition), cores must be assigned and the scheduling performed to obtain the TAT of this architecture (line 3 in Figure 4).

- 1. For all ATE channels partitions into p parts

- For each compatible TAM partition into p parts

- Find the best assignment of the cores to the p lines (that minimize TAT) ->cf Fig 5.

If this assignment reduces the global TAT, memorize this assignment and ATE/TAM architecture

Figure 4: Partition algorithm

Seeking for the assignment of cores to lines that minimizes TAT is an NP-complete problem. So we developed the heuristic given in Figure 5.

// Initial Solution

- Sort cores by decreasing test data volume

- Assign each core to the largest bus so that TAT increases as few as possible.

// Improvement of the solution

- · While TAT is reduced

- Find the line i with the highest TAT<sub>i</sub>

- For each core c assigned to i,

- For all other lines k ( k ≠ i )

- Move core c from i to k

- Compute newTAT and memorize i, k, c and newTAT

- Move back core c from k to i

- Move core c from i to k such that:

- 1) the smallest TAT has been obtained

- 2) the number of useless bits on k is minimized

- 3) the standard deviation between TAT<sub>i</sub> of all lines is maximized

Figure 5: Assignment algorithm

The first step determines an initial solution of the architecture, i.e an initial assignment of cores to the TAMs. Each core is positioned on the largest possible TAM i.e. and its wrapper size is set according to (cons.4). If the core is wrapper-ready, it is assigned to the smallest bus i.e. respecting cons.4. For instance, in case of 3 TAMs having resp. 5, 7 and 10 bits, a core with a 6-bits wrapper will be assigned to the 7 bits TAM. The first bus is not large enough to be connected to the core's wrapper (cons.4). The second bus is preferred to the third one since, a priori, it is beneficial to reserve the larger one for cores with larger wrappers.

The second step consists in improving this initial solution. For this, the cores are moved to other lines to reduce the global TAT.

The principle is to move a core from the line with the highest TAT to another line so that the global TAT gets reduced as much as possible. For that, all cores of the line are virtually shifted to other lines and TATs are computed accordingly. The move that gives the highest benefit is chosen. In case of equality, the algorithm chooses (Core c, Line i) such that the number of useless bits on the line is minimized i.e.  $W_{TAM\_i} - w_c$  is minimal. This is done for getting more room to move cores with larger wrappers to large buses, in next steps. Similarly, a third order criterion is used to unbalance test times over lines.

Let's recall that the computation of TAT is straightforward ( $TAT_i$  denotes the test application time on line i):

TAT = max(TAT<sub>i</sub>, i = 1,...,p) and TAT<sub>i</sub> =

$$\sum_{\text{cores assigned to i}} t_{w_c \cdot p_i}^c$$

Note that the test times  $t_{w_c,\rho}^c$  for all cores and for all compression ratios ( $W_{\rm ATE\_i}/w_c$ ) are inputs of the proposed algorithm. These data are necessary to compute the system TAT (i.e. schedule the tests). Thus, as a preprocess, the compression algorithm must be performed for all compression ratios, for all cores and all wrapper sizes. This can be very CPU expensive depending on the compression technique used. We propose here an alternative to the exhaustive computation

First, when the wrapper size is questioned, let's recall that as reported by many authors, the test time of a core, in the absence of compression i.e.  $\rho$ =1, is a stepwise decreasing function of the wrapper size. Furthermore it depends on the number of test vectors and not on the vectors themselves. Figure 6 reports the test time versus  $w_c$  for the  $10^{th}$  core of the D695 ITC'02 benchmark. In general the number of steps is small. Only 15 optimal values of  $w_c$  have to be considered for this core.

**Figure** 6: ITC'02 d695 benchmark (core 10) Test time vs wrapper size

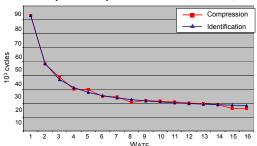

Secondly, whatever the TDC technique is used, the same behavior of the test time of cores versus decompression ratio can be observed (for a given wrapper size w<sub>c</sub>). It can be identified to the function:

$$t_{w_c,\rho}^c = \frac{\alpha}{\rho} + \beta$$

Only two values of t for one core are sufficient to identify  $\alpha$  and  $\beta$ . The estimated values of  $t_{w_c,\rho}^c$  for several decompression ratios are thus obtained from only two measured values instead of  $w_c$  computations. In order to improve the precision of the estimation, the

Figure 7: S38417 ( $w_c = 16$ ) computed/estimated test times

compression algorithm is performed with the first and last decompression ratio values.

This property has been validated with the TDC method [14]. This compression scheme is applicable with intellectual property cores and it is Test Suite independent, i.e. it does not required specific test generation or fault simulation.

The measured and estimated  $t_{c,p}$  values are reported on Figure 7 for the ISCAS'89 s38417 benchmark (16-bits wrapper). The maximum error between measured and estimated values is smaller than 1%. Similar results have been obtained for all ISCAS'89 benchmarks and several configurations of wrappers.

As a final remark let's note that the proposed heuristic can be very easily adapted to additional constraints such as power limit, precedence constraints, etc...

#### 5. Results

The first SoC used for experiments is the one described in [9][20] and depicted in Figure 8. It is composed of 16 ISCAS'89 benchmark circuits used as cores (i.e. with wrappers).

Figure 8: SoC example from [20]

In a first series of experiments, we assume that the wrappers are already designed. Wrappers sizes are equal to the number of scan chains. The test sequences of the circuits have been obtained with the Synopsis ATPG tool TETRAMAX [23] and compressed with our TDC technique described in [14]. The characteristics of the cores are given in table 1.

| Core number | #scan chains (wc) | test cycles |  |

|-------------|-------------------|-------------|--|

| 1 to 4      | 5                 | 9331        |  |

| 5 to 8      | 6                 | 9030        |  |

| 9, 10       | 10                | 8804        |  |

| 11,12       | 12                | 16048       |  |

| 13,14       | 14                | 19845       |  |

| 15 16       | 16                | 45760       |  |

Table 1: Characteristics of the cores

In the experiments, we have set the number of ATE channels to 32 and the maximal total TAM bitwidth to 64. The algorithm has been applied with a number of lines ranging from 2 to 6. Results are reported in Table 2.

| р | # conf.   | TAT    | Lines' parameters<br>(W <sub>ATE_i</sub> / W <sub>TAM_i</sub> ) | #bits<br>used on<br>TAM |

|---|-----------|--------|-----------------------------------------------------------------|-------------------------|

| 2 | 522       | 127413 | (16,16) / (16, 48)                                              | 30                      |

| 3 | 44639     | 90457  | (8,9,15) / (14,16,34)                                           | 42                      |

| 4 | 1345142   | 68361  | (5,7,8,12) /<br>(7,14,16,27)                                    | 53                      |

| 5 | 18605924  | 57941  | (5,5,7,7,8) /<br>(6,12,14,16,16)                                | 64                      |

| 6 | 142238520 | 57941  | (1,4,5,7,7,8) /<br>(1,5,12,14,16,16)                            | 63                      |

Table 2: Architectures exploration results

The number of lines is given in col.1. Col.2 indicates the number of architectural configurations that have been explored while col.3 gives the TAT of the elected architecture. The details of the test infrastructure are given in col.4. The last column indicates the actual number of TAM bits.

For instance, for an architecture with 3 lines, 44639 configurations have been explored. The optimal one leads to a TAT equal to 90457 test cycles. The architecture contains 3 decompressors such that  $(W_{ATE\_1}, W_{TAM\_1}) = (8,14), (W_{ATE\_2}, W_{TAM\_2}) = (9,16)$ , and  $(W_{ATE\_3}, W_{TAM\_3}) = (15,34)$ .

From this table, some observations can be done:

- All potential test infrastructures are explored including those that do not contain decompressors. For

instance, for the 2 lines configuration, the optimal architecture does not include a decompressor on the first bus  $W_{\text{ATE 1}} = W_{\text{TAM 1}} = 16$ .

- While a budget of a 64 bits TAM has been given, all those bits are not necessarily connected to cores (and thus are useless). This is the case for p=2, 3, 4, 6. This is mainly due to the wrapper sizes chosen for the cores. This means that the actual bitwidth of the TAM is smaller than 64 bits.

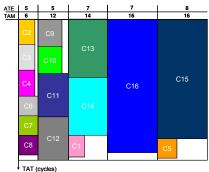

Among all experiments, the best TAT is obtained with p=5 lines. The corresponding test schedule and architecture are given in Figure 9 and Figure 10. Test parallelism cannot be fully exploited with smaller values of p since at most p cores can be tested in parallel. For larger values of p (6, 7, ...), the relative sizes of the wrappers to the possible TAM\_i widths act as a brake on parallelisation.

Figure 9: Test schedule for a  $32 \rightarrow 64$  bits decompression with 5 lines. TAT = 57941 cycles

We measured the benefit of using compressors in SoCs test architectures by comparing them to standard architectures i.e. without using compression, while setting the same environmental constraints. In the first case, we assumed the same limit on the numbers of available ATE channels (32 bits and thus a TAM of 32 bits), in a second case, the same area budget for building the TAM (64 bits wide and thus 64 ATE channels).

Figure 10: Final architecture

For the first case, the TAT is 127413 cycles for a standard TAM architecture when a number of sub-buses p ranges from 2 to 4 and 131210 cycles when p equals 5 or 6. These results have to be compared with the 57941 cycles when compression is used. Thus, the use of TDC technique in the context of SoC infrastructure design leads to a gain of 54.5% in terms of TAT for this example (at the expense of area overhead: larger TAM, decompressors).

In the second case, i.e. a TAM of 64 bits (which means 64 ATE channels for a standard architecture vs 32 ATE

channels with compression), comparative results are reported in Table 3. At the evidence, TDC has allowed to divide by two the number of ATE channels at the expense of only a 4% increase on TAT.

|         | Proposed architecture:       |                     | Standard architecture:       |        |

|---------|------------------------------|---------------------|------------------------------|--------|

|         | $W_{ATE} = 32, W_{TAM} = 64$ |                     | $W_{ATE} = 64, W_{TAM} = 64$ |        |

| # lines | TAT                          | actual TAM bitwidth | # lines                      | TAT    |

| 2       | 127413                       | 30                  | 2                            | 127413 |

| 3       | 90457                        | 42                  | 3                            | 90457  |

| 4       | 68361                        | 53                  | 4                            | 68361  |

| 5       | 57941                        | 64                  | 5                            | 57941  |

| 6       | 57941                        | 63                  | 6                            | 55738  |

Table 3: Architectures Comparison (fixed wrappers)

We did the same experiments, but without assuming fixed wrappers size i.e. letting the method determines the most adequate wrappers structures. TAT are reported in Table 4. It can be fist noted that since wrappers structures are questioned, bus width can be better utilized leading to shorter TAT. Secondly, as in the previous case, the use of TDC leads to a large TAT improvement.

| р | 32→64 Decomp.<br>Architecture | Standard 64 bits<br>Architecture | Standard 32 bits<br>Architecture |

|---|-------------------------------|----------------------------------|----------------------------------|

| 2 | 66596                         | 52953                            | 97216                            |

| 3 | 61277                         | 49814                            | 96624                            |

| 4 | 57337                         | 49129                            | 96736                            |

| 5 | 55101                         | 48592                            | 96624                            |

| 6 | 54140                         | 48517                            | 96563                            |

Table 4: Architectures Comparison

The same kind of experiments has been performed on the g1023 ITC'02 benchmark. Unfortunately, in the ITC'02 suite, neither cores netlists nor test patterns are provided, all information necessary to perform compression. Thus we got random patterns including 80% of don't care bits (many authors report a percentage of more than 90% of don't care bits on industrial circuits). Comparative results are given in table 5.

|   | Decomp.<br>Architecture |       | Standard Architecture |         |         |

|---|-------------------------|-------|-----------------------|---------|---------|

| р | 32→64                   | 16→32 | 64 bits               | 32 bits | 16 bits |

| 2 | 17492                   | 26256 | 15153                 | 19633   | 33952   |

| 3 | 14185                   | 23084 | 11274                 | 17892   | 33718   |

| 4 | 12996                   | 21409 | 11274                 | 17235   | 33824   |

| 5 | 12399                   | 20719 | 11274                 | 17215   | 33824   |

| 6 | 12138                   | 20667 | 11274                 | 17235   | 33824   |

Table 5: g1023 Comparison results

### 6. Conclusion

In this paper, we explored the benefits of horizontal test data compression techniques in the context of the design of SoC test infrastructures. The increase in parallelism allowed by compression is fully exploited to reduce the test application time of the SoC. We propose a method that explores all architectural solutions from one single decompressor for all cores to architectures with a dedicated decompressor per core. Results obtained on a SoC based on ISCAS'89 benchmarks circuits have confirmed this TAT reduction with a ratio of more than 50%. While the experiments have been performed using

a particular TDC technique, the method is independent of the used TDC.

Presently, this method is geared to minimize the test time. Area overhead induced by decompressors and TAM is not taken into account. Seeking the best tradeoff is a direction for future research.

#### 7. References

- [1] IEEE standard for embedded core test IEEE Std. 1500-2004.

- [2] V. Iyengar et al.. "Test wrapper and test access mechanism co-optimization for system-on-a-chip". J. Electronic Testing, vol. 18, no. 2, pp. 213-230, April 2002

- [3] V. Iyengar et al., "Efficient Wrapper/TAM Co-Optimization for Large SOCs", DATE'02, pp. 491-497.

[4] V. Iyengar et al. "Wrapper/TAM co-optimization,

- [4] V. Iyengar et al. "Wrapper/TAM co-optimization, constraint-driven test scheduling, and tester data volume reduction for SOCs", DAC '02. pp. 685-690.

- [5] S.K. Goel, E.J. Marinissen, "Effective and Efficient Test Architecture Design for SOCs", ITC'02, p: 529-535.

- [6] G. Zeng, H. Ito, "Concurrent core test for SOC using shared test set and scan chain disable", DATE'06, pp. 1045-1050.

- [7] A. Jas, B. Pouya, N.A. Touba, "Virtual Scan Chains: a means for reducing scan length in cores", VTS'00, pp: 73-78.

- [8] L-T Wang et al., "VirtualScan: a new compressed scan technology for test cost reduction", ITC'04, pp. 916-924.

- [9] I. Bayraktaroglu, A. Orailoglu, "Test volume application time reduction through scan chain concealment", DAC'01, pp: 151, 155

- [10] K.J. Balakrishman, N.A. Touba, "Reconfigurable linear decompressor using symbolic Gaussian elimination", DATE'05, pp. 1130-1135.

- [11] J. Rajski et al., "Embedded deterministic test for low cost manufacturing Test", ITC'02, pp: 916-922.

- [12] L. Li, K. Chakrabarty, N. A. Touba "Test data compression using dictionaries with selective entries and fixed-length indices", ACM TODAES, Vol. 8, No. 4, October 2003, pp. 470-490.

- [13] A. Würtenberger, C.S.Tautermann, S.Hellebrand, "Data compression for multiple scan chains using dictionaries with corrections", ITC'04, pp. 926-935.

- [14] J. Dalmasso, M.L. Flottes, B. Rouzeyre, "Fitting ATE Channels with Scan Chains: a Comparison between a Test Data Compression Technique and Serial Loading of Scan Chains", DELTA'06, pp. 295-300.

- [15] N. Sitchinava et al., "Changing the scan enable during shift", VTS'04, pp: 73-78.

- [16] H. Tang, S.M. Reddy, I. Pomeranz, "On reducing test data volume and test application time for multiple scan chain designs", ITC'03, pp: 1079-1088.

- [17] B. Arslan, A. Orailoglu, "CircularScan: a scan architecture for test cost reduction", DATE'04, pp. 1290-1295.

- [18] S. Mitra, K.S. Kim, "X-compact, an efficient response compaction technique for test cost reduction", ITC 02, pp. 311-320

- [19] J. Rajski,et al., "Finite memory test response compactors for embedded test applications", IEEE Trans. on CAD, April 2005, Vol. 24-4, pp: 622-634

- [20] V. Iyengar, A. Chandra, "A Unified SOC Test Approach Based on Test Data Compression and TAM Design", Proc. IEEE DFT'03, pp. 511-518

- [21] P.T. Gonciari, B.M. Al-Hashimi, "A Compression-Driven Test Access Mechanism Design Approach", ETS'04, pp: 100-105.

- [22] P.T. Gonciari, B.M. Al-Hashimi, N. Nicolici, "Integrated Test Data Decompression and Core Wrapper Design for Low-Cost System-on-a-Chip Testing", ITC'02, p. 64-70.

- [23] www.synopsys.com/products/test/tetramax\_ds.html