### Evaluation et Optimisation de Chemins Combinatoires

Xavier Michel, Philippe Maurine, Nadine Azemard, Daniel Auvergne

### ▶ To cite this version:

Xavier Michel, Philippe Maurine, Nadine Azemard, Daniel Auvergne. Evaluation et Optimisation de Chemins Combinatoires. Colloque du GDR CAO de Circuits et Systèmes Intégrés, May 2002, Paris, France. pp.173-176. lirmm-00269329

## HAL Id: lirmm-00269329 https://hal-lirmm.ccsd.cnrs.fr/lirmm-00269329

Submitted on 11 Sep 2019

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **Evaluation et Optimisation de chemins combinatoires**

X. MICHEL, P. MAURINE, N. AZEMARD et D. AUVERGNE

LIRMM : Laboratoire d'Informatique ,de Robotique et de Microélectronique de Montpellier, UMR 5506 Université Montpellier II / CNRS, 161 rue ADA , 34392 Montpellier cedex 5, France

Phone: (33) 4 67 41 85 21, Fax: (33) 4 67 41 85 00, E-mail: azemard@lirmm.fr

#### Résumé

Cet article met en évidence l'utilisation de méthode de classification de chemins pour l'optimisation des performances de circuits combinatoires. La classification de chemins est développée à partir de la technique incrémentale. Les contraintes de délai et de puissance/surface sont respectées en utilisant des alternatives de redimensionnement des chemins d'un circuit, ceci avec une évaluation réaliste des retards des portes. Cette technique est appliquée à l'énumération et l'optimisation de chemins sur des benchmarks ISCAS'85.

**Mots Clés:** technique d'exploration de graphe, classification de chemins, sélection de portes, retard-puissance.

#### 1. Introduction

Les outils [1] de conception requièrent des temps et des ressources de calcul trop importantes pour pouvoir gérer la complexité et l'hétérogénéité des circuits actuellement en développement. Les futurs outils doivent pouvoir manipuler des circuits très complexes dans une approche d'abstraction multiniveaux tout en considérant les phénomènes parasites induits associés aux technologies submicroniques. Ils doivent pouvoir prendre en compte les contraintes de vitesse et de consommation de puissance [2]. Pour cela il devient essentiel de disposer, au niveau le plus élevé de la démarche de conception, d'informations sur les performances des structures qui sont définies au niveau physique.

L'optimisation de performance est l'une des tâches les plus difficiles à réaliser au plus haut niveau de la conception de circuit. Les contraintes de retard sont généralement fixées par la période d'horloge maximale de fonctionnement des blocs combinatoires. Ainsi, l'optimisation du temps de propagation sur les chemins critiques constitue la condition nécessaire pour l'implantation d'un circuit rapide, de la même manière que la minimisation de la taille des portes qui n'appartiennent pas aux chemins critiques est une alternative d'assignement technologique permettant la réduction de puissance [2]. D'où la nécessité de disposer d'outils rapides et précis d'exploration de chemins [3] dans les circuits.

Les simulations intensives au niveau transistor doivent alors être remplacées par une modélisation analytique de performance, au niveau porte, qui doit être orientée conception et permettre la définition de critères de conception robustes, applicables à la synthèse de macro cellules contrôlées en vitesse et puissance. Des modèles temporels améliorés doivent être utilisés aussi bien par les outils de synthèse de placement routage que par les outils d'évaluation temporelle, et doivent prendre en compte les variations non linéaires des retards. La densité d'intégration permise par les technologies submicroniques, impose de considérer la dissipation de comme une limite réelledans la réalisation de circuits complexes. Des métriques fiables de performance doivent donc être définies afin de pouvoir comparer les évolutions des procédés de fabrication ou d'explorer les alternatives de conception faible puissance par variation des tensions d'alimentation.

Pour cela nous utilisons un outil d'analyse, d'évaluation et d'optimisation de performances (POPS: Performance Optimization by Path Selection). Cet outil permet :

- l'analyse et l'énumération de chemins classés par ordre de retard, puissance ou compromis retard/puissance [4,5],

- l'évaluation précise des performances de retard et de puissance du circuit, avec prise en compte différenciée des temps à la montée et à la descente, des effets submicroniques non linéaires (prise en compte des effets de rampe et de charge ...), du rang de l'entrée attaquée et des capacités réelles des différents nœuds du circuit.

- l'utilisation d'un protocole d'optimisation local basé sur un redimensionnement sélectif des éléments critiques, permettant la réduction de la complexité du problème général d'optimisation [6] à une solution locale.

L'originalité de la technique de classification incrémentale utilisée [7] est de permettre la caractérisation de chaque élément du circuit par une valeur réaliste de son retard à la montée et à la descente et des différentes composantes de puissance suivant les modélisations de retard et de puissance que nous avons développées [8,9,10]. La technique incrémentale s'appuie sur des informations calculées et extraites préalablement (post layout). Elle permet de trouver un nombre prédéfini de chemins suivant un critère de délai, de puissance ou encore un compromis délaipuissance et de les classer. De plus, la connaissance de l'état de charge de chaque noeud épermet de prendre des décisions en terme d'ajout de buffer ou de redimensionnement sur des portes spécifiques. L'idée principale est de travailler sur un nombre limité de chemins [11,12] afin d'appliquer plus facilement les différents critères d'optimisation de chemins [13].

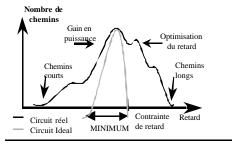

L'objectif poursuivi est **d'accélérer un circuit tout en minimisant l'augmentation de puissance correspondante** ce qui résulte en une distribution de chemins représentée sur la fig.1 en pointillés.

Fig. 1 Objectif poursuivi.

Dans une première partie, nous présentons les modèles analytiques de délai et de puissance utilisés. En effet, la précision de la recherche incrémentale de chemins dépend directement de la précision des modèles de retard et de puissance considérés. Ensuite, nous détaillerons le protocole d'optimisation de chemins, utilisé pour dimensionner certaines portes sur des chemins prédéfinis. Pour finir, nous présenterons des validations de l'outil en comparant, pour différents benchmarks (ISCAS'85),

les chemins critiques et les performances optimisées, par rapport aux valeurs obtenues à partir de standards de référence tel que Spice ou AMPS de Synopsis [14].

#### 2. Modélisation du retard et de la puissance

A cause de la complexité croissante des circuits, permise par les technologies actuelles, l'analyse des performances à toutes les étapes de la conception d'un circuit apparaît être la seule alternative de développement de circuits intégrés avec une prise en compte réaliste des contraintes de vitesse et de puissance. La seule méthode permettant de tirer profit des possibilités offertes par les technologies modernes est de disposer d'informations physiques au plus haut niveau possible de la hiérarchie de conception. Pour cela nous avons développé un macro modèle orienté conception permettant l'évaluation des performances de délai et de dissipation de puissance dans un circuit digital CMOS.

Nous prenons en compte les effets de canaux courts, et l'influence des rampes d'entrée [8,9]

Ces dernières années, la consommation de puissance a pris un intérêt important dans le domaine de la conception de circuit intégré. Trois composantes de puissance sont généralement considérées sur les structures CMOS:

- une composante dynamique, externe, due à la charge et à la décharge des différentes capacités du circuit

$$P=f.Vdd^2.\alpha C_{I}$$

,

où f représente la fréquence du signal d'entrée, C la charge physique de sortie,  $\alpha$  la probabilité de commutation du noeud de sortie et Vdd la tension d'alimentation,

- une composante dynamique, interne, appelée composante de court-circuit apparaissant pendant la mise en conduction des plans N et P et résultant en un court circuit direct entre les rails d'alimentation.

- une composante statique associée aux courants de fuite et d'injection de substrat, usuellement négligée tant que la tension d'alimentation est supèrieure au double des tensions de seuil des transistors.

Le premier terme est prépondérant et considéré dans la littérature pour les techniques de conception basse puissance [15]. Pour certaines conditions de conception, la dissipation de puissance interne peut aussi contribuer de façon significative à la dissipation dynamique, comme cela a été démontré par quelques auteurs [16]. Si la composante capacitive dynamique peut être évaluée aisément, il est plus difficile d'évaluer la composante interne étant donné sa dépendance aux conditions de conception des portes. Afin de modéliser la composante de court-circuit qui dépend fortement de la structure et des conditions de contrôle, un concept de capacité effective [10,17] a été implanté et s'est avéré suffisamment précis pour représenter cette composante. C'est ce modèle que nous avons choisi.

#### 3. Stratégie de dimensionnement des transistors

L'évaluation du retard d'un chemin repose sur un macro modèle réaliste du retard d'une porte [8,9]. Ce modèle prend en compte les capacités de couplage entrée-sortie et les effets de courant de court-circuit. Ceci permet une évaluation réaliste du retard des différents chemins sélectionnés, à partir d'une extraction post layout des différentes capacités parasites. Cette évaluation comparée aux évaluations SPICE donne une bonne précision.

L'algorithme de dimensionnement consiste à dimensionner les portes des chemins les plus longs identifiés par la technique incrémentale présentée ci-dessus. Le critère de sélection pour le dimensionnement des portes est défini par le facteur de charge d'une porte, Fc. Il a été démontré dans [13] que ce facteur est un

critère robuste représentant la charge et la force d'une porte. Ce facteur de charge est le rapport de la capacité de sortie sur la capacité d'entrée de la porte comme défini ci-dessous :

$$Fc = \frac{Cload}{Cin}$$

L'algorithme de dimensionnement est basée sur une stratégie de dimensionnement local [18] et il se déroule ainsi :

- dimensionnement initial uniforme de toutes les portes à une valeur qui peut être égale au minimum technologique, ou n'importe quelle valeur utilisée comme référence ( taille minimale permise dans une librairie standard cell, par exemple ),

- calcul du facteur de charge Fc pour chaque porte sur le chemin le plus long selectionné et comparaison de ce facteur de charge avec le facteur de charge limite caractéristique de chaque porte. [13],

- pour chaque porte, dimensionnement des portes ayant un facteur de charge plus grand que son facteur de charge limite de façon à obtenir un facteur de charge infèrieur au facteur de charge limite ( Fc < Flimit ),

- calcul du retard du chemin ainsi dimensionné à partir du retard des portes et des valeurs des paramètres MDS et BS.

Ainsi un nouveau long chemin est considéré et cette procédure est réitérée jusqu'à satisfaction de la contrainte de délai.

La contrainte de délai étant satisfaite, la consommation de puissance est limitée en mettant au minimum technologique toutes les portes des chemins courts n'appartenant pas aux chemins longs. Cette méthode permet de satisfaire une contrainte de délai sans trop consommer de puissance.

#### 4. Résultats expérimentaux

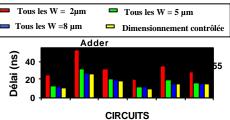

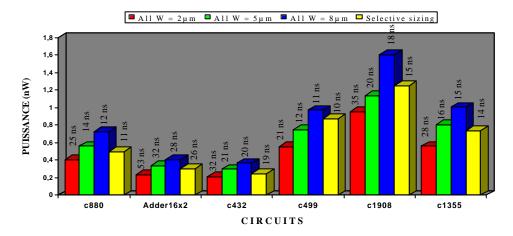

Nous avons appliqué cet algorithme sur des circuits ISCAS'85. L'histogramme de la figure 2 représente, pour différents circuits ISCAS'85, le retard du chemin le plus long pour différentes alternatives de dimensionnement : régulier ou contrôlé par l'algorithme de

dimensionnement.

**Fig. 2** Evolution du retard du chemin le plus long (ns) sur des c ISCAS'85 pour différents dimensionnements.

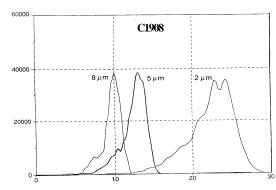

dimensionnement contrôlé est sélectif : ne sont redimensionnées que les portes ayant des nœuds de sortie trop chargés. Comme nous pouvons le voir sur la figure 2, la solution contrôlée est plus rapide que la solution régulière. Ceci est une conséquence directe du dimensionnement d'un nombre limité de portes. On peut noter que l'ensemble de ces dimensionnements contrôlés ont été effectués en des temps CPU raisonnables. Par exemple, pour le C1908, l'évaluation et la classification de ses 730000 chemins ont été effectués en 169 s de temps CPU sur Ultra Sparc 20. Un exemple d'illustration est donné par la figure 3. Nous comparons, pour le circuit C1908, ( 1075 portes et environ 730 000 chemins ) la distribution de retard sur ses chemins, pour des implantations régulières (tous les transistors taillés à 2µm, 5µm ou 8µm) (Ecpd07, ATMEL-ES2 0.25µm process). Nous remarquons le décalage des courbes vers la gauche au fur et à mesure de l'augmentation de la largeur des transistors. La courbe avec la taille de transistor la plus grande se trouve le plus à gauche et la distribution est de plus en plus resserrée : en effet l'écart de délai entre les chemins courts et les chemins longs se réduit. Nous observons donc sur ces courbes une accélération du retard quand W augmente, c'est à dire au détriment de la puissance au 1<sup>er</sup> ordre. Ceci est le résultat du dimensionnement global à l'aveugle.

#### Nombre de chemins

#### Retard

**Fig. 3** Comparaison du profil du retard pour différentes alternatives de dimensionnement régulier sur le circuit C1908.

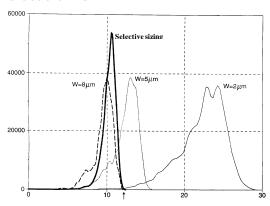

Sur la Fig.4, nous comparons les profils de délai obtenus pour le même circuit, pour un dimensionnement régulier et le dimensionnement contrôlé, c'est à dire après application du protocole de dimensionnement.

#### Nombre de chemins

#### Retard

**Fig.4** Comparaison des profils du retard sur le circuit C1908 pour deux alternatives : dimensionnement régulier et dimensionnement contrôlé.

Sur cet exemple de plus de 730 000 chemins, l'application des techniques de dimensionnement sélectif [11] pour contrôler le fan out des portes n'a affecté que 25 chemins. Il en résulte une amélioration du retard de 58% par rapport à la solution initiale à 2μm; le prix à payer étant une augmentation de la consommation de puissance dynamique de 30% (Fig. 5). Par comparaison avec la solution régulière à 8µm, la solution contrôlée admet une dispersion de retard moindre. Elle constitue donc une solution pour une implantation basse puissance. Ce résultat est illustré sur la figure 5 où nous comparons l'évolution de la puissance dissipée pour différents circuits avec les différentes alternatives de dimensionnement. La consommation de puissance a été évaluée au 1<sup>er</sup> ordre en considérant la capacité commutée totale du circuit. Nous constatons que les améliorations de retard ont été obtenues en limitant le perte en puissance. Notons aussi que le contrôle des facteurs de charge minimise la composante de court-circuit [16]. Les résultats obtenus pour la solution à

dimensionnement sélectif peuvent être encore améliorés par l'utilisation d'un modèle plus précis de la puissance.

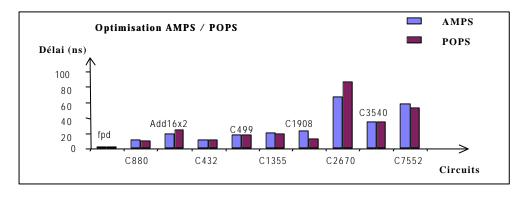

# 5. Comparaison du prototype POPS avec un outil d'optimisation de Synopsis

Nous présentons des validations pour une optimisation postlayout en délai (c'est à dire une amélioration du retard tout en limitant l'augmentation de puissance et en considérant les capacités parasites sur chaque nœud du circuit). Pour cela, nous comparons sur différents circuits ISCAS'85, les valeurs du retard des chemins les plus longs optimisés avec AMPS [14], outil d'optimisation de Synopsis, et POPS. Pour chaque outil, nous comparons aussi, sur le même chemin, le nombre de portes redimensionnées, le facteur de charge des portes dites critiques, le tout constituant une documentation intéressante sur le circuit étudié.

L'outil AMPS est l'outil industriel de base pour la recherche de chemins et l'optimisation de ces chemins. Le délai est calculé par la méthode des tables avec l'outil Synopsis TimeMill [14] intégré dans AMPS. Afin de travailler sur le même long chemin, le chemin le plus long sur lequel va être effectuée la comparaison, est déterminé par PathMill [14], outil de recherche de chemins de Synopsis intégré dans AMPS. Cet outil génère le speudo vecteur nécessaire pour la simulation électrique avec SPICE. Ensuite, nous vérifions que POPS extrait le même long chemin.

Nous comparons alors les valeurs du délai après optimisation avec AMPS et POPS. Les résultats sont représentés sur la figure 6.

Comme nous pouvons le constater sur cette figure, la précision de POPS est comparable à celle d'un outil industriel. Le coté intéressant de POPS est l'utilisation pour l'évaluation du retard et de la puissance, de modèles explicites représentant la réalité physique du circuit et prenant en compte les spécifications du fondeur.

#### 6. Conclusion

En conclusion, ces résultats montrent l'intérêt d'associer une méthode de dimensionnement sélectif à la classification de chemins avec la technique incrémentale. Le contrôle du nombre de chemins à étudier et du nombre de portes à dimensionner apportent à cette technique un avantage important par rapport aux autres techniques de parcours de graphe. Le gain obtenu en allocation mémoire et en temps CPU permet de traiter des circuits plus importants. L'utilisation de modèles réalistes pour le retard et la puissance combinés à l'exploitation d'algorithme d'optimisation locaux a contribué largement à la précision et à la rapidité du prototype réalisé.

L'application illustrée sur le C1908 montre l'avantage de contrôler le nombre de chemins pour l'optimisation du circuit. La comparaison avec des méthodes de dimensionnement régulier montre que même si les contraintes de délai peuvent être aussi atteintes avec une solution régulière, le dimensionnement local sur des portes spécifiques permet de consommer moins de puissance que les autres méthodes. Le dimensionnement de seulement 25 chemins sur les 730000 que compte le circuit C1908, montre l'importance pour cette technique d'optimisation de chemins de contrôler des paramètres spécifiques tels que le facteur de charge et le facteur de charge limite caractéristiques d'une porte. L'implantation de ces techniques dans le protoptype POPS a donné des résultats plus que satisfaisants lors de la comparaison avec un outil industriel de Synopsis.

POPS représente donc une solution intéressante pour l'optimisation de chemins, orientée conception, ceci à partir d'une estimation post layout des facteurs de charge des portes du circuit.

#### **Bibliographie**

- [1] D. Singh, J. Rabaey, M. Pedram, F. Catthoor, S. Rajgopal, N. Sehgal, T. Mozdzen, "Power Conscious CAD tools and Methodologies: a Perspective", Proc. IEEE, vol.83, n°4, pp.570-593, April 95.

- [2] M. Borah, R.M. Owens, M.J. Irwin,"Transistor sizing for minimizing Power consumption of CMOS circuits under Delay Constraint", ISLPD'95 Symposium Proceedings, pp.167-172

- [3] H.C. Chen, D.H.C. Du and L.R. Liu, "Critical Path Selection for Performance Optimization", IEEE trans. On CAD of Integrated Circuits and Systems, vol. 12, n°2, pp. 185-195, February 1995

- [4] J. Benkoski, E.V. Meersch, L. Claesen and H. De Man, "Efficient Algorithms for Solving the False Path Problem in Timing Verification", IEEE Int. Conf. on CAD, pp. 44-47, June 1987.

- [5] P.C. McGeer and R.K. Brayton, "Efficient Algorithms for Computing the Longest Viable Path in a Combinational Network", DAC, pp. 561-567, June 1989

- [6] W. Chuang, S.S.Sapatnekar, I.N.Hajj, "Timing and area optimization for standard cell VLSI circuit design", IEEE trans. On CAD of I.C. and Systems, vol. 14, n°3, pp.308-320, march 1995.

- [7] Yun-Chen Ju, R.A. Saleh, "Incremental techniques for the identification of statically sensitizable critical paths", Proc. 28<sup>th</sup> Design Automation Conf., pp.541-546, 1991.

- [8] J.M.Daga, D.Auvergne "Signal transition modeling in submicronic CMOS structures" Patmos 97, pp.259-268, Louvain la Neuve 8-10 September 1997

- [9] J.M. Daga, D.Auvergne "A comprehensive delay macromodeling for submicron CMOS logics" IEEE J. of Solid state Circuits, IEEE trans. on CAD of Integrated Circuits and Systems, vol. 34, n°1, pp. 42-55, January 1999.

- [10] S.Turgis, D. Auvergne, "A Novel Macromodel for power estimation in CMOS structures", IEEE trans. on CAD vol. 17, n°11, pp. 1090-1098, November 1998.

- [11] S. Yen, D. Du and S. Ghanta, "Efficient Algorithms for Extracting the k Most Critical Paths in Timing Analysis", Design Automation Conference, pp. 649-654, June 1989.

- [12] S. Crémoux, N. Azémard, D. Auvergne "Path resizing based on incremental technique", Proc. ISCAS, USA, 1998.

- [13] S. Turgis, N. Azemard, D. Auvergne, "Design and selection of buffers for minimum power-delay product", ED&TC, pp.224-228, Paris, March 1996.

- [14] AMPS & PathMill 5.1 User Guide, Epic Inc.,1997.

- [15] A.P. Chandrasakan, S.Sheng, R.W. Brodersen: «Low power CMOS digital design », IEEE J. Solid State Circuits, vol. 27, pp. 473-484, april 1992.

- [16] H.J.M. Veendrick: « Short circuit power dissipation of static CMOS circuitry and its impact on the design of buffer circuits », IEEEJ. Solid State Circuits, vol SC-19, pp. 468-473, aug.1984.

- [17] S.Turgis, J.M. Daga, J.M. Portal, D.Auvergne "Internal power modelling and minimization in CMOS inverters" ED&TC 97 pp603-609.

- [18] D. Auvergne, N. Azemard, V. Bonzom, D. Deschacht, M. Robert, "Formal Sizing Rules of CMOS Circuits", EDAC, pp.96-100, Amsterdam, The Netherlands, February 1991.

Fig. 5 Comparaison de la puissance consommée (nW) estimée pour différentes alternatives de dimensionnemnt, (le délai (ns) sur le chemin est donné au sommet des barres verticales).

Fig. 6. Comparaison POPS/AMPS.