## Rétine vidéo rapide réalisée en technologie CMOS

Benaïssa Bellach, Olivier Aubreton, Bernard Lamalle, Lfc. Lew Yan Voon, Guy Cathébras, Patrick Gorria

### ▶ To cite this version:

Benaïssa Bellach, Olivier Aubreton, Bernard Lamalle, Lfc. Lew Yan Voon, Guy Cathébras, et al.. Rétine vidéo rapide réalisée en technologie CMOS. JNRDM 2002 - 5ièmes Journées Nationales du Réseau Doctoral de Microélectronique, Apr 2002, Paris, France. lirmm-00269430

# HAL Id: lirmm-00269430 https://hal-lirmm.ccsd.cnrs.fr/lirmm-00269430v1

Submitted on 3 Apr 2008

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Rétine vidéo rapide réalisé en technologie CMOS

B.Bellach, O.Aubreton, B.Lamalle, L.F.C. Lew Yan Voon, P.Gorria LE2I 12, rue de la fonderie 71200 Le Ceusot G.Cathebras LIRMM 161, rue Ada 34392 Montpellier Cedex 5

E-mail: b.bellach@iutlecreusot.u-bourgogne.fr

#### Résumé

Nous présentons une rétine réalisée en technologie CMOS 0.6 µm dédiée à l'observation de phénomènes lumineux rapides. Le pixel que nous avons conçu est basé sur un principe de modulation de la durée d'une impulsion représentative du flux lumineux incident. Ce pixel a été validé par simulation SPICE grâce aux bibliothèques AMS du fondeur puis dessiné en fullcustom de façon à optimiser sa surface, on a obtenu ainsi un pixel dont la dimension est de 49.2µm de coté avec un taux de remplissage de 18 %.

#### 1. Introduction

Avec le développement des technologies VLSI, on note depuis 5 ans un regain d'intérêt pour les capteurs CMOS. L'intégration de processeurs élémentaires au niveau du pixel, la possibilité de rendre les photo-sites accessibles indépendamment les uns des autres, la rapidité et la facilité de mise en œuvre sont les principaux atouts des rétines CMOS sur les capteurs CCD. Le gain de place apporté par les nouvelles technologies de semi-conducteurs a permis d'intégrer d'avantage de transistors au niveau de chaque pixel. Les capteurs CMOS les plus répandus utilisent une structure de pixel appelée APS pour « Active Pixel Sensor » qui consiste à amplifier le signal capté sur la cellule photosensible. Cette amplification apporte une grande souplesse pour la lecture du signal mais elle génère également un bruit spatial supplémentaire appelé « fixed pattern noise » dû à la disparité des gains qui apparaissent au moment de la réalisation de ces amplificateurs. Ces capteurs dominent le marché actuel des imageurs CMOS et leur structure souffre beaucoup d'un faible taux de lecture de l'image. En effet l'adressage de chaque pixel et la conversion analogique-numérique qui lui succède ralentit énormément la lecture complète de l'image. Par conséquent les capteurs CMOS les plus performants se limitent à des fréquences d'acquisition de l'ordre de milliers images/seconde. Pour palier à cette limitation incontestable, nous présentons ici un prototype de capteur vidéo rapide innovant réalisé en technologie CMOS avec une résolution de 64 par 64 pixels et destiné à l'observation de phénomènes lumineux rapides. Dans ce

papier nous allons, tout d'abord décrire le principe de modulation de la durée d'impulsion qui est à la base de la conception du pixel avant d'étudier l'architecture complète de ce circuit.

#### 2. Modulation de durée d'impulsion

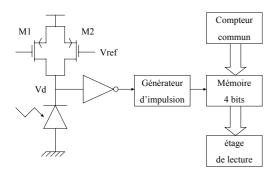

L'originalité de ce capteur provient de la façon de coder l'information. Dans notre approche, le signal lumineux, une fois converti sous forme de tension, est codé dans le domaine temporel. Le pixel est constitué de 4 étages: une photodiode qui convertit le flux lumineux en un signal électrique, un inverseur logique, un générateur d'impulsion et une mémoire 4 bits (fig.1). En première approximation, nous pouvons considérer la diode, polarisée en inverse, comme un condensateur. Lorsqu'elle est éclairé, la photodiode fournit un courant inverse proportionnel au flux lumineux incident. Le condensateur se déchargera donc d'autant plus rapidement que le flux lumineux et grand.

Dans un premier temps, on précharge la capacité de la diode par la mise en conduction du transistor M1 (fig.1). Dans l'étape suivante, on bloque le transistor M1 et on déclenche simultanément un compteur commun à toute la matrice. Le photosite est alors isolé et l'éclairement qu'il reçoit fait décroître la tension Vd. Arrivée au seuil de l'inverseur, cette tension provoque le changement d'état de celui ci. Ce basculement déclenche une impulsion permettant de mémoriser dans la mémoire la valeur fournie par le compteur. La décroissance de la tension d'un pixel fortement éclairé sera plus importante que celle d'un pixel faiblement éclairé et donc la valeur mémorisée sera plus faible dans un cas que dans l'autre. On code ainsi numériquement l'information lumineuse reçue par le pixel.

Finalement nous obtenons une image codée sur 16 niveaux de gris où chaque niveau de gris correspond à l'instant de basculement du pixel. L'ensemble des informations caractéristiques du phénomène observé (vitesse et trajectoire) est contenu dans une seule image. Le fonctionnement de ce circuit peut être assimilé à un découpage de l'image en une séquence de 16 images dont le temps d'exposition est entièrement géré par l'utilisateur grâce à une horloge externe. La fréquence de cette horloge se situe dans une large gamme et peut aller de quelque Hz à quelque dizaine de MHz, son choix est directement lié aux

caractéristiques temporelles et lumineuses du phénomène observé.

L'aspect vidéo rapide vient du fait qu'il est possible de mémoriser la trajectoire d'un objet lumineux se déplaçant à très haute vitesse par la prise d'une rafale de 16 images. En effet le déplacement du point lumineux projeté sur la matrice provoque le basculement de l'état des pixels les uns après les autres et chaque pixel mémorise ainsi l'instant de son basculement dans la mémoire SRAM.

Figure 1. Synoptique du pixel

#### 3. Architecture du circuit

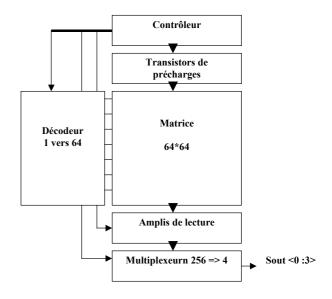

Nous venons d'étudier la mémorisation d' une donnée numérique provenant d'un compteur synchronisé avec le début d'acquisition de l'image. L'architecture complète de ce circuit est donnée figure 2. Nous avons remplacé le compteur par un contrôleur afin de permettre une grande souplesse d'utilisation du capteur. Il s'agit en fait d'une machine de Moore synchrone d'une horloge externe. Cette machine d'état a été décrite à l'aide d'un langage de programmation de haut niveau (VHDL) puis synthétisée à l'aide de logiciel de CAO. Ce contrôleur gère tous les modes de fonctionnement du circuit comme la lecture, l'écriture et l'acquisition de l'image. L'accès à la matrice se fait par l'intermédiaire d'un réseau de transistors de précharge destiné à « bufferiser » les signaux de contrôle, il permet également d'offrir plusieurs configurations d'accès à la matrice. Un dispositif de lecture (Ampli de Lecture) est directement connecté aux colonnes de la matrice et permet de lire les informations binaires. Les circuits annexes sont implantés autour d'une matrice 64\*64 pixels. L'image est codée sur 4 bits d'information par pixels et finalement on obtient une image de 2 ko. Dans le but de faciliter la réalisation et de réduire le nombre d'interconnexions, notre choix du mode d'adressage s'est porté sur un adressage lignes puis colonnes. La taille finale du circuit et de 4 par 3.8mm avec une surface utile matrice utile de 3.2 par 3.2mm, le taux de remplissage du pixel (rapport surface photosensible par la surface total du circuit) et de 18 %.

Figure 2. Architecture du circuit

#### 4. Conclusions

Nous avons présenté ici un capteur destiné à la vidéo rapide. L'information est codée sous forme d'une durée d'impulsion dont la valeur est numérisée par un compteur puis placée dans une mémoire de type SRAM. Les premiers tests réalisés confirment les résultats des simulations. Il nous reste à utiliser ce circuit dans le but d'observer l'évolution du gradient de température sur une pièce métallurgique au cours d'un soudage laser.

#### Références

- [1] A. Moini, "Vision Chips", Kluwer Academic Publishers, 2000, ISBN: 0-7923-8664-7.

- [2] P. Gorria, B. Lamalle et G. Cathebras, "Dispositif d'intercorrélation d'une image", Brevet N°99 00008, déposée le 4 janvier1999 auprès du Cabinet Claude Guiu : Dijon.

- [3] P.F.Pugibet "Réalisation d'un capteur vidéo rapide en technologie CMOS" Rapport de stage de DEA (1997), laboratoire LIRMM, université de Montpellier, laboratoire LE2I, université de Bourgogne