# Impact de la variabilité des caractéristiques temporelles des cellules combinatoires et séquentielles sur un opérateur numérique

Bettina Rebaud, Marc Belleville, Christian Bernard, Zeqin Wu, Michel Robert, Philippe Maurine, Nadine Azemard

#### ▶ To cite this version:

Bettina Rebaud, Marc Belleville, Christian Bernard, Zeqin Wu, Michel Robert, et al.. Impact de la variabilité des caractéristiques temporelles des cellules combinatoires et séquentielles sur un opérateur numérique. FTFC: Faible Tension - Faible Consommation, May 2008, Louvain-La-Neuve, Belgique. lirmm-00283731

### HAL Id: lirmm-00283731 https://hal-lirmm.ccsd.cnrs.fr/lirmm-00283731

Submitted on 30 May 2008

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Impact de la variabilité des caractéristiques temporelles des cellules combinatoires et séquentielles sur un opérateur numérique

B. Rebaud, M. Belleville, C. Bernard, Z. Wu, M. Robert, P. Maurine, N. Azemard,

Résumé— L'un des principaux intérêts de la diminution des dimensions du transistor est l'augmentation du rendement. Mais aujourd'hui, avec les technologies nanométriques, cette réduction s'accompagne d'un impact croissant des variations du processus de fabrication sur les circuits, pouvant dès lors faire chuter ce même rendement avec des spécifications non tenues. Au niveau temporel, on peut ramener ces effets à une probabilité plus élevée de violations des temps de maintien et d'établissement sur les bascules. Comme principale réponse face à ce problème, les marges de sécurité sont constamment augmentées, induisant un pessimisme excessif et ne permettant pas d'optimisation efficace.

Cet article propose une méthodologie d'étude plus réaliste basée sur le concept d'analyse temporelle statique et statistique (SSTA) et de calcul de probabilités de violation. Les résultats obtenus sur un opérateur arithmétique en technologie 65 nm permettent de mettre en exergue les limitations des techniques actuelles, la nécessité d'adopter d'autres méthodes et le bénéfice de l'utilisation d'outils statistiques pour les technologies futures.

Mots clés—Variabilité de processus de fabrication, Analyse temporelle statique et statistique SSTA, Temps de maintien, Temps d'établissement.

#### I. INTRODUCTION

vec la diminution constante des dimensions du transistor intégré, nous sommes rentrés dans l'ère nanométrique. Malgré de meilleures performances apparentes en vitesse et en consommation, et un rendement du nombre de puces par plaque augmenté, les bénéfices escomptés sont limités par plusieurs éléments [1]: de nouveaux effets physiques, amplifiés par la tendance basse consommation des systèmes embarqués, une difficulté croissante dans la mise en œuvre de procédés de fabrication et une augmentation de la sensibilité vis à vis des variations.

Manuscript reçu le 25 Avril. Ces travaux ont été réalisés dans le cadre d'un contrat entre le CEA LETI et le LIRMM, Univ. Montpellier 2, CNRS.

- B. Rebaud, M. Belleville et C. Bernard travaillent au CEA LETI MINATEC, 17 rue des Martyrs, 38054, Grenoble, Cedex 9, France. (e-mails: bettina.rebaud@cea.fr, marc.belleville@cea.fr, christian.bernard@cea.fr)

- Z. Wu, M. Robert, P. Maurine, N. Azemard travaillent au LIRMM, Univ. Montpellier 2, CNRS, 161 rue Ada, 34392, Montpellier, France. (e-mails: zeqin.wu@lirmm.fr, michel.robert@lirmm.fr, pmaurine@lirmm.fr, nadine.azemard@lirmm.fr)

Cet article se préoccupe des variations du processus de fabrication dans les circuits numériques.

Au niveau temporel, leurs effets peuvent se ramener à l'étude des violations des temps de maintien et d'établissement sur les bascules, violations provenant des variations des divers temps de propagation sur un chemin de portes logiques. Ces types de violations ont un impact direct sur la fonctionnalité et les performances d'un circuit. D'autres études sur ces variations et leur impact [2][3] ont déjà été faites, mais à des niveaux différents de celui décrit ici (niveau physique, architecture globale). L'étude des probabilités de violation est donc judicieuse puisqu'elle souligne les problèmes de variations de processus de fabrication tout en mettant en évidence les défauts et limitations des outils de CAO actuels.

Il est présenté ici une méthodologie d'étude des violations des temps de maintien et d'établissement dans les bascules, dues aux variations de processus de fabrication. Elle est basée sur des analyses temporelles statistiques (SSTA) [4][5] couplées à des données provenant de simulations Monte Carlo.

La partie qui suit explique plus en détails les problèmes de variations, la définition des temps de maintien et d'établissement, et les bases du concept de la SSTA. La partie III explicite la méthodologie appliquée. La partie IV donne les principaux résultats de cette étude, obtenus sur un opérateur arithmétique. Enfin, l'article est résumé brièvement dans la conclusion.

#### II. PRELIMINAIRES

#### A. Le problème de la variabilité

La variabilité recouvre un ensemble de notions très hétérogènes [1][6]. Elles peuvent être classifiées selon plusieurs points de vue et champs d'application. Pour résumer, les taxinomies les plus courantes sont :

- Spatial ou Temporel

- Systématique ou Aléatoire

- Global ou Local

- Physique ou Environnemental

Les variations des processus de fabrication qui nous intéressent touchent tous les aspects de variabilité cités cidessus. Les fondeurs fournissent généralement un certain

nombre de données statistiques concernant les paramètres de leurs technologies, mais actuellement, elles sont peu utilisées en conception numérique. Avec les nouvelles technologies, et des variations de plus en plus grandes, les concepteurs ont tout intérêt à intégrer ces données le plus tôt possible dans le flot de conception pour pouvoir prévenir tout risque de disfonctionnement.

#### B. Définition des temps d'établissement et de maintien

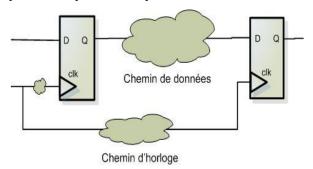

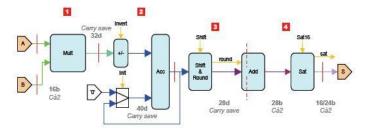

Lors d'une analyse temporelle statique typique, les violations de temps d'établissement et de maintien sont vérifiées pour voir si le circuit satisfait aux contraintes données. Le temps d'établissement correspond au temps de stabilité minimum de la donnée avant le front d'horloge pour qu'elle soit bien prise en compte. Le temps de maintien, quant à lui, est le temps de stabilité minimum après le front d'horloge (fig. 1).

La variabilité croissant, la méthode des « corners » (pire ou meilleurs cas en processus de fabrication, température et alimentation), permettant de vérifier les temps d'établissement sur les chemins longs et les temps de maintien sur les chemins courts, n'est plus assez efficace pour fournir des résultats pertinents. En effet, afin de continuer à garantir un rendement équivalent aux anciennes technologies, les marges prises sont de plus en plus pessimistes et ne permettent donc pas d'optimiser les caractéristiques d'un circuit. Une analyse temporelle statique et statistique s'avère alors nécessaire.

Fig. 1. Illustration des temps d'établissement et de maintien respectés sur un chemin logique.

#### C. Analyse temporelle statique et statistique (SSTA)

Ce concept s'appuie sur la propagation des fonctions de distribution des temps de propagation plutôt que des valeurs extrêmes à travers un chemin logique [4][5]. Le type de résultat obtenu est le même que celui découlant d'une simulation Monte Carlo (MC) à tirages aléatoires sur les paramètres du processus de fabrication. Son principal intérêt est sa rapidité d'exécution, au détriment d'une précision moins

élevée. Cependant, cette analyse reste beaucoup plus lente qu'une analyse corner pour un même jeu de chemins, car elle doit prendre en compte plus de paramètres. Des étapes préliminaires supplémentaires comme la caractérisation des cellules de bibliothèque selon des critères statistiques sont également nécessaires. En bref, cette méthodologie s'avèrera de plus en plus indispensable dans le futur pour obtenir des données statistiques sur tout un circuit, chose impossible à réaliser en MC compte tenu du nombre de plus en plus élevé de chemins à analyser.

#### III. METHODOLOGIE PROPOSEE

Cette partie explique la méthodologie utilisée ici pour étudier statistiquement des chemins de portes logiques.

#### A. Généralités

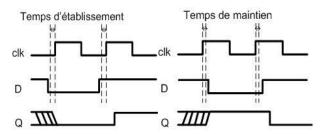

La méthode décrite dans cet article s'insère dans le flot de conception connu d'un circuit numérique. Il s'agit d'une analyse statistique supplémentaire au flot usuel dont les outils pourraient bénéficier en vues d'optimisations. Cette méthodologie nécessite de sélectionner un certain nombre de chemins caractéristiques du circuit ou bloc étudié et d'en sortir des informations de distribution des temps de propagation et de transition.

Fig. 2. Description du flot utilisé pour analyser statistiquement des chemins logiques.

Pour cela, l'application de la SSTA sur le chemin de portes logiques sélectionné et sur son chemin d'horloge associé, est effectuée. Puis, le couplage des informations sortantes avec les caractéristiques intrinsèques de la bascule de fin de chaîne permet d'obtenir facilement la probabilité de violation voulue (maintien pour chemins courts et établissement pour chemins longs). Un schéma récapitulatif est donné figure 2.

Pour le bon fonctionnement de cette méthodologie, il faut également procéder à un certain nombre de caractérisations statistiques, étapes préliminaires dont les résultats seront ensuite utilisés dans le flot sous forme de tables à deux entrées. Le bloc de calcul des probabilités de violation utilise l'équation (1).

$$Pv_{E} = \Pr(T - d_{donn\acute{e}s} + d_{hort} < TE_{bascule})$$

$$Pv_{M} = \Pr(d_{donn\acute{e}s} - d_{hort} < TM_{bascule})$$

(1)

avec Pv la probabilité de violation, T la période, d les distributions des délais du chemin de données ou d'horloge, TE et TM, respectivement les distributions des temps d'établissement et de maintien dans le cas étudié. En utilisant l'hypothèse de distributions gaussiennes, les calculs de probabilité se simplifient énormément.

Les deux sous-parties suivantes détaillent les étapes de calcul et de caractérisation.

#### B. Description du SSTA implémenté

La mise en place de notre technique SSTA s'appuie sur les travaux de [5], basés sur l'étude de chemins de façon indépendante. Elle se décompose en deux étapes : la caractérisation des cellules logiques selon la capacité de sortie et la transition d'entrée, et le calcul de distributions temporelles. La caractérisation permet d'avoir la moyenne et la déviation standard des temps de propagation et de transition avec les variations de processus de fabrication. Pour cela, des simulations MC sont appliquées. Les données obtenues sont stockées dans des tables. Il est à noter que la précision des résultats finaux obtenus dépend fortement de la manière dont s'effectue cette étape. Le calcul des temps, quant à lui, se fait grâce à la discrétisation des distributions gaussiennes en entrée de porte en n points, pondérés par leur probabilité. Nous avons pris n = 6 qui constitue un bon compromis temps de simulation/précision. Chaque point discrétisé renvoie à la lecture de tables pour connaître les moyennes et déviations standards associées. Ainsi, le délai et le temps de transition de sortie d'une porte sont donnés par les équations (2).

$$\mu_{d} = \sum_{i=1}^{n} p_{i} m_{d}(t_{i}, C_{L})$$

$$\sigma_{d}^{2} = \sum_{i=1}^{n} p_{i} (s_{d}^{2}(t_{i}, C_{L}) + [m_{d}(t_{i}, C_{L}) - \mu_{d}]^{2})$$

$$\mu_{T_{out}} = \sum_{i=1}^{n} p_{i} m_{T_{out}}(t_{i}, C_{L})$$

$$\sigma_{T_{out}}^{2} = \sum_{i=1}^{n} p_{i} (s_{T_{out}}^{2}(t_{i}, C_{L}) + [m_{T_{out}}(t_{i}, C_{L}) - \mu_{T_{out}}]^{2})$$

(2)

avec  $\mu$  la moyenne et  $\sigma$  la déviation standard. m et s sont lues dans les tables grâce à la capacité de sortie  $C_L$  et la transition d'entrée  $t_i$ , le tout pondéré par les probabilités  $p_i$  (i valant de 1 à n, n nombre d'échantillons). Les indices d et  $T_{out}$  représentent

les délais de propagation et de transition en sortie de la porte étudiée.

Pour connaître ensuite le délai du chemin entier, nous appliquons les équations (3).

$$\mu_{d_{chemin}} = \sum_{i=1}^{M} \mu_{i}$$

$$\sigma_{d_{chemin}}^{2} = \sum_{k=1}^{M} \sum_{l=1}^{M} \rho_{kl} \sigma_{k} \sigma_{l}$$

(3)

avec M le nombre total de cellules logiques du chemin,  $(\mu_j, \sigma_j)$  les caractéristiques des distributions de probabilité du délai de chaque porte, et  $\rho_{kl}$  le coefficient de corrélation linéaire du délai entre deux portes.  $\rho_{kl}$  est obtenu en propageant de nombreux échantillons de temps de transition à l'entrée du chemin et en récupérant les délais associés de chaque porte. Il suffit ensuite d'appliquer la formule connue de corrélation linéaire. Pour le temps de transition de sortie, il s'agit simplement de celui de la dernière porte.

L'erreur relative a été regardée pour des chemins allant de 1 à 30 portes logiques : on constate une erreur pouvant aller jusqu'à 7% pour la moyenne et 15% pour la déviation standard en technologie 65 nm.

#### C. Calculs des temps de maintien et d'établissement

Nous avons procédé à la caractérisation MC des temps intrinsèques de maintien et d'établissement des bascules en observant le temps de propagation Clock-to-Q tout en rapprochant le front du signal de donnée du front d'horloge. La courbe ainsi obtenue est une fonction monotone décroissante. Les temps voulus sont ensuite relevés à +10% du temps Clock-to-Q minimum obtenu pour des distances front de donnée/front d'horloge grande. Cela nous permet de remplir des tables selon les temps de transition de la donnée et de l'horloge. Ensuite, le calcul des temps pour la bascule dans un chemin précis se fait identiquement à la méthodologie SSTA, en discrétisant selon n points les distributions d'entrées et en les pondérant de leur probabilités respectives. A l'issue de cette étape, toutes les informations nécessaires sont réunies pour le calcul final de probabilité de violation : on applique les équations (1) pour trouver  $P_{ve}$  et  $P_{vm}$ . La période T dans  $P_{ve}$  est indispensable pour fixer la fréquence de fonctionnement du bloc/circuit. L'hypothèse de simplification permet de se ramener à la simple étude d'une distribution normale centrée réduite.

#### IV. RESULTATS

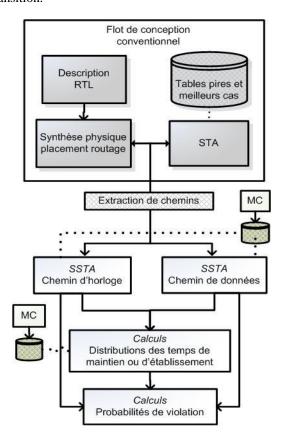

Cette méthodologie a été appliquée sur un opérateur digital (fig. 3) comprenant un étage multiplieur et un autre accumulateur. Ce type de bloc numérique est communément utilisé dans les systèmes embarqués, d'où son choix pour les simulations. Dans notre cas, il comprend deux entrées de 16 bits chacune et est pipeliné en quatre étages permettant d'accélérer la fréquence de fonctionnement. Les instructions sont elles aussi pipelinées pour parvenir au bon moment à l'étage voulu.

Fig. 3. Schéma de l'opérateur numérique implémenté.

Afin de connaître ses performances temporelles, ce bloc a été synthétisé, placé et routé en technologie 65 nanomètres. Deux types de synthèses ont été menées : l'une en technologie basse consommation en utilisant des portes à haute tension de seuil (HVT), et l'autre en utilisant un ensemble de cellules avec des tensions de seuil différentes (MVT). Cette dernière technique est très souvent utilisée pour baisser la consommation d'un bloc en remplaçant dans les chaînes non critiques des cellules à basse tension de seuil par des cellules moins coûteuses en énergie, homogénéisant dès lors les temps de propagation en rendant plus de chemins critiques. La contrainte temporelle fixée est de 2ns, facilement atteignable en MVT, mais pas en HVT (pas de violation temporelle pour une période de 3,3 ns). Les ensembles de chemins extraits de ces synthèses, placements et routages vont nous permettre d'étudier statistiquement leur comportement temporel, et ainsi de déterminer les réelles performances du bloc.

Les conditions environnementales limites prises pour les études en pire ou meilleur cas sont les couples tension-température (1.1V/125C; 1.3V/-40C). Nous nous sommes limités à regarder les chemins les plus critiques au niveau du temps de maintien et d'établissement, et non pas l'ensemble de tous les chemins du bloc. Les plus longs chemins sont principalement situés dans l'étage principal comportant le multiplieur, tandis que les plus courts correspondent à l'acheminement du contrôle.

Les résultats ci-après mettent en évidence les limites des méthodes de conception actuelles et fournissent des chiffres concernant la probabilité de violation de temps d'établissement et de temps de maintien.

#### A. Etude des cellules combinatoires

Conformément à la première étape de notre méthodologie, nous avons appliqué des SSTA pire et meilleur cas environnementaux sur les jeux de chemins sélectionnés. Cette simple analyse permet déjà de faire un certain nombre de constats. Des premiers résultats permettent de connaître la composition des chemins étudiés, la moyenne du délai de propagation et sa déviation standard (sigma). La déviation simple, calculée à 3\*sigma/moyenne (%) est un bon indicateur de la dispersion. Les marges prises par l'outil d'analyse temporelle sont également accessibles.

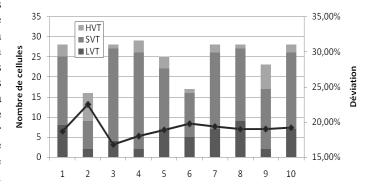

L'analyse SSTA des chemins longs (« launch clock path + data path ») est effectué en pire cas environnemental. On constate une déviation d'environ 23% pour les 10 premiers chemins de la synthèse HVT, avec une profondeur logique d'environ 17 cellules. Cette déviation est dépendante d'un

nombre important de paramètres du chemin : la complexité des cellules, le nombre de cellules, la sortance des portes contribuant à en baisser les effets. En MVT (fig. 4), la contrainte de 2 ns n'est pas assez forte pour avoir une majorité de cellules à basse tension de seuil. La déviation est ici aux alentour de 20 %, ce qui peut s'expliquer par des chemins plus longs et surtout par l'utilisation de cellules plus rapides et moins sujettes aux variations.

Concernant les chemins les plus courts (« capture clock path »), au meilleur cas environnemental, une moyenne de déviation de 22% a été calculée. Ce chiffre est valable pour les deux synthèses, sachant que, par soucis d'énergie, l'utilisation de cellules à haute tension de seuil, sur des chemins n'ayant pas besoin d'optimisation en vitesse, est systématique en MVT.

Fig. 4. Déviation (3\*sigma/mu) en pourcentage et composition des 10 premiers chemins critiques en synthèse et placement routage MVT.

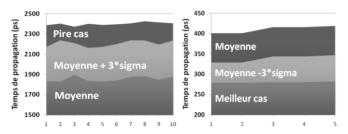

La comparaison de l'analyse de ces chemins avec les résultats donnés par les outils d'analyse temporelle (fig. 5) permettent de quantifier les marges excédentaires. On peut constater un pessimisme entre 7% et 11% sur les chemins longs par rapport à la moyenne+3\*sigma (correspondant à 99,7% des cas), et entre 18% à 23% sur les chemins courts. Une marge beaucoup plus importante est présente sur les chemins courts qui correspondent aux violations de temps de maintien. Celles-ci sont beaucoup plus critiques, car elles affectent la fonctionnalité même du bloc et non pas seulement ses performances en fréquence.

Fig. 4. Corners de conception pire et meilleur cas donnés par les outils sur les 10 premiers chemins les plus longs et les 5 chemins les plus courts, comparés aux résultats statistiques des délais de propagation. Les bandes noires représentent les marges de sécurité prises par les outils.

#### B. Temps d'établissement et temps de maintien

Grâce à la caractérisation Monte Carlo des temps de maintien et d'établissement intrinsèques aux bascules, il nous a

été possible de mettre en exergue un problème concernant l'utilisation même des pires et meilleurs cas environnementaux. En effet, outre les variations de ces temps très grandes et les marges prises encore plus élevées, les pires temps ne sont plus forcément ceux des corners usuels.

Si l'on regarde la moyenne+3\*sigma, la table I représentant les temps d'établissement d'une bascule pour plusieurs conditions environnementales, désigne le pire cas à (1,1V/-40°C); la table II pour les temps de maintien à des conditions (1,3V/125°C). De plus, ces pires conditions environnementales peuvent varier d'une bascule à l'autre. Dans ces conditions, la méthodologie actuelle des corners, trop pessimiste dans certains cas, n'est plus du tout valable ici. Le fondement même de la méthodologie serait à revoir.

TABLE I

TEMPS D'ETABLISSEMENT

| TEM OF ETHEROPENE |        |        |        |        |  |  |  |

|-------------------|--------|--------|--------|--------|--|--|--|

| Alimentation      | 1,1    |        | 1,3    |        |  |  |  |

| Température       | -40    | 125    | -40    | 125    |  |  |  |

| mu                | 125    | 105    | 61     | 67     |  |  |  |

| Sigma             | 17     | 16     | 7      | 8      |  |  |  |

| mu+3*sigma        | 176    | 153    | 82     | 91     |  |  |  |

| déviation         | 40,80% | 45,71% | 34,43% | 35,82% |  |  |  |

Caractéristiques statistiques des temps d'établissement d'une bascule selon les conditions environnementales.

TABLE II TEMPS DE MAINTIEN

| Alimentation | 1,1    |        | 1,3    |        |

|--------------|--------|--------|--------|--------|

| Température  | -40    | 125    | -40    | 125    |

| mu           | -149   | -86    | -66    | -59    |

| sigma        | 14     | 12     | 6      | 6,6    |

| mu+3*sigma   | -107   | -50    | -48    | -39,2  |

| déviation    | 28,19% | 41,86% | 27,27% | 33,56% |

Caractéristiques statistiques des temps de maintien d'une bascule selon les conditions environnementales.

Notons également que pour de mêmes conditions environnementales, les cellules à plus basse tension de seuil possèdent une déviation en temps d'établissement plus basse (45% pour HVT, 42% pour SVT, 37% pour LVT [1.1V, 125C]), mais une déviation en temps de maintien similaire (autour de 28% [1.3V,-40C]). Cela peut s'expliquer par le fait que les temps d'établissement font intervenir le délai de propagation d'un seul chemin dont la déviation dépend du type de cellules, alors que le temps de maintien concerne la concurrence entre chemins très courts de même longueur.

#### C. Probabilités de violations

La dernière étape de la méthodologie permet d'obtenir la probabilité de violation des temps de maintien et d'établissement.

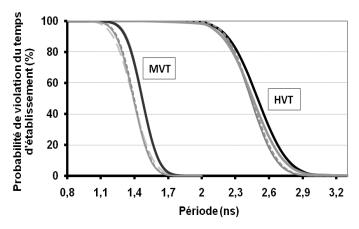

La figure 6 fournit les résultats de l'analyse de violation des temps d'établissement sur les cinq chemins considérés comme les plus critiques par l'analyse temporelle de l'outil CAO après placement-routage MVT et HVT. On peut noter que les courbes MVT sont légèrement plus pentues que les HVT, ce qui est dû aux variations plus faibles des cellules à plus basse

tension de seuil. De manière générale dans notre cas, avec des variations presque similaires sur les chemins étudiés, la classification par criticité des chemins en pire cas ou cas statistique moyenne+3 sigma reste pratiquement la même, avec des courbes parfois confondues.

Nous pouvons désormais mesurer le pessimisme final en comparant ces courbes à la fréquence maximum prédite par les outils. En prenant les pires chemins (en noir), nous pouvons estimer les périodes de fonctionnement à 1,7ns (MVT) et à 2,9ns (HVT) pour une probabilité de violation de moins de 0,5%, contre 2ns et 3,2ns données initialement. Cela permet d'optimiser le bloc d'au moins 13%.

Fig. 6. Probabilité de violation du temps d'établissement sur les cinq chemins les plus critiques de chaque synthèse (HVT, MVT).

Bien que le corner choisi pour les bascules ne corresponde pas forcément au pire temps de d'établissement, la marge prise sur le chemin de d'horloge est assez grande pour recouvrir ce temps. De plus, les calculs étant effectués avec des délais de propagation du chemin de données et d'horloge décorrélés, on peut supposer que la fréquence maximum réelle est encore plus élevée. Un avantage supplémentaire suite à l'application de cette méthode est d'obtenir une quantification exacte de la probabilité de violation pour une fréquence donnée grâce aux courbes continues obtenues. Un certain nombre de compromis peut alors être fait en toute connaissance de cause; ce qui n'est pas possible avec la méthode des corners. Ainsi, une méthodologie statistique semble indispensable pour l'étude temporelle et précise des performances d'un bloc.

TABLE III

PROBABILITE DE VIOLATION DE TEMPS DE MAINTIEN

| Conditions        | -40°C / 1,3V | 25°C/1,2V   | 125°C/1,1V |

|-------------------|--------------|-------------|------------|

| environnementales | Meilleur cas | Cas typique | Pire cas   |

| Probabilité (%)   | 0,004        | 0,12        | 0,015      |

Probabilité de violation du temps de maintien pour plusieurs cas environnementaux de hascules.

L'étude des violations des temps de maintien permet de surligner de nouveau le problème des corners de conception à choisir. La table III représente la probabilité de violation calculée sur le chemin le plus critique, en SSTA meilleur cas et pour plusieurs conditions environnementales pour le temps de maintien de la bascule, dans le cas où celle-ci est décorrélée du reste. On peut voir que c'est le cas typique qui est le plus critique, or ce corner n'est jamais vérifié par les outils.

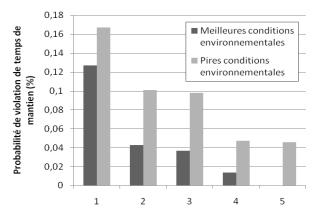

La figure 7 montre les résultats d'analyse des chemins critiques courts après placement routage. Deux types de SSTA ont été réalisées, en noir avec les conditions les plus rapides (meilleur cas) et en blanc avec les conditions les plus lentes (pire cas), le tout avec une bascule au cas typique. Contre toute attente, la probabilité de violation est plus élevée pour les cas les plus lents. Cela s'explique par le fait que le chemin d'horloge rentre en concurrence avec le chemin de données et peut parfois avoir un comportement plus critique dans des conditions plus lentes.

Fig. 7. Probabilité de violation de temps de maintien sur les 5 chemins les plus courts avec différentes analyses SSTA.

Il faut donc envisager toutes les possibilités avant de choisir un corner environnemental. Enfin, qu'en est-il si les chemins de données et d'horloge ont des conditions environnementales fortement décorrélées? Cela reste tout à fait possible avec la présence de gradient de température, de points chauds ou encore de baisses locales d'alimentation (IR drop). Ce problème est beaucoup plus visible en temps de maintien, car le chemin d'horloge et de données ont sensiblement la même profondeur logique.

#### V. CONCLUSION

Cet article présente une méthodologie d'étude statistique des violations des temps de maintien et d'établissement, avec une application concrète sur un opérateur arithmétique.

Il est démontré ici le pessimisme engendré par l'utilisation de la méthode des corners sur les cellules combinatoires, ses limites concernant les cellules séquentielles et ainsi la nécessité de repenser les méthodes et techniques de conception actuelles. Des outils statistiques sur les variations de processus de fabrication apparaissent indispensables pour obtenir des résultats fiables et optimiser la conception de circuits. L'application de notre méthodologie a démontré une optimisation en fréquence d'au moins 13% par rapport aux chiffres donnés par les outils CAO.

#### REFERENCES

- [1] S. Borkar et al. "Designing Reliable Systems from Unreliable Components: The Challenges of Transistor Variability and Degradation", IEEE, Micro, vol. 25, no. 6, pp. 10-16, Nov/Dec 2005

- [2] A. Asenov et al. "Simulation of intrinsic parameter fluctuations in decananometer and nanometer-scale MOSFETs", Electron Devices, IEEE Transactions, vol. 50, Issue 9, pp. 1837-1852, Sept 2003.

- [3] S. Borkar et al. "Parameter Variation and Impact on Circuits and Microarchitecture", Proceedings of the 40th Conference on Design Automation, Juin 2003.

- [4] Chirayu S. Amin *et al.* "Statistical static timing analysis: how simple can we get?", Proceedings of the 42th Conference on Design Automation, Juin 2005.

- [5] V. Migairou et al. "A simple statistical timing analysis flow and its application to timing margin evaluation", PATMOS'07 Conference, Sept 2007

- [6] K. Bernstein et al. "High performance CMOS variability in the 65 nm regime and beyond", IBM Journal of Research and Development, vol. 50, pp. 433-449, Juillet 2006