# Keynote intitulé "Power: The New Dimension of Test" Patrick Girard

#### ▶ To cite this version:

Patrick Girard. Keynote intitulé "Power: The New Dimension of Test". WRTLT'2008: Workshop on RTL and High Level Testing, Nov 2008, Sapporo, Japan. lirmm-00820640

#### HAL Id: lirmm-00820640 https://hal-lirmm.ccsd.cnrs.fr/lirmm-00820640

Submitted on 6 May 2013

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## WRTLT 2008 – Sapporo - Japan

## **Power: The New Dimension of Test**

Patrick GIRARD

LIRMM

University of Montpellier / CNRS

Montpellier, France

## Outline

- 1. Relevance of power during test

- 2. Main test power issues

- 3. Reducing test power by dedicated techniques

- 4. Low Power Design and its implications on test

- 5. One step to the future

## Power Consumption in CMOS

### **Switching (dynamic) Power**

- Due to charge/discharge of load capacitance during switching

- $\bullet$   $P_{DYN} \propto V_{DD}^2$  .  $F_{CLK}$

### **Leakage (static) Power**

- Power consumed when the circuit is idle

- Mainly due to sub-threshold leakage

- $\bullet$   $I_{SUB} \propto V_{DD} / V_{TH}$

# Power During Test ...

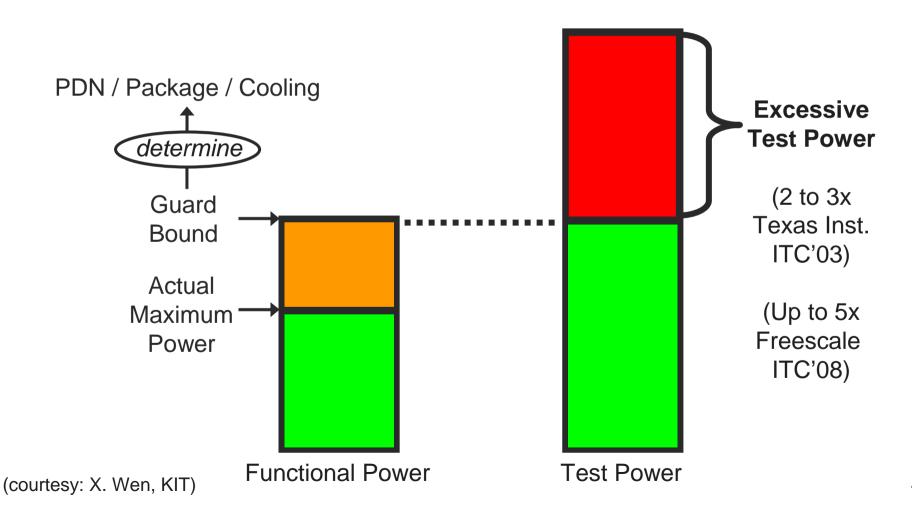

### Much higher than during functional operations

# Power During Test ...

### Main reasons for excessive test power

- No correlation between consecutive test vectors

- → Test vectors may ignore functional (especially power) constraints

- Non-functional clocking during test

- DFT (e.g. scan) circuitry intensively used

- Concurrent testing often used for test time efficiency

- Compression and compaction used for test data volume reduction

For conventional (non low-power) designs, dynamic power is the main responsible for excessive test power!!

Leakage power is a real issue during IDDQ test (reduced sensitivity) and during burn-in test (can result in thermal runaway condition and yield loss)

## Main Test Power Issues

Temperature Increase

$$T_{die} = T_{air} + \theta \times P_{Average}$$

**Excessive Heat Dissipation**

Structural degradations (hot spots)

Hot-Carrier-Induced Defects

Electro-migration

Dielectric Breakdown

**Reduced Reliability**

Low Allowable Parallelism (Wafer Testing & Package Testing)

**Low Test Throughput**

## Main Test Power Issues

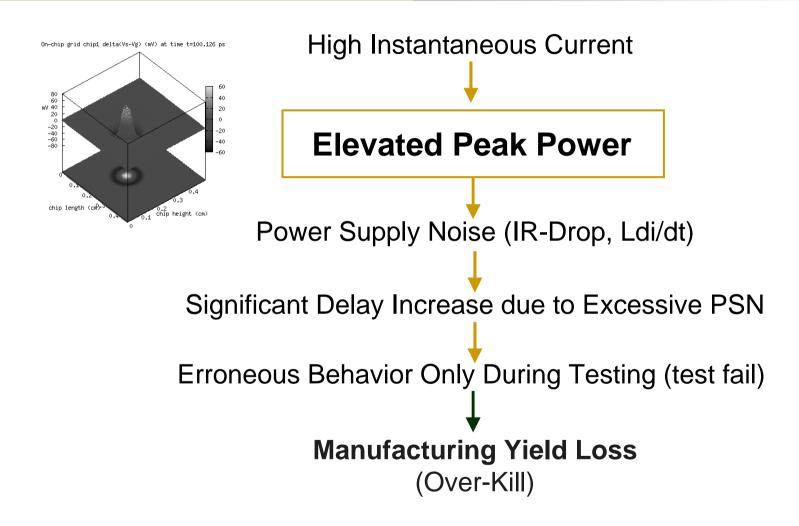

As huge designs can be manufactured today, most power-related test issues (during scan) are due to excessive peak power

# Reducing Test Power

### **Straightforward Solutions**

- Test with lower clock frequency

- Partitioning and appropriate test planning

- Over sizing packages and use of cooling equipments

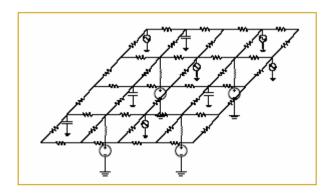

- Over sizing power distribution network (PDN)

- Grid Sizing based on functional power requirements

- all parts not active at a time

- Grid Sizing for test purpose too expensive !!

### Costly or longer test time

# Reducing Test Power

#### Main classes of dedicated solutions

- Design for Test Power Reduction

- Test Data Manipulation for Power Reduction

- Power-Aware Test Data Compression \*

- System-Level Power-Aware Test Scheduling \*

### **Objective**

#### Make test power dissipation comparable to functional power

While achieving high fault coverage, short test application time, small test data volume, low test development efforts, low area overhead, ...

<sup>\*</sup> See: P. Girard, X. Wen and N. Touba, chapter "Low Power Testing" of book "System-on-Chip Test Architectures: Nanometer Design for Testability", Morgan Kaufmann, 2007.

# Design for Test Power Reduction

### During scan testing (standard or LOC-based at-speed):

| Shift Power Reduction                                                                                                                                                                                                                                                                                                                                 | Capture Power Reduction                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Shift Impact Blocking</li> <li>blocking gate, special scan cell</li> <li>first-level power supply gating</li> <li>Scan Chain Modification</li> <li>scan cell reordering</li> <li>scan chain segmentation</li> <li>scan chain disable</li> <li>Scan Clock Manipulation</li> <li>splitting, staggering</li> <li>multi-duty clocking</li> </ul> | <ul> <li>Partial Capture</li> <li>circuit modification</li> <li>scan chain disable</li> <li>one-hot clocking</li> <li>capture-clock staggering</li> </ul> |

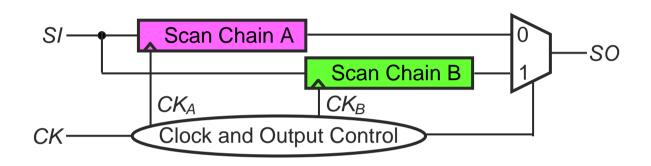

## Design for Test Power Reduction

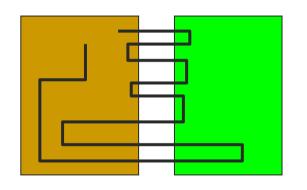

### **Example: Scan chain segmentation**

- Controllable and data-independent effect of shift power reduction.

- No change to ATPG and no increase in test application time.

# Test Data Manipulation

|                        | Shift Power Reduction                                                                | Capture Power Reduction                                                                                                                                                                                                                                            |

|------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low-Power<br>ATPG      | <ul><li>Blocking Test Generation</li><li>Low Power Compaction</li></ul>              | <ul> <li>Test Generation</li> <li>power constraint checking</li> <li>target fault restriction</li> </ul>                                                                                                                                                           |

| Low-Power<br>X-Filling | <ul> <li>X-Filling</li> <li>O-fill</li> <li>1-fill</li> <li>adjacent-fill</li> </ul> | <ul> <li>FF-Oriented X-Filling         <ul> <li>justification-based</li> <li>probability-based</li> <li>hybrid</li> </ul> </li> <li>Node-Oriented X-Filling         <ul> <li>internal-switching-activity-aware</li> <li>critical-path-aware</li> </ul> </li> </ul> |

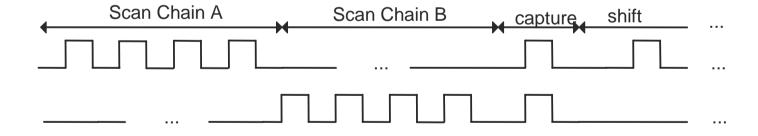

# Test Data Manipulation

### **Example: Low-Power X-filling**

- Fill to reduce power in scan cells and combinational logic

- X-filling can be used to reduce shift-in (not shift-out) power or capture power

- Can be extended to support test compression

- Very efficient!

# Evaluating ...

### ... Test Power Reduction Strategies

| <ul><li>Power reduction effectiveness</li></ul>   |         | High |

|---------------------------------------------------|---------|------|

| <ul><li>Fault coverage impact</li></ul>           | Low     |      |

| ATPG engine impact                                | Minimum |      |

| Test data volume impact                           | Low     |      |

| <ul><li>Test time impact</li></ul>                | Low     |      |

| <ul><li>Functional timing impact</li></ul>        | Low     |      |

| <ul><li>Area overhead</li></ul>                   | Low     |      |

| <ul><li>Usability with test compression</li></ul> |         | High |

| <ul><li>Design effort</li></ul>                   | Minimum |      |

| <ul><li>Design flow change</li></ul>              | Low     |      |

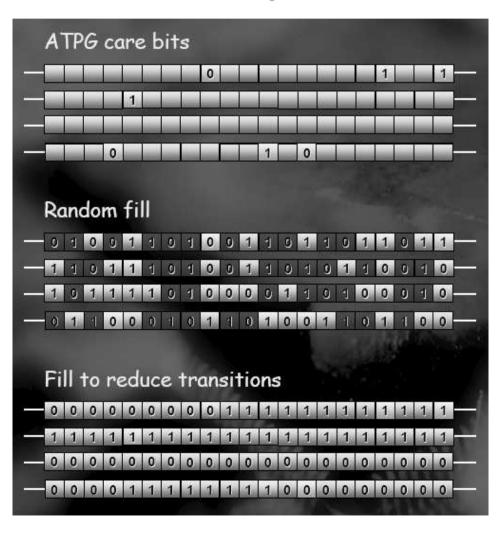

# Power During Test ...

#### **Even more critical for Low-Power Devices!!**

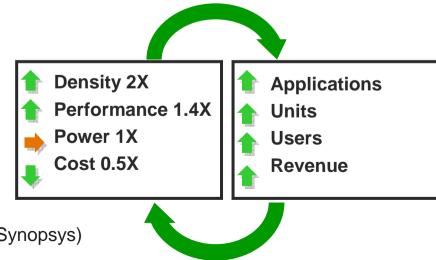

# Low Power Design (LPD)

| Main LPD techniques   | Power reduction |         |

|-----------------------|-----------------|---------|

|                       | Dynamic         | Leakage |

| Clock gating          | -               |         |

| Power gating          | -               | -       |

| Multi-Voltage domains | -               |         |

| Multi-Threshold cells |                 | -       |

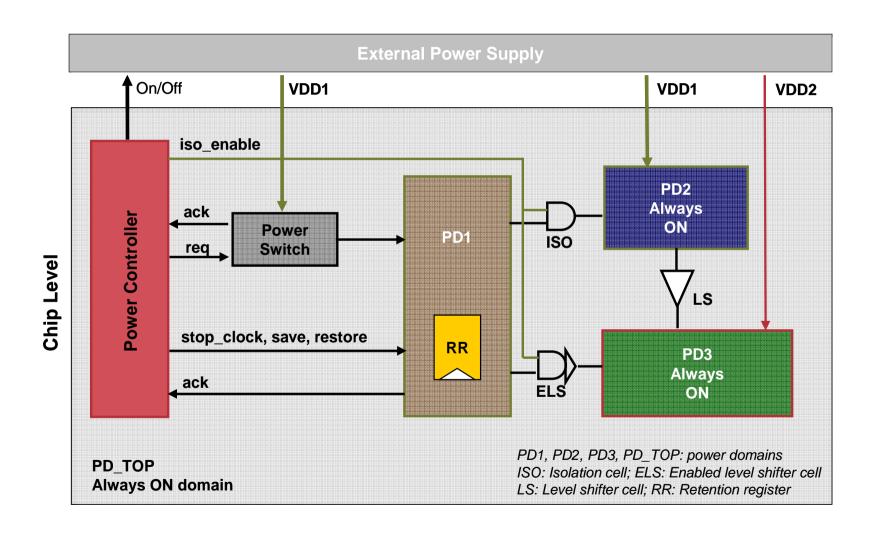

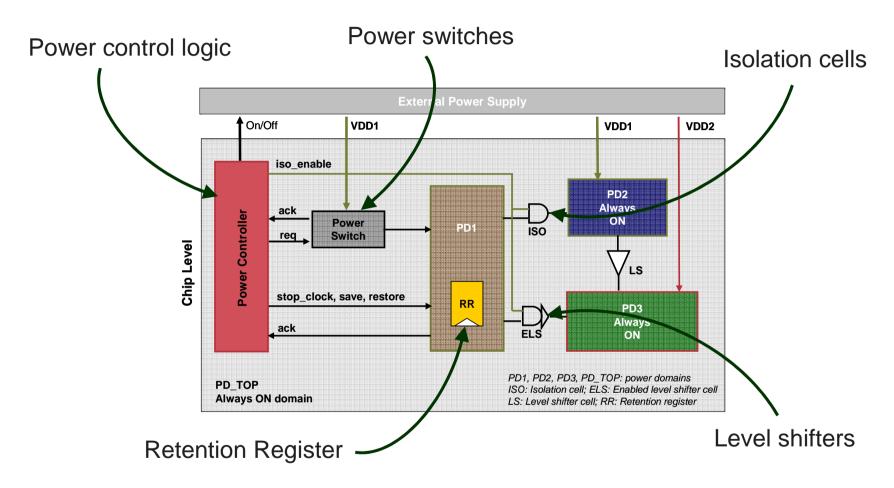

# Power Management Infrastructure

## Implications of LPD on Test

- Reduce (even more) test power by using the power management infrastructure (and/or applying the previous dedicated solutions)

- Preserve the functionality of the test infrastructure

- Test the power management (PM) structures

### And still target:

High fault coverage, short test application time, small test data volume, low area overhead, etc ... while making test power dissipation (dynamic and leakage) comparable to functional power

## Use of PM Infrastructure

Some solutions exist to reduce test power by considering the PM infrastructure ... but further developments are needed!

| Dynamic Power Reduction                                                                                                           | Leakage Power Reduction                                     |  |

|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|

| <ul> <li>Test generation for multi-voltage designs</li> </ul>                                                                     | <ul> <li>Low-power data retention<br/>scan cells</li> </ul> |  |

| <ul> <li>Test Relaxation and X-Filling for<br/>gated clock designs</li> </ul>                                                     |                                                             |  |

| <ul><li>DFT for gated clock designs</li></ul>                                                                                     |                                                             |  |

| <ul> <li>Test planning for multi-power<br/>domains architectures</li> </ul>                                                       |                                                             |  |

| <ul> <li>DfT (scan) for multi-voltage designs (power-aware scan chain<br/>construction for MSMV and PSO-aware testing)</li> </ul> |                                                             |  |

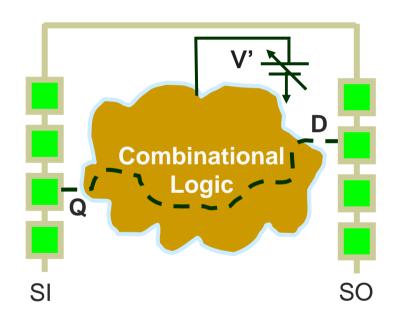

## Use of PM Infrastructure

### **Example 1: Voltage scaling in scan mode**

Scaled voltage V' in Scan Mode gives a lower shift power: (V'/V)<sup>2</sup>

- During scan shift, the combinational logic need not meet timing

- The scan shift speed is usually lower than the functional speed

Using a lower supply voltage during scan shifting to reduce dynamic and leakage power dissipation.

Done by re-using the voltage scaling infrastructure in test mode

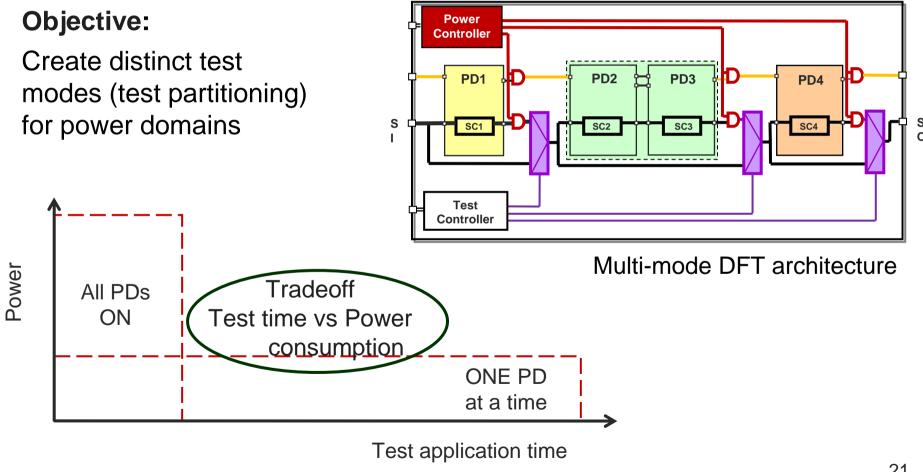

## Use of PM Infrastructure

### **Example 2: Power Domain Test Planning**

21

# Preserving Test Functionality

### Main Challenge

• Test infrastructures like scan chain or TAM may cross several power domains and can be broken if some of these domains are temporarily powered-down for low-power constraints

Specific test control strategies and extra DfT insertion are required for preserving functionality of the test infrastructure!

Similar challenges exist for clock gating designs, though some of them are comprehended today by existing test methods and tools \*

# Preserving Test Functionality

### **Example 1: MSMV-aware scan chain assembly**

• Minimize the occurrence of chains that cross voltage domains

- Avoid unwanted power down during scan shift/capture

- Chain must not span domains that must be independently on/off

- Chains traversing through powered down domains must bypass them

• ...

# Preserving Test Functionality

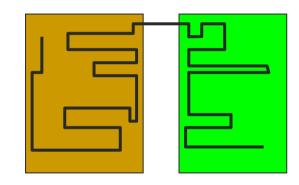

### **Example 2: Dedicated clock gating logic**

- The clock gating logic may prevent scan registers from being fully controllable for the purpose of shifting test data through them

- The proposed logic overrides the clock control signal (EN) and allows for normal operation of the scan chains when shifting test data

## Test the PM Structures

PM structures require dedicated DFT methods and ATPG patterns, and need to consider power modes!

## Test the PM Structures

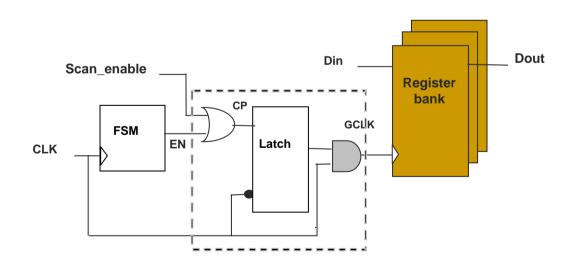

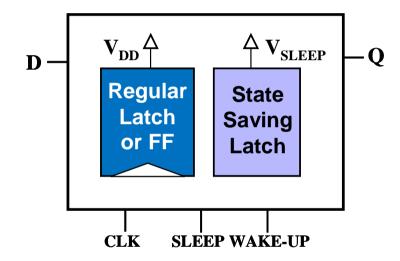

### **Example 1: State Retention Cell**

### Main test challenges:

- Retention cells are usually tested as normal FFs by test generation

- Retention capability in power down mode has to be tested

- Impact of power domain switching on retention has to be tested

- Considering only the stuck-at fault model is not enough!

## Test the PM Structures

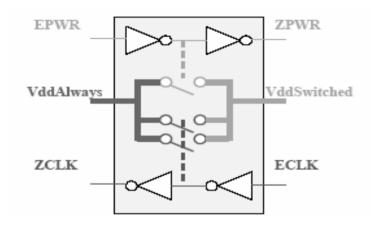

### **Example 2: Power Switch**

### Main test challenges:

- Rush current during power up → specific functional mode → test mode has to map functional mode!

- Testing micro-switches individually  $\rightarrow$  DfT needed to turn 'on' and 'off' each switch individually and allow  $R_{off}/R_{on}$  measurement

- Switches are usually daisy-chained → ensure the chain is not broken by adding control and observability to the ring control signals

## One Step to the Future

- New test solutions for Low-Power Design using the PM infrastructure and preserving the test functionality will be needed

- New test solutions for PM structures will also be needed

### Main accompanying challenges:

- High quality delay fault coverage will be mandatory !!

- Test power estimation needs improvements!

### Test conditions may be influenced by LPD:

Testing at only high T° for Fmax will be insufficient

# Delay Fault Coverage

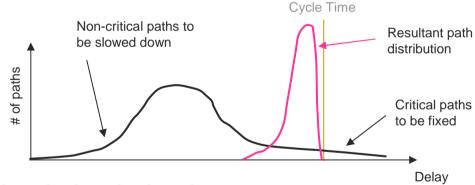

- To reduce leakage, multi-threshold voltage designs use high-Vt cells to decrease leakage current where performance is not critical

- By using such power optimization techniques, more paths become clustered in a narrow region around the cycle time, resulting in a large population of paths which are sensitive to small delay perturbations

- > PDF selection more complex

- More test data are needed

- Sensitivity to variations

- PSN has a significant impact on the timing behavior

- > Need to integrate PSN effects in delay test pattern generation

Solutions for high quality at-speed fault coverage are needed!

## **Test Power Estimation**

- Needed for test space exploration (DfT/ATPG) early in the design cycle

- Availability of scan enhanced design and ATPG patterns only at the gate level in today's design flows imposes the usage of gate-level estimators for test power

- Conventional flow adopted to perform estimation is simulation-based

- Challenges for multi-million gate SoCs

- > Time-consuming !!

- > Dump sizes can be very large !!

- The weighted transition model is widely used but not accurate enough

Faster and low cost solutions for test power estimation are needed!

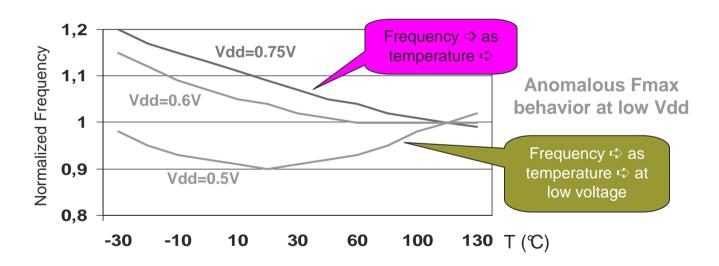

## **Test Conditions of LPD**

- Different activity levels in different parts of a die causes T° variations. Circuit delay change non-linearly with V and T°.

- Defining the worst-case timing conditions during test will be even more a challenge!!

Traditional Methods of testing at only high temperature for Fmax will be insufficient for LP devices!

# Thank You!