## Tutorial intitulé "Power-Aware Testing and Test Strategies for Low Power Devices"

Patrick Girard, Nicola Nicolici, Xiaoqing Wen

## ▶ To cite this version:

Patrick Girard, Nicola Nicolici, Xiaoqing Wen. Tutorial intitulé "Power-Aware Testing and Test Strategies for Low Power Devices". IEEE International NEWCAS Conference, Jun 2010, Montréal, Canada. lirmm-00820652

## HAL Id: lirmm-00820652 https://hal-lirmm.ccsd.cnrs.fr/lirmm-00820652

Submitted on 6 May 2013

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

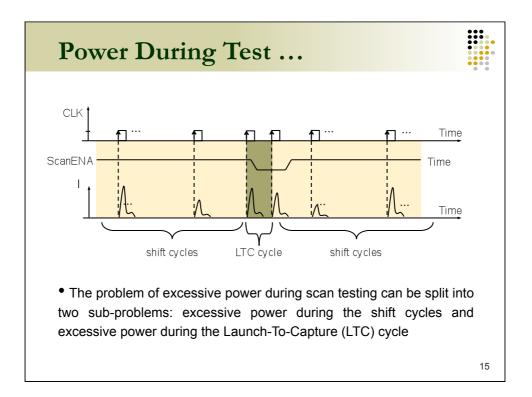

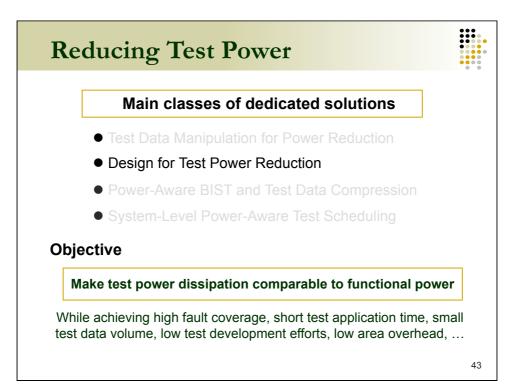

| During scan testing (standard or at-speed):                                                                                                                                                                                                                                                                       |                                                                                                                         |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|

| Shift Power Reduction                                                                                                                                                                                                                                                                                             | LTC Power Reduction                                                                                                     |  |

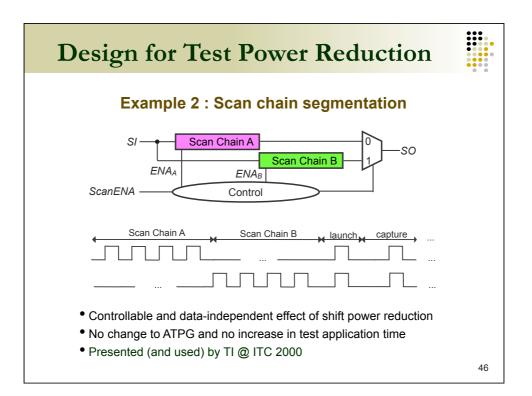

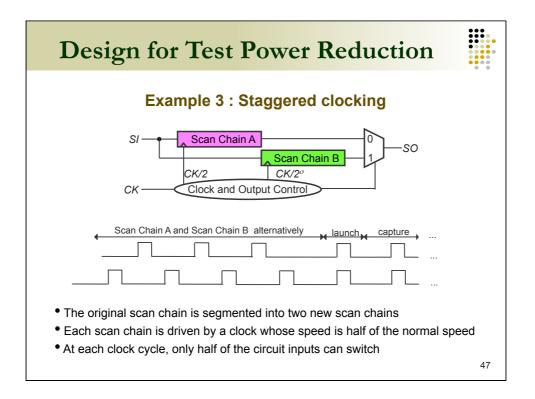

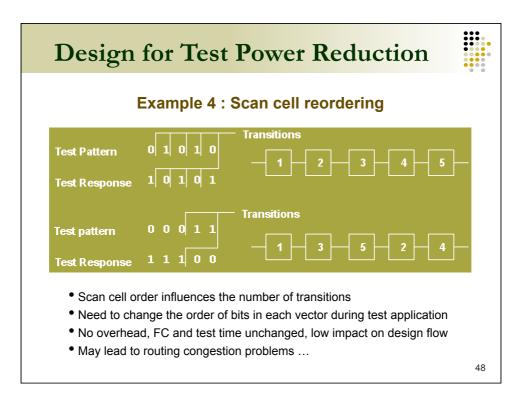

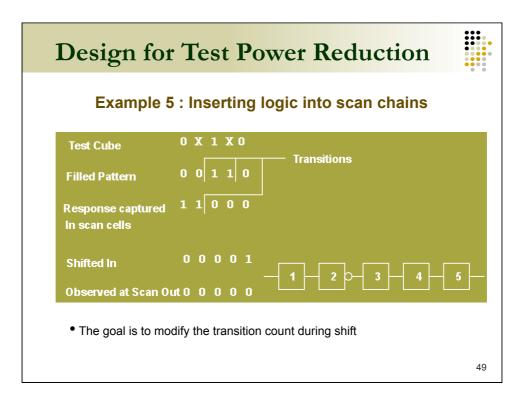

| <ul> <li>Shift Impact Blocking <ul> <li>blocking gate, special scan cell</li> <li>first-level power supply gating</li> </ul> </li> <li>Scan Chain Modification <ul> <li>scan cell reordering</li> <li>scan chain segmentation</li> <li>scan chain disable</li> </ul> </li> <li>Scan Clock Manipulation</li> </ul> | • Partial Capture<br>- circuit modification<br>- scan chain disable<br>- one-hot clocking<br>- capture-clock staggering |  |

| - splitting, staggering<br>- multi-duty clocking                                                                                                                                                                                                                                                                  |                                                                                                                         |  |

|                                                                                                                                                                                                                                                                                                                   | -                                                                                                                       |  |

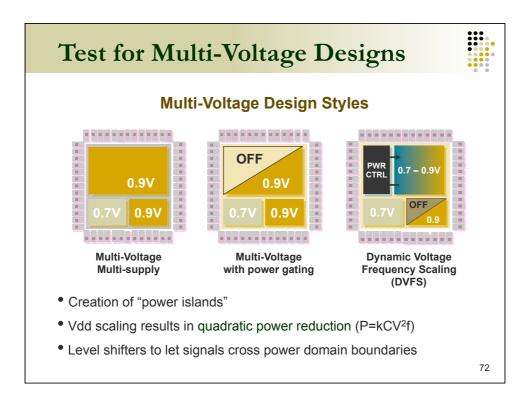

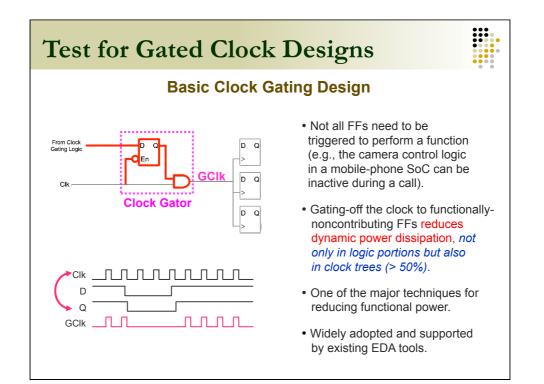

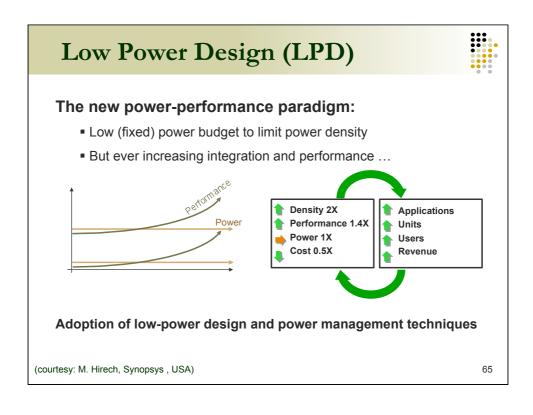

| System & Architecture<br>• Voltage / Frequency Scaling<br>• Architecture (parallel, well managed<br>pipeline, etc.)<br>• Others (H/S partitioning, instruction<br>set, algorithms, etc.)                 | IC Design & Implementation<br>- Clock Gating<br>- Multiple Supply Voltage<br>- Multiple Threshold Voltage<br>- Substrate-Bias<br>- Power Gating<br>- Others                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Circuit (Logic) Design<br>Low Power Cell Library<br>Gate sizing (to equalize paths)<br>Buffer insertion to reduce slew<br>Logic restructuring to avoid hazards<br>Memory Bit Cell and Compiler<br>Others | Process Technology <ul> <li>Reduce Vdd</li> <li>Threshold Voltage Option</li> <li>Low Capacitance Dielectric</li> <li>New Gate Oxide Material</li> <li>Transistor Sizing</li> <li>Others</li> </ul> |

| Main LPD techniques   | Power reduction |               |

|-----------------------|-----------------|---------------|

|                       | Dynamic         | Leakage       |

| Clock gating          | <i>✓</i>        |               |

| Power gating          | ✓               | 1             |

| Multi-Voltage domains | 1               |               |

| Julti-Threshold cells |                 | 1             |

| <u> </u>              | n combined tog  | ✓<br>ether to |