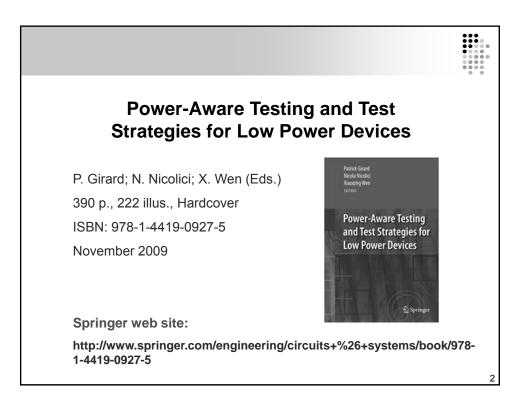

# Tutorial intitulé "Power-Aware Testing and Test Strategies for Low Power Devices"

Patrick Girard, Nicola Nicolici, Xiaoqing Wen

#### ▶ To cite this version:

Patrick Girard, Nicola Nicolici, Xiaoqing Wen. Tutorial intitulé "Power-Aware Testing and Test Strategies for Low Power Devices". ITC'2012: International Test Conference, Nov 2012, Anaheim, CA, United States. lirmm-00820734

## HAL Id: lirmm-00820734 https://hal-lirmm.ccsd.cnrs.fr/lirmm-00820734v1

Submitted on 6 May 2013  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### ITC 2012 – Anaheim, USA

### Power-Aware Testing and Test Strategies for Low Power Devices

Patrick GIRARD LIRMM / CNRS France

Nicola NICOLICI McMaster University Canada

Xiaoqing WEN Kyushu Institute of Technology Japan

# **Motivation and Objectives**

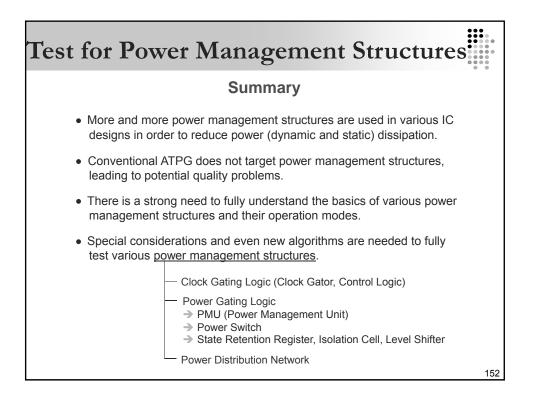

- · Power constraints have severe impact on test

- Implications for test engineers / test tool developers:

- Reduce power consumption in test mode becomes mandatory

- Dedicated test strategies for low-power devices are needed

- Objectives of this tutorial:

- Learning more about the impact of power during test

- How to alleviate test power issues

- How low-power devices and power management structures can be tested safely

3

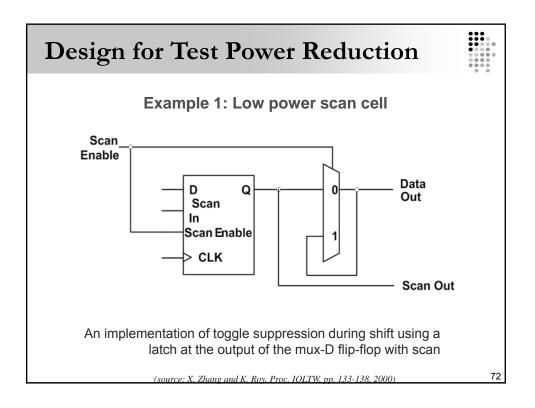

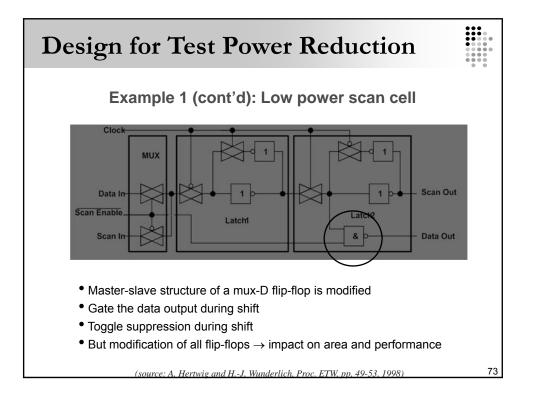

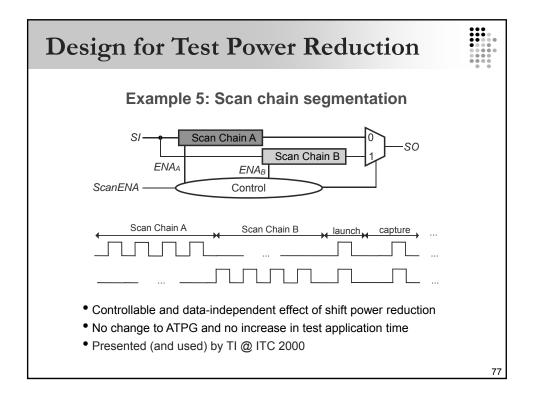

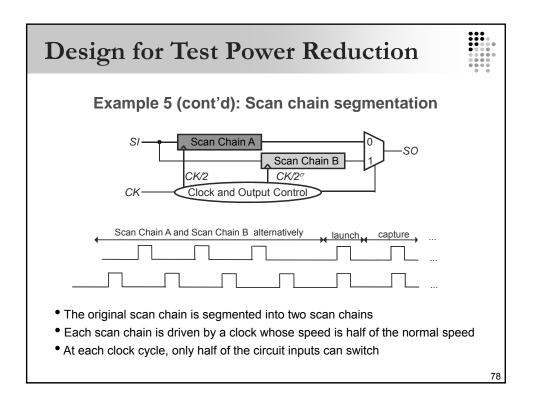

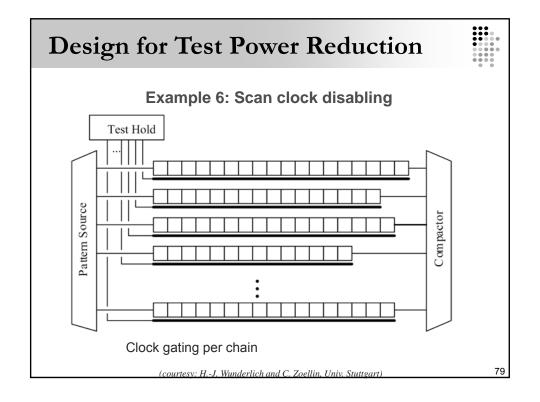

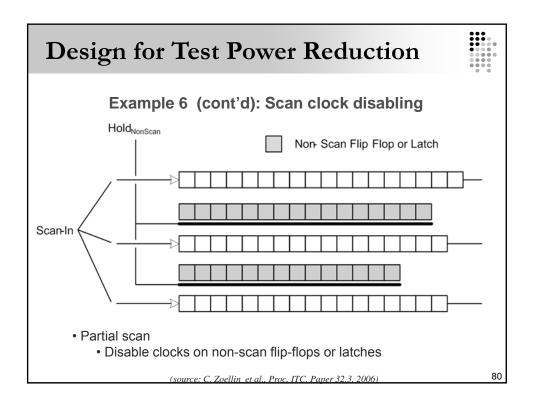

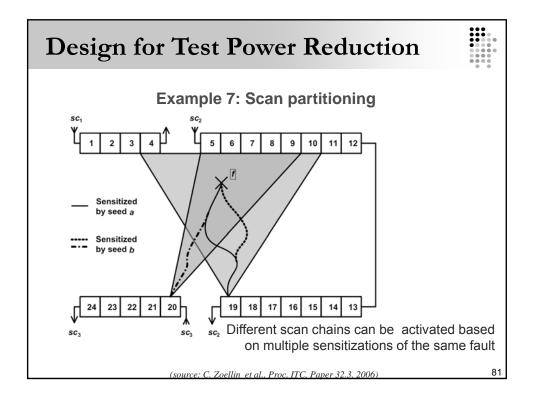

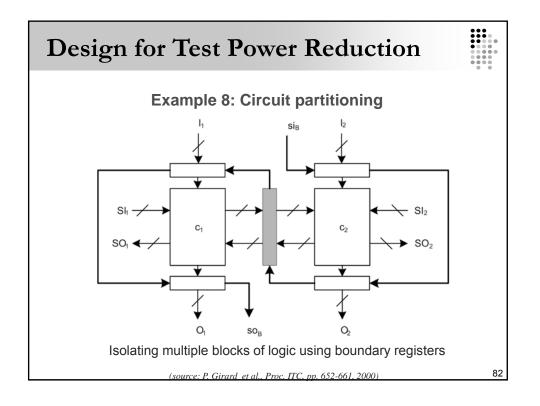

| Design for Test Pow                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                   |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|

| Shift Power Reduction                                                                                                                                                                                                                                                                                                                                                                                             | LTC Power Reduction                                                                                               |  |

| <ul> <li>Shift Impact Blocking         <ul> <li>blocking gate, special scan cell</li> <li>first-level power supply gating</li> </ul> </li> <li>Scan Chain Modification         <ul> <li>scan cell reordering</li> <li>scan chain segmentation</li> <li>scan chain disable</li> </ul> </li> <li>Scan Clock Manipulation         <ul> <li>splitting, staggering</li> <li>multi-duty clocking</li> </ul> </li> </ul> | Partial Capture     circuit modification     scan chain disable     one-hot clocking     capture-clock staggering |  |

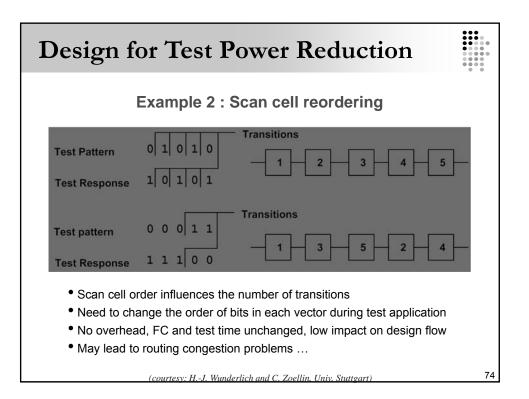

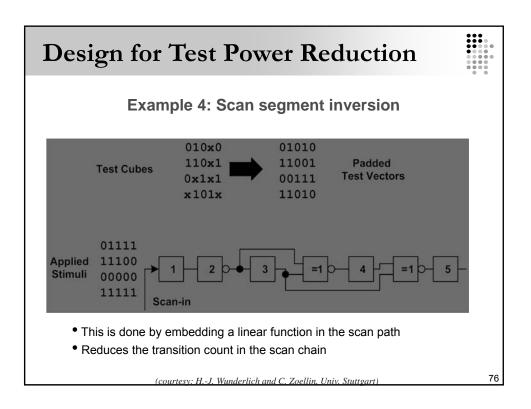

| Design for '                       | <b>Test Power Reduction</b>                            |    |

|------------------------------------|--------------------------------------------------------|----|

| Example                            | 3: Inserting logic into scan chains                    |    |

| Test Cube                          | 0 X 1 X 0                                              |    |

| Filled Pattern                     | 0 0 1 1 0 Transitions                                  |    |

| Response captured<br>In scan cells | 1 1 0 0 0                                              |    |

| Shifted In                         |                                                        |    |

| Observed at Scan Ou                |                                                        |    |

| • The goal is to mo                | odify the transition count during shift.               |    |

| (cou                               | rtesy: HJ. Wunderlich and C. Zoellin. Univ. Stuttgart) | 75 |

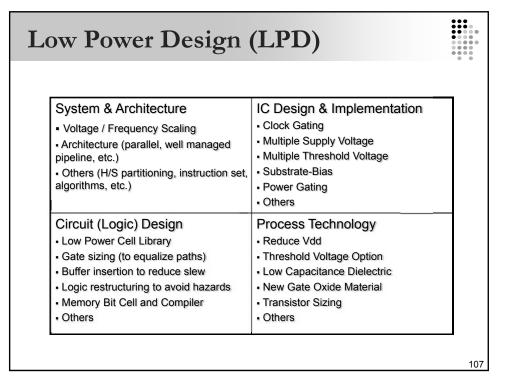

| Main LPD techniques         Dynamic         Leaka |

|---------------------------------------------------|

|                                                   |

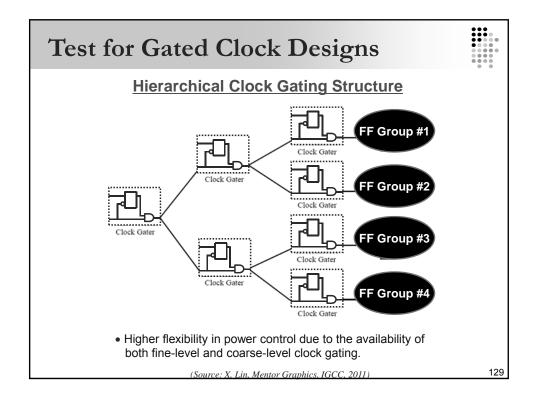

| Clock gating                                      |

| Power gating 🗸 🗸                                  |

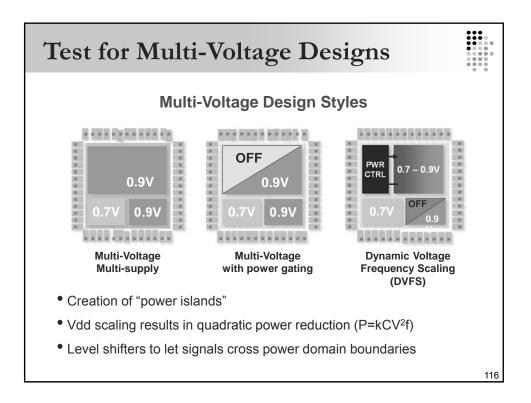

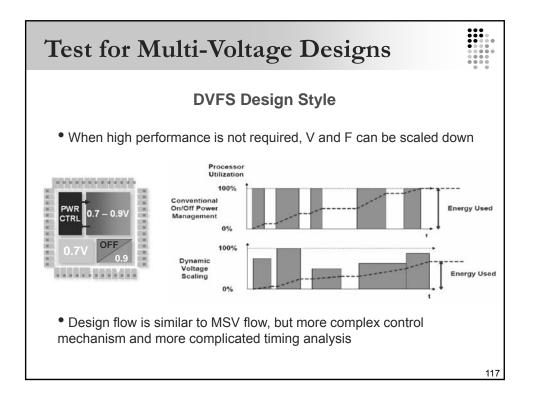

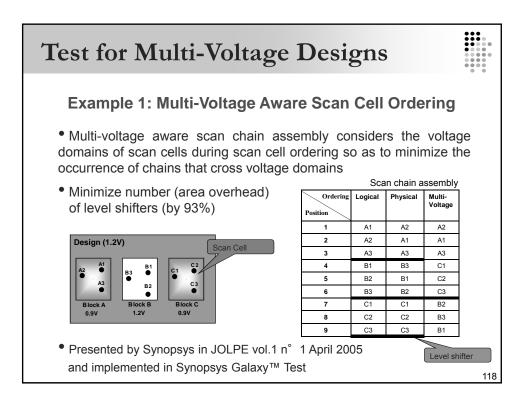

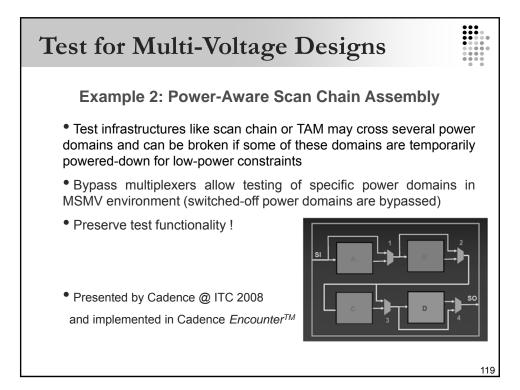

| Multi-Voltage domains                             |

| Multi-Threshold cells                             |

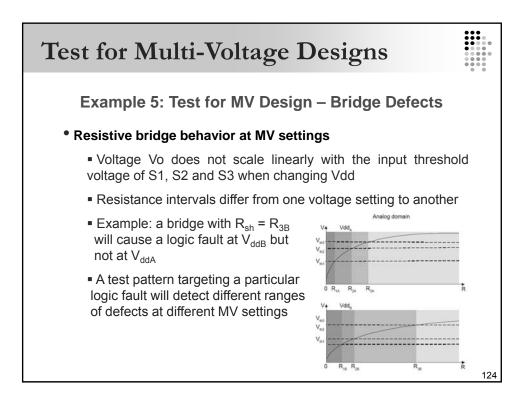

**Test for Multi-Voltage Designs** Example 6: Test for MV Design – Open Defects Open defects Due to unconnected nodes ■ Full opens → logic failures tested using static faults Transmission gate opens Better detectability at low Vdd settings (N. Zain Ali et al., ETS, 2006) Interconnect resistive opens ■ Resistive opens → time-dependent → tested using delay tests Better detectability at elevated Vdd settings \* (\* B. Kruseman et al., DATE, 2006) Longest path in the fault-free design 20 30 Cycle Time (ns) 126

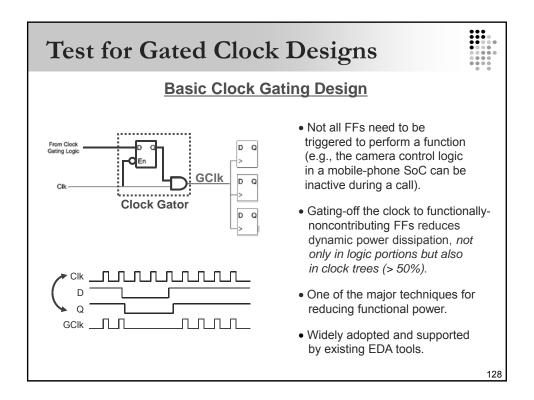

## <section-header><section-header><section-header><section-header><list-item><list-item><list-item><list-item><list-item>

Power-Aware DFT Tools

Image: Im