# Carbon nanotube interconnects for energy-efficient integrated circuits

Aida Todri-Sanial

### ▶ To cite this version:

Aida Todri-Sanial. Carbon nanotube interconnects for energy-efficient integrated circuits. TNT: Trends in Nanotechnology, Sep 2015, Toulouse, France. limm-01446233

## HAL Id: lirmm-01446233 https://hal-lirmm.ccsd.cnrs.fr/lirmm-01446233

Submitted on 25 Jan 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **Carbon Nanotube Interconnects for Energy Efficient Integrated Circuits**

### Aida Todri-Sanial

CNRS-LIRMM/University of Montpellier, Montpellier, France todri@lirmm.fr

Abstract - Carbon nanotubes (CNTs) due their unique mechanical, thermal, and electrical properties are being investigated as promising candidate material for on-chip and off-chip interconnects. The attractive mechanical properties of CNTs, including high Youngs modulus, resiliency and low thermal expansion coefficient offer great advantage for reliable and strong interconnects, and even more so for 3D integration. Through-Silicon-Vias (TSVs) enable 3D integration and implementation of denser, faster and heterogeneous circuits, which also lead to excessive power densities and elevated temperatures. Due to their unique properties, CNTs present an opportunity to address these challenges and provide solutions for reliable 3D integration. In this work, we perform detailed analyses of horizontally aligned CNTs and report on their efficiency to be exploited for 3D power delivery networks.

#### Introduction

One essential and most interesting application of the nanotubes in microelectronics is as interconnects using the ballistic (without scattering) transport of electrons and the extremely high thermal conductivity along the tube axis. Electronic transport in SWCNTS and MWCNTS can go over long nanotube lengths, 1um, enabling CNTs to carry very high currents (i.e. >  $10^9$  Acm<sup>2</sup>) with essentially no heating due to nearly 1D electronic structure.

In literature, the comparison of copper and CNTs have been limited to signal interconnects. Investigation of CNTs for power and clock delivery would also have a significant importance. It would reveal whether or not CNTs can potentially replace both signal, and power/ground copper wires. Additionally, clock and power networks are most vulnerable to electromigration, it is therefore critical to know whether or not CNTs improve their reliability. There are many works in literature that investigate CNT interconnects. The first group of works focuses on modeling aspects of CNT interconnects [1-2]. The second group of works focuses on performance comparison of CNT interconnects versus copper (Cu) interconnects [3-4]. Almost all these works have considered the application of CNT interconnects for signaling and few works focus on power delivery [4]. Complementary to these efforts, in this work, we investigate the application of horizontally aligned CNTs for power delivery network (i.e. both 2D and 3D ICs) while

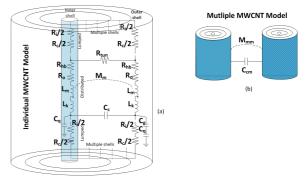

exploiting their unique electrical and thermal properties. In Fig. 1 the model of an individual MWCNT is shown with parasitics represent both dc conductance and high-frequency impedance i.e. inductance and capacitance effects. Multiple shells of a MWCNT are presented by their individual parasitics. Such model can also be applicable to SWCNTs where only a single shell is represented.

Fig.1 Electrical modeling of CNT interconnects.

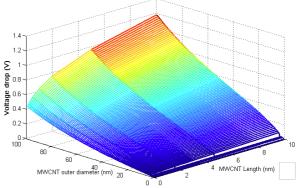

In Fig.2 the voltage drop on CNT interconnects due to its parasitics is plotted as a function of length and outer nanotube diameter.

Fig. 2. Voltage drop on CNT interconnect as a function of length and outer nanotube diameter.

#### References

[1] A. Naeemi, et al., "Performance Comparison Between Carbon Nanotube and Copper Interconnects for Gigascale Integration," IEEE Electron Device Letter, vol.26, no.2, pp.84-86, 2005.

[2] A. Naeemi, et al.,"Performance Modeling for Carbon Nanotube Interconnects in on-Chip Power Distribution," ECTC, pp. 420-428, 2007.

[3] H. Li, et al., "Low-Resistivity Long-Length Horizontal Carbon Nanotube Bundles for Interconnect Applications— Part II: Characterization," IEEE Trans. Electron Devices, vol.60, no.9, pp.2870-2876, 2013.

[4] N.H. Khan, et al, "The Feasibility of Carbon Nanotubes for Power Delivery in 3D Integrated Circuits," ASP-DAC, pp.53-58, 2012.