## Carbon-based Power Delivery Networks for nanoscale ICs: electrothermal performance analysis

Alessandro Magnani, Massimiliano De Magistris, Aida Todri-Sanial, Antonio Maffucci

#### ▶ To cite this version:

Alessandro Magnani, Massimiliano De Magistris, Aida Todri-Sanial, Antonio Maffucci. Carbon-based Power Delivery Networks for nanoscale ICs: electrothermal performance analysis. IEEE-NANO: Nanotechnology, Jul 2015, Rome, Italy. pp.416-419, 10.1109/NANO.2015.7388625. lirmm-01446739

### HAL Id: lirmm-01446739 https://hal-lirmm.ccsd.cnrs.fr/lirmm-01446739v1

Submitted on 26 Jan 2017

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Carbon-Based Power Delivery Networks for Nanoscale ICs: Electrothermal Performance Analysis

A. Magnani, M. de Magistris

Dep. of Electrical Engineering and Information Technology

University of Naples Federico II,

Naples, Italy

alessandro.magnani@unina.it, m.demagistris@unina.it

A. Todri-Sanial CNRS- LIRMM University of Montpellier Montpellier, France todri@lirmm.fr

#### A. Maffucci

Dep. of Electrical and Information Engineering University of Cassino and Southern Lazio Cassino, Italy maffucci@unicas.it

Abstract—This paper presents the electrothermal analysis of the performances of a Power Delivery Network for nanoscale integrated circuits, comparing standard (copper) with carbon nanotubes and graphene interconnects. Realistic carbon interconnects are considered, with the typical values of electrical and thermal parameters obtainable with the current fabrication technology. A temperature-dependent model for the electrical resistance is adopted, able to describe the case of negative temperature coefficient of the resistance, as it has been theoretically predicted and experimentally proved. The electrothermal analysis of the power network of a standard chip puts on evidence, for the first time, an interesting trade-off between voltage drop and temperature increase, while exploiting carbon nanotube and graphene based interconnects.

Keywords— Carbon nanotube; Graphene; On-chip power distribution networks; electro-thermal analysis.

#### I. INTRODUCTION

Nanoscale Integrated Circuits (ICs) will contain billions of transistors, operating at tens of GHz [1]. A big issue for nanoscale Power Distribution Networks (PDNs) is the increase of the power supply current per circuit area, and of the transient current slew rate, yielding an ohmic and inductive voltage drop, respectively. Another major issue is the heat produced either by the Joule effect and by the power switching activity [2]. The heat production not only imposes strong design constraints for its efficient dissipation, but also yields a chip temperature rise. Higher temperature affects the electrical performance, given the temperature dependence of the electrical resistivity [3]. Accurate simulations of the behavior of PDNs are possible only with an electrothermal modeling, where the electrical and thermal behaviors are simultaneously dealt with, *e.g.* [4].

The dramatic increase of copper resistivity at nanoscale has suggested to replace copper in on-chip interconnects with carbon nanotubes (CNTs) or graphene nanoribbons (GNRs) [1]. The performance of carbon-based materials have been intensely investigated for signal interconnects [5]-[7]. Few works have been so far devoted to their use for power grids: in [5] a comparative analysis between Cu and CNT interconnects is

carried out for a nanoscale on-chip PDN, whereas in [8]-[9] the analysis is extended to 3-D ICs. The cited works suggest that carbon interconnects may outperform Cu ones at the chip global level, provided that "good quality" interconnects are fabricated. This means: good control of alignment, chirality, dimension, and density, and low contact resistances at the interfaces carbon/metals. For instance, global level power interconnects require a minimum density of 1/2.5 nm², if made by single-walled CNTs (SWCNTs) [5], or a minimum length of 20 μm, if made by multi-walled CNTs (MWCNTs) [8].

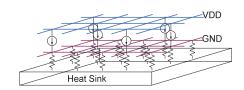

Due to technological limits, the physical parameters of a realistic carbon interconnect sensibly differ from the remarkable values experimentally obtained for isolated samples. Indeed, isolated CNTs may exhibit ballistic electrical transport for lengths up to some um, but in real CNT bundles the defects and the contacts may add huge parasitic resistances (of the order of  $100 \text{ k}\Omega$ ), hiding the effect of ballistic transport. Similarly, a huge thermal conductivity (3000-5000 W/mK) was reported for isolated CNTs or single GNRs, but this value drops to about 200 W/mK in CNT bundles [10] or GNR arrays [11]. The above considerations lead to the conclusion that the electrical performance of carbon interconnects are often overestimated. However, the greater stability of the resistance over temperature exhibited in some cases by a certain class of carbon lines, could be of great interest for PDNs. Indeed, a Temperature Coefficient of the Resistance (TCR) close to zero or even negative has been theoretically predicted [7] and experimentally reported [12]-[13]. This paper is devoted to study this effect, by means of an electrothermal analysis of a PDN, commonly structured as a multilayer grid, as in Fig. 1.

Fig. 1. Schematic of the considered PDN.

#### II. ELECTRO-THERMAL MODEL

Let us refer to the two-grids PDN for ICs reported in Fig.1. The ground and power grids, separated by an insulation layer, are connected to VDD and GND supply pins, respectively, through a series resistance  $R_{\text{supply}}$  at the four corners in the basic stamp element. For heat dissipation, one side of the chip is connected to a heatsink.

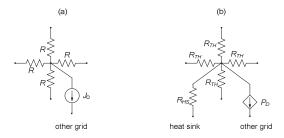

The electrical problem is modeled by two regular grids, where the connectivity on a node is depicted in Fig.2(a): the temperature-dependent resistors R(T) connect adjacent nodes of the same grid. The power and ground grids are connected by a current source  $J_0$ , which represents the circuit *activity*, i.e. the current demand of a circuit connected between VDD and GND pins. The solution of the electrical problem provides the *voltage drop* at any generic node i, defined as:

$$V_d(i) = V_{DD} - (V_n(i) - V_g(i)),$$

(1)

being  $V_n(i)$  and  $V_g(i)$  the node potentials with respect to the power and ground plane references, respectively.

The main sources of heat in PDNs are associated to the circuit activity and to the joule effects in the metal interconnects. A perfect duality between thermal and electric transport models exists, where the heat flow plays the role of an electrical current and the temperature difference corresponds to the electrical voltage. If we define a grid where the branch lengths are within the characteristic thermal length, we can adopt the same grid for the electrical and thermal problems, and define a unique thermal resistance between the nodes [14]. The generic node of the thermal network is shown in Fig.2(b): thermal resistances connect two nodes of the same grid, and the grids are connected by the equivalent sources modeling the heat generation  $P_D(i)=J_0V_d(i)$  modeling the power produced at node "i" by effect of the voltage drop (1) and of the current  $J_0$ . An additional thermal resistance connect the node to the heatsink.

The equivalent thermal model is here analyzed in steadystate, assuming negligible heat diffusion in the dielectric. Thus, in each power track of the metal interconnects the temperature distribution T(x) is solution of the 1-D heat diffusion equation:

$$\frac{d^2T(x)}{dx^2} = -\frac{g(x,T)}{k_m},$$

(2)

where g(x,T) is the power density of heat sources [W/m<sup>3</sup>] and  $k_m$  is the thermal conductivity of the material [W/mK].

Fig. 2. Generic node of the grids for: (a) electrical, and (b) thermal model.

The coupled problems are solved in a classical relaxation approach: the thermal problem is first solved at room temperature, obtaining the distribution of T. Then the electrical resistances R(T) are upgraded and the electrical circuit is solved, obtaining the voltage drop (1). After upgrading the thermal sources  $P_D(i)$ , the thermal problem is solved again, and so on. By establishing convergence between the problems, the final temperature and voltage drop distributions are obtained.

#### III. TEMPERATURE-DEPENDENT ELECTRICAL RESISTANCES

Let us first analyze the case when the PDN is made by conventional Cu interconnects. The electrical resistance of each track is commonly described by the linear law:

$$R(T) = R_0[1 + \beta(T - T_0)], \tag{3}$$

where  $T_0 = 300 \, \mathrm{K}$  is the room temperature,  $R_0$  is the resistance at  $T = T_0$  and  $\beta$  is the temperature coefficient. Given the cross section dimensions of the conductors analyzed hereinafter in Section IV, we can consider the "bulk" copper parameters, i.e. a room temperature resistivity of  $\rho_0 = 1.72 \cdot 10^{-8} \, [\Omega \mathrm{m}]$  and  $\beta = 0.0039 \, \mathrm{K}^{-1}$ . For nanoscale sizes (cross-section diameters smaller than about 100 nm), phenomena like electromigration and boundary and grain scattering lead to different values: at a line width of 14 nm, it would be  $\rho_0 = 8.19 \cdot 10^{-8} \, [\Omega \, \mathrm{m}]$ , and  $\beta = 0.012 \, \mathrm{K}^{-1} \, [7]$ , [16].

Let us now consider the case of replacing the copper with a CNTs or GNRs. The electrical resistance of a single CNT or GNR of length l may be put in the form [7], [16]:

$$R(T) = \frac{R_Q + R_{con}}{M(T)} + \frac{R_Q}{2M(T)} \frac{l}{l_{mfp}(T)},$$

(4)

where  $R_Q=12.9\,\mathrm{k}\Omega$  is the quantum resistance,  $R_{con}$  is a lumped parasitic resistance due to non-ideal contacts,  $l_{mfp}(T)$  is the mean free path and M(T) is the total number of conducting channels. As for Cu, the mean free path  $l_{mfp}(T)$  decreases as T increases, leading to increasing values of R. However, for a certain class of CNTs (MWCNTs) and for all the GNRs, the number of channels M(T) is increasing with T. For some values of the line length, this effect counteracts the effect of  $l_{mfp}(T)$ ,

leading to negative values of TCR = dR/RdT. This theoretical behavior [7], [16] has been demonstrated in [12] and [13]: for instance, in [13] for MWCNT lengths up to some tens of microns it has been reported:  $-19 \,\mathrm{m}\Omega/\mathrm{K} < TCR < -4 \,\mathrm{m}\Omega/\mathrm{K}$ .

#### IV. RESULTS

As a case study we refer to a PDN with the simple structure as in Fig.1, with each of the 4 electrical and thermal grids containing about 1 million nodes (i.e., a total of 4 millions nodes), that is a 20x20 replica of a basic structure of 51x51 nodes, as in [14]. Each single track has a length  $l = 5.88 \, \mu \text{m}$ ,

width w = 2.67  $\mu$ m and height H = 0.668  $\mu$ m. In addition, we assume  $V_{DD}$  = 1 V,  $R_{supply}$ =0.01  $\Omega$ ,  $R_{HS}$ =100x  $R_{TH}$ .

Let us consider CNT interconnects, assuming that each track is filled by a bundle of MWCNTs, with outer diameter of 50 nm and filling factor of 80%. We assume the realistic case where only 1/3 of the CNT shells are metallic, and the other are semiconducting [10]. In addition, we include the effects of the contact resistance in (4). As for GNR interconnect, we assume an array made of GNRs of width *W* and length *l*. Also in this case, the percent of metallic GNRs is assumed to be 1/3.

Assuming the temperature-dependent model for M and  $l_{mfp}(T)$  as in [7] and [16], we obtain for the given length a TRC<0 for CNTs and GNRs. However, the room temperature resistance  $R_0$  is smaller for Cu:  $R_{0,Cu}=56~\text{m}\Omega$ , while  $R_{0,CNT}=152.4~\text{m}\Omega$ , and  $R_{0,GNR}=1.19~\Omega$ .

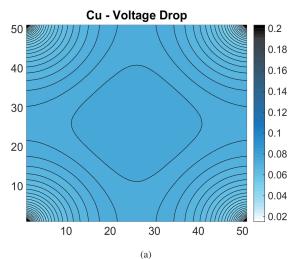

Fig. 3 Maps for voltage drop (a) and incremental temperature (b) in a self consistent electrothermal solution fot the case of Copper.

For this case-study, the temperature-behavior of R for carbon lines may be fitted by:

$$R(T) = \alpha_0 + \alpha_1 T + \alpha_2 T^2, \tag{5}$$

with the fitting coefficients  $a_i$  given in Table I.

TABLE I. FITTING COEEFICIENTS IN EQ. (5)

|     | $lpha_0 \ [\Omega]$ | $\alpha_1$ [m $\Omega$ /K] | $\alpha_2$ [ $\mu\Omega/K^2$ ] |

|-----|---------------------|----------------------------|--------------------------------|

| CNT | 0.42                | -1.42                      | 1.76                           |

| GNR | 3.30                | -10.15                     | 10.42                          |

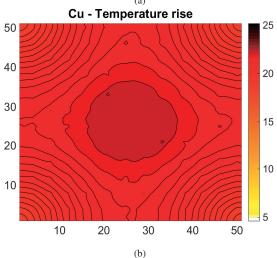

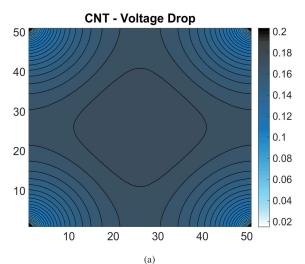

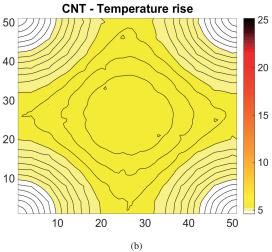

Fig. 4 Maps for voltage drop (a) and incremental temperature (b) in a self consistent electrothermal solution fot the case of Carbon Nanotubes.

As for the thermal resistance, assuming bulk value for thermal conductivity for copper,  $R_{TH,Cu}$ =8473K/W. Considering a realistic value of thermal conductivity of 200 W/mK, which has been experimentally reported for multi-CNTs or multi-GNRs [10]-[11], we get  $R_{TH,CNT}$ =  $R_{TH,GNR}$  = 850 K/W.

A steady state analysis of the electro-thermal problem has been carried out, based on the efficient solution of the two (linear) sub-problems (electrical network at fixed temperature, thermal problem at fixed heat production rate), in a classical relaxation cycle for the self-consistent solution of the non linear joint problem [14]. As a first result, the voltage drop and thermal maps for the case of Cu (3a and 3b) and for the case of CNT (Fig.4a and Fig.4b) are shown, for the basic stamp structure at the center of the large grid, at the fixed value of the current  $I_0$ =0.4 mA.

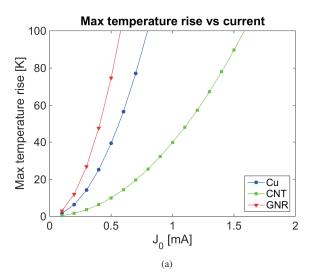

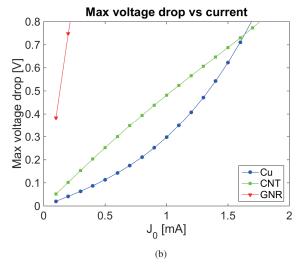

Fig. 5. Max voltage drop (a) and max incremental temperature (b) as functions of current for copper, carbon nanotubes and graphene.

A more extended analysis, with different values of the current, is given in Fig. 5 also for GNR. It reveals, at realistic parameters values, an interesting trade-off between the voltage drop and the temperature rise for Cu and CNTs, leaving the GNR solution still non performant. This may open new scenarios for the design of nanoscale ICs PDNs.

#### REFERENCES

- [1] Intern. Technology Roadmap of Semiconductors, Ed. 2013, www.itrs.net/

- [2] L.-R. Zheng and H. Tenhunen, "Fast modeling of core switching noise on distributed Irc power grid in ULSI circuits," IEEE Trans. on Advanced Packaging, Vol.24, pp. 245-254, 2001.

- [3] M. Pedram, and S. Nazarian, "Thermal modeling, analysis, and management in VLSI circuits: principles and methods," Proceedings of the IEEE, Vol. 94, pp.1487-1501, 2006.

- [4] A. Todri, S. Kundu, P. Girard, A. Bosio, L. Dilillo, A. Virazel, "A study of tapered 3-D TSVs for power and thermal integrity," IEEE Trans. on VLSI Systems, Vol.21, pp. 306 – 319, 2013.

- [5] A. Naeemi, J.D. Meindl, "Performance modeling for single- and multiwall carbon nanotubes as signal and power interconnects in gigascale systems," IEEE Trans. on Electron Devices, Vol.55, pp. 2574-2582, 2008.

- [6] H. Li, C. Xu, N. Srivastava, and K. Banerjee, "Carbon nanomaterials for next-generation interconnects and passives: physics, status, and prospects," IEEE Tran. on Electron Devices, Vol.56, pp.1799-1821, 2009.

- [7] A. G. Chiariello, A. Maffucci, G. Miano, "Circuit models of carbon-based interconnects for nanopackaging," IEEE Trans. on Components, Packaging and Manufacturing, Vol.3, pp.1926-1937, 2013.

- [8] N. H. Khan, and S. Hassoun, "The feasibility of Carbon Nanotubes for power delivery in 3-D Integrated Circuits," Proc. of 17<sup>th</sup> Asia and South Pac. Design Autom. Conf. (ASP-DAC), p. 1B-3 Sidney, Australia, 2012.

- [9] A. Todri-Sanial, "Investigation of horizontally aligned carbon nanotubes for efficient power delivery in 3D ICs," Proc. of IEEE 18th Workshop on Signal and Power Integrity (SPI), Ghent, Belgium, May 2014.

- [10] J. Yang, Q. Zhang, G. Chen, S. F. Yoon, J. Ahn, S. G. Wang, Q. Zhou, Q. Wang, and J.Q. Li, "Thermal conductivity of multiwalled carbon nanotubes," Physical Review B, Vol. 66, p.165440, 2002.

- [11] H.-Y. Cao, Z.-X. Guo, H. Xiang, and X.-G. Gong, "Layer and size dependence of thermal conductivity in multilayer graphene nanoribbons," Physics Letters A, Vol. 376, pp.525-528, 2012.

- [12] Q.Shao, G.Liu, D. Teweldebrhan, and A. A. Balandin, "High-temperature quencing of electrical resistance in graphene interconnects," Applied Physics Letters, Vol.92, p.202108, 2008.

- [13] S. Vollebregt, S. Banerjee, K. Beenakker, and R. Ishihara, "Size-dependent effects on the temperature coefficient of resistance of carbon nanotube vias," IEEE Trans. Electron Dev., Vol. 60, pp. 4085-4089, 2013.

- [14] A. Magnani, M. de Magistris, A. Maffucci, A. Todri-Sanial, "A node clustering reduction scheme for power grids electrothermal analysis," accepted at IEEE Work. on Signal and Power Integrity, SPI 2015, Berlin, Germany, May 2015.

- [15] C. Knoth, H. Jedda, U. Schlichtmann, "Current source modeling for power and timing analysis at different supply voltages", Proc. of DATE 2012, pp. 923 – 928, Dresden, Germany, Mar 2012.

- [16] A. G. Chiariello, A. Maffucci, G. Miano, "Temperature effects on electrical performance of carbon-based nano-interconnects at chip and package level", International Journal of Numerical Modelling: Electronic Networks, Devices and Fields, Vol. 26, pp.560–572, 2013.