## Exploration of magnetic memory for ultra low-power systems-on-chip

Guillaume Patrigeon, Sophiane Senni, Pascal Benoit, Lionel Torres

# Using benefits of emerging Non-Volatile memories in ultra low power systems-on-chip to reduce power consumption for Internet of Things devices

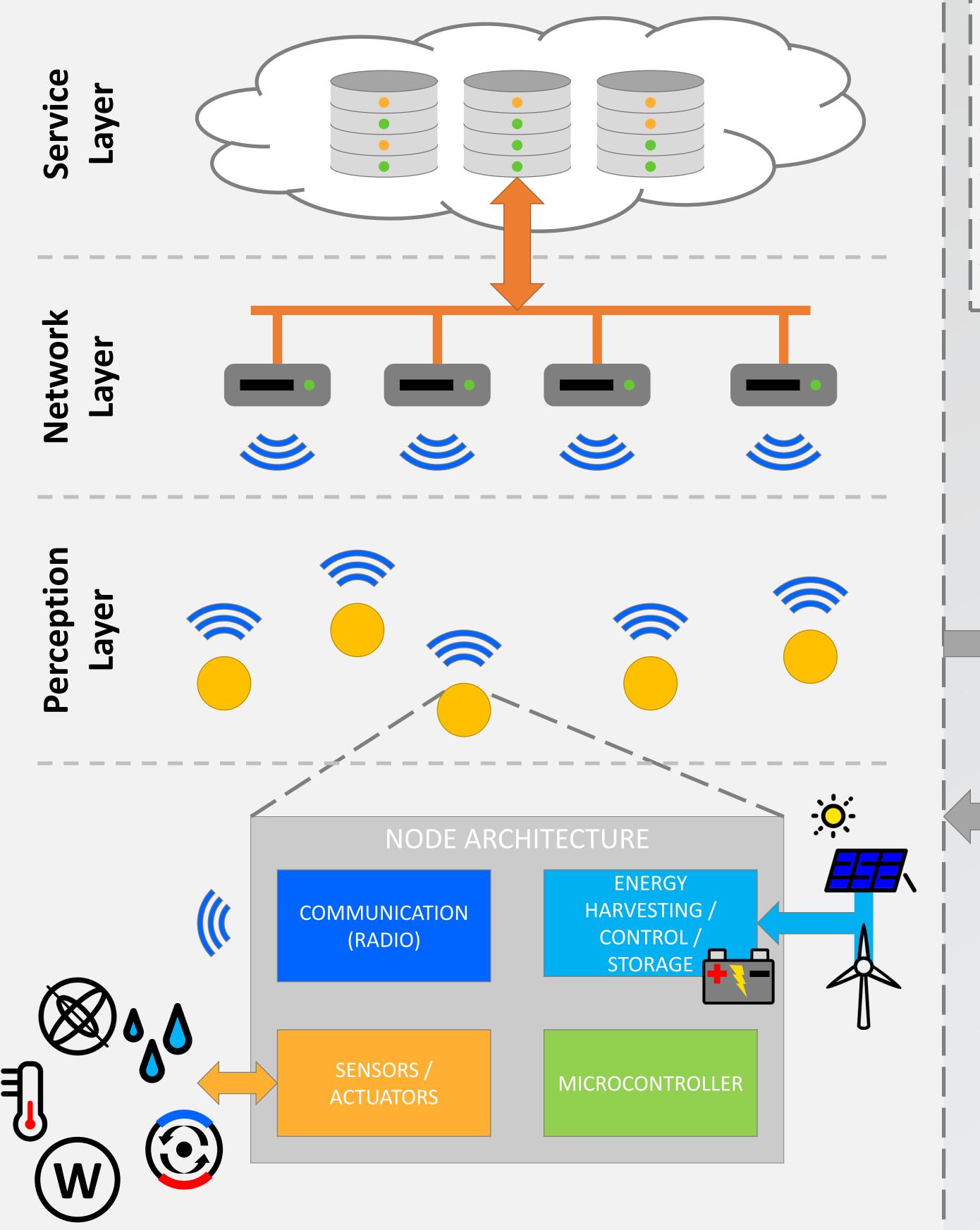

High constraints:  $\rightarrow$  Reliable  $\rightarrow$  Secure  $\rightarrow$  Low cost  $\rightarrow$  Low size  $\rightarrow$  Long lifetime

Reducing the battery size and energy harvesting devices size means less energy power available. To keep a long lifetime, it is very important to reduce power consumption.

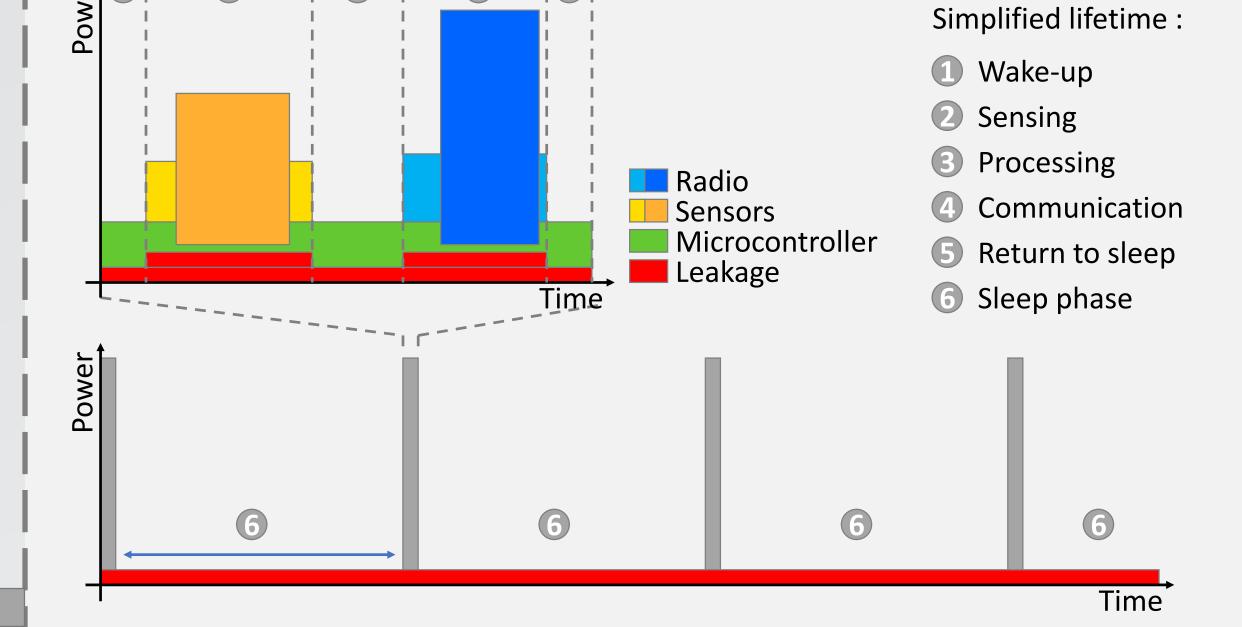

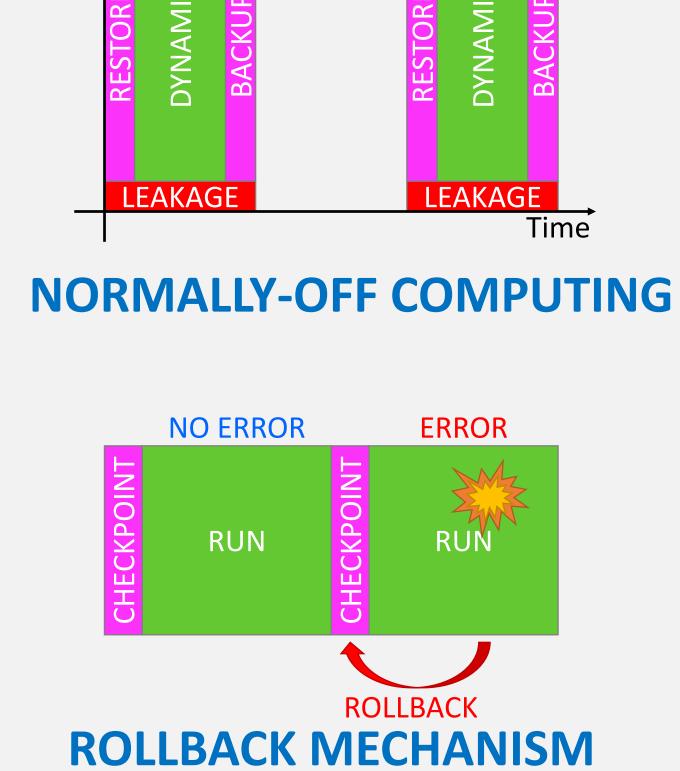

The final application defines the duration of the sleep phases. In a lot of applications which need long sleep periods, the energy consumption during sleep phases is higher than the one during running phases.

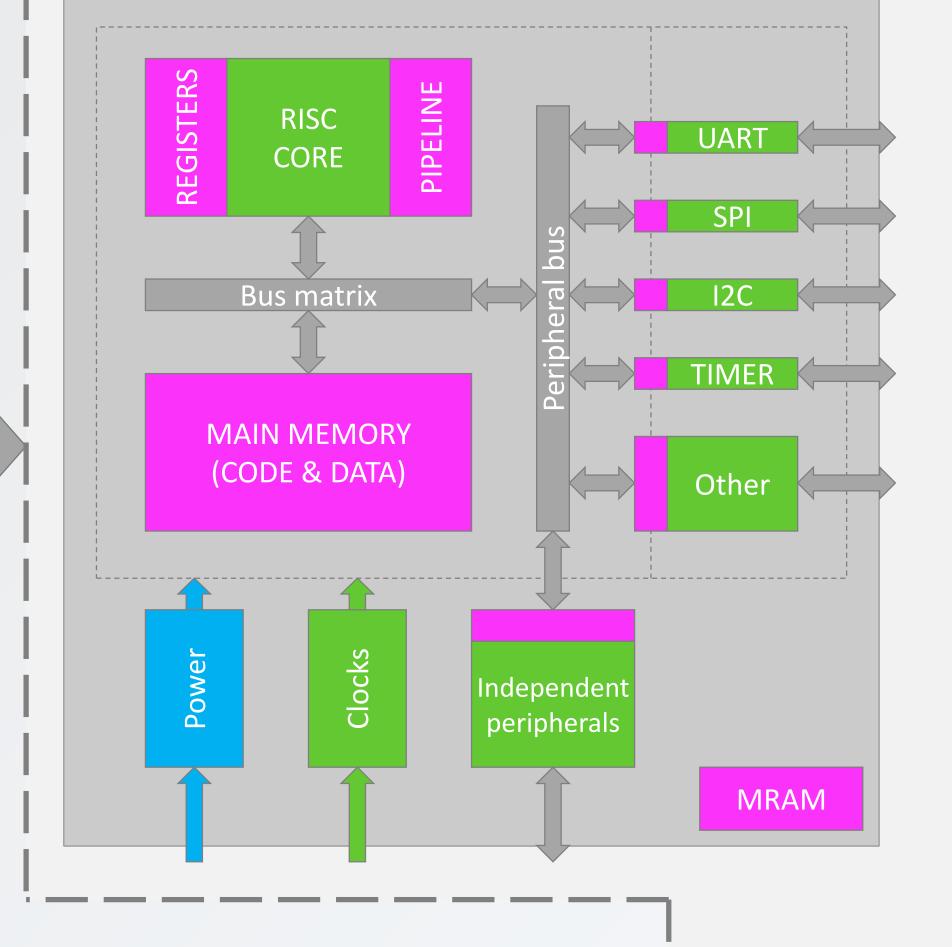

#### **MRAM-BASED MICROCONTROLLER**

RISC 32-bit MRAM-based MICROCONTROLLER

. . . . . . .

**CONCEPTION &** VALIDATION

When devices (radio, sensors, actuators...) are unused they can be powered off. But the microcontroller should stay allways active.

Even with various sleep modes, the static power consumtpion of a microcontroller is still too high for a lot of applications.

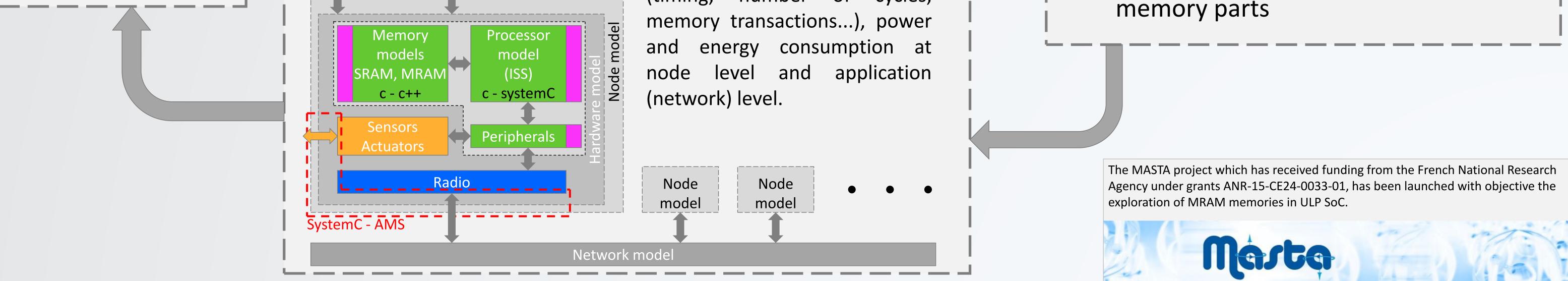

### **DESIGN SPACE EXPLORATION**

IoT benchmarks Standalone, OS (FreeRTOS...

Estimation of performance of cycles, (timing, number

#### SINGLE MEMORY ARCHITECTURE

- Code & Data sections scalable by user

- Easy and fast NV data read and write

- No leakage current for unsued

Laboratoire d'Informatique, de Robotique et de Microélectronique de Montpellier 161 rue Ada, 34095 Montpellier, France LIRMM-UMR CNRS 5506 - Université de Montpellier *firstname.lastname@*lirmm.fr