# Power and Performance Analysis of Doped SW/DW CNT for On-Chip Interconnect Application

Aida Todri-Sanial, Jie Liang

## ▶ To cite this version:

Aida Todri-Sanial, Jie Liang. Power and Performance Analysis of Doped SW/DW CNT for On-Chip Interconnect Application. GRAPHENE, Mar 2017, Barcelone, Spain. lirmm-01800286

## HAL Id: lirmm-01800286 https://hal-lirmm.ccsd.cnrs.fr/lirmm-01800286

Submitted on 25 May 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Power and Performance Analysis of Doped SW/DW CNT for On-Chip Interconnect Application

#### Jie Liang

Aida Todri-Sanial CNRS-LIRMM/University of Montpellier Montpellier, France

#### Jie.liang@lirmm.fr

Abstract – In this paper, we investigate the electrical properties of doped single wall (SW) and double wall (DW) carbon nanotube (CNT) for integrated circuits interconnect applications. P-type lodine charge transferred doping has been studied for modifying electrical properties and models of CNT interconnects. We perform circuit-level simulations on a 5-stage ring oscillator implemented with 45nm CMOS technology node devices for power and performance analysis with doped SWCNT and DWCNT interconnects.

#### Introduction

There is a lot of interest and on-going research on carbon nanotubes as a novel material for faster and energy efficient devices, next generation of organic solar cells and fast-charging batteries. In this work, we explore CNT as back-end-of-line interconnect material for integrated circuits. With continuous technology node scaling following Moore's law, the impact of interconnects is becoming dominant due to their significant contribution to delay and power consumption on very large scale integrated (VLSI) circuit. Current copper interconnects are reaching their limit on current density, thermal conductivity performance, thus finding a new interconnect material is imminent and is an on-going quest [ITRS2.0].

CNT with its high conductivity, high electromigration, and the low-temperature effect is a promising candidate for on-chip interconnects applications [6]. Here, we investigate on metallic CNTs as on-chip interconnects material for signal, clock and power delivery. Uncontrollable chirality of CNTs motivates us to study doped CNTs with the expectation of optimizing semiconducting CNTs and enhancing metallic CNTs' performance. In this paper, we study p-type lodine intercalate doping. lodine is known as a good donor. lodine provides charge transfer towards CNT - this type of doping is chemically and morphologically more stable than CNT substitutional surface doping [5]. We consider an iodine molecule chain located inside the innermost shell of CNTs. The different number of iodine atoms in the chain represent different doping concentration, which shifts Fermi-level differently in a CNT Fermi-Dirac energy band. Density-functional Theory with Generalized Gradient Approximation (DFT-GGA) [8] can calculate the conductivity of this p-type lodine doping. By dividing the conductivity after doping by intrinsic one electron quantum conductivity  $G_0$  ( $G_0 = 2e^2/h$ ) gives the number of conducting channels of doped CNTs (we electron occupies consider one one conducting channel). We vary the number of conducting channels in simulations to see how doping impacts the electrical performance of metallic CNT interconnects.

#### Physical electrical modeling and simulations

Based on Banerjee and Li's work [1][2], We investigate on electrical physical modeling of doped SWCNT and DWCNTs. A SWCNT is modeled as RLC (resistance, inductance, and capacitance) circuit with intrinsic quantum components and diffusive scatterina dependences. For DWCNT, mutual interaction effects between two shells are also taken into account. For the doped CNTs, quantum resistance and capacitance are modified accordingly. From quantum physics, it is expected that doping shifts the Fermi-level position, hence provides more available electron states for charge transport which increases the number [3] of

conducting channels as shown in equation (1) below:

$$N_{channels/shell} = \sum_{all \ subband} \frac{1}{\exp\left(\frac{|E_i - E_F|}{k_B}\right) + 1}$$

(1)

Where  $E_i - E_F$  is the difference between the possible participating electron energy subband and the Fermi-energy level.

We believe that doping reduces the overall CNT resistance (R) [4]; however, it increases the capacitance (C) effects where the quantum capacitance is  $C_Q = N_{channels} \times 200 aF$  (where 200 aF is calculated for one electron conducting channel [7]). Therefore, we aim to study the impacts on delay and power consumption for doped CNTs interconnects which depend on both R and C parasitics.

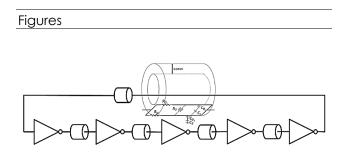

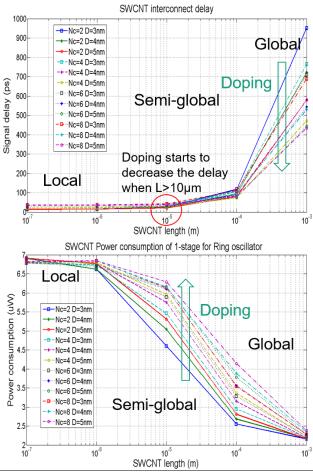

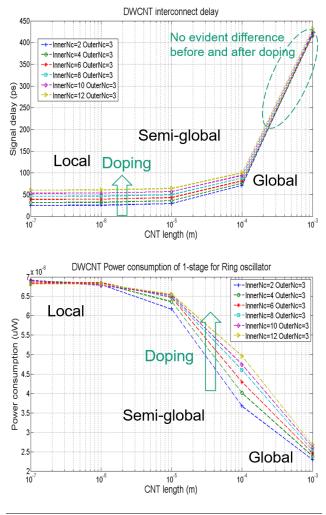

In this paper, we perform circuit-level simulations to analyze delay and power consumption for SWCNT and DWCNT interconnect before and after doping. Ring oscillator (which includes five inverter stages implemented in 45nm CMOS technology node) simulations with electrical models (Figure 1) have been performed on Cadence with Verilog-A models. We study the power and performance (i.e., signal delay) for different SWCNTs (Figure 2) and DWCNTs (Figure 3). SWCNT's diameters are chosen to vary from 3nm to 5nm, which are also the most reliable fabricating range. Based on the calculation of DFT-GGA and methodology described at the end of the previous section, we vary the number of conducting channels from 2 to 8 for SWCNT to represent doping effects corresponding to more available electron transport states after Fermi-level shift. For DWCNT, the inner diameter is chosen as 5nm, and the inter-shell distance is respected to the Van der Waals distance (0.34nm). Based on the study of iodine intercalate doping of CNTs [5] and DFT-GGA calculation, we assume for a DWCNT, the augmentation of conducting channels is directly related to the inner shell; hence, we only vary the inner shell conducting channel numbers from 2 to 12.

### Simulation results and discussions

Simulation results show that with increasing of CNT length, signal delay increase and power consumption decrease for both SWCNT and DWCNT. SWCNT used as local interconnect length (< 1µm), show no evident better performances on delay and power consumption after doping. For semi-global interconnect length (1-100µm), doping with 8 conducting channels leads up to 4 times higher capacitance effect which gives a 26.9% augmentation of power consumption; however, doping starts to have a decreasing effect on delay when SWCNTs are longer than 10µm. For CNT length of 1mm (global interconnect), doping can reduce 27% of increase 7% of delav but power consumption.

For DWCNT, doping does not improve signal delay on different interconnect lengths. We obtain up to 66.7% of capacitance increase when inner shell conducting channels vary from 2 to 12. However, we observe that overall delay of DWCNT is less than in SWCNT interconnects especially for lengths longer than 100µm. For an interconnect length of 1mm, signal delay can be reduced by 7.6% when using doped DWCNT instead of doped SWCNT, and with a delay reduction of 54.7% when compared to pure SWCNT interconnects.

#### Conclusion

In this paper, we investigate the electrical modeling of Iodine molecules intercalate charge transfer doping for SWCNTs and DWCNTs as on-chip interconnect material. We also provide signal delay and power consumption simulations for doped SWCNTs and DWCNTs with different aspect ratios. Our simulation results show that for a local interconnect length (< 1µm), doping does SWCNTs and **DWCNTs** not improve interconnect performance. In the semiglobal interconnect range (1-100µm), doped SWCNT starts to have better performance as SWCNT get longer than 10µm. Meanwhile, doped global interconnects DWCNTs with the length of 1mm, can reduce up to 54.7% of signal delay compared to pure SWCNT. However, no significant improvement in power consumption is observed mainly due to an increase of quantum capacitance.

Figure 1: Ring oscillator simulations of DWCNT with RC circuit model.

**Figure 2:** Signal delay and power consumption for SWCNT interconnect with different conducting channels.

**Figure 3:** Signal delay and power consumption for DWCNT interconnect with different conducting channels.

#### References

- Srivastava, Navin, and Kaustav Banerjee. "Performance analysis of carbon nanotube interconnects for VLSI applications." *ICCAD-*2005. IEEE/ACM International Conference on Computer-Aided Design, 2005. IEEE, 2005.

- [2] Li, Hong, et al. "Circuit modeling and performance analysis of multi-walled carbon nanotube interconnects." *IEEE Transactions* on electron devices55.6 (2008): 1328-1337.

- [3] F. V. Paez, "Effects of Doping Single and Double Walled Carbon Nanotubes with Nitrogen and Boron," Master thesis at MIT 2006.

- [4] J. Liang, L. Zhang, N. Azemard-Crestani, P. Nouet, A. Todri-Sanial, "Physical Description and Analysis of Doped Carbon Nanotube Interconnects", in IEEE Power and Timing Modeling, Optimization and Simulation (PATMOS), pp.1-4, 2016.

- [5] D. Tristant, "Analyse des Améliorations des Propriétés Electroniques des Matériaux

Carbonés par Interaction d'Espèces Chimiques: Approche Numérique Combinée à la Spectroscopie Raman", PhD thesis at INSA de Toulouse, France, 2016.

- [6] Carbon Nanotube Interconnects: Process, Design and Applications, by Aida Todri-Sanial, Jean Dijon, and Antonio Maffucci, Springer 2016, ISBN#: 978-3-319-29744-6.

- [7] S. Vollebregt, "Carbon Nanotubes as Vertical Interconnects in 3D Integrated Circuits", PhD thesis at Elektrotechnisch ingenieur, Technische Universiteit Delft, 2014.

- [8] Perdew, John P., Kieron Burke, and Matthias Ernzerhof. "Generalized gradient approximation made simple." *Physical review letters* 77.18 (1996): 3865.