# Design of Double-Upset Recoverable and Transient-Pulse Filterable Latches for Low Power and Low-Orbit Aerospace Applications

Aibin Yan, Yan Chen, Zhelong Xu, Zhili Chen, Jie Cui, Zhengfeng Huang, Patrick Girard, Xiaoqing Wen

### ► To cite this version:

Aibin Yan, Yan Chen, Zhelong Xu, Zhili Chen, Jie Cui, et al.. Design of Double-Upset Recoverable and Transient-Pulse Filterable Latches for Low Power and Low-Orbit Aerospace Applications. IEEE Transactions on Aerospace and Electronic Systems, 2020, 56 (5), pp.3931-3940. 10.1109/TAES.2020.2982341. lirmm-03031912

## HAL Id: lirmm-03031912 https://hal-lirmm.ccsd.cnrs.fr/lirmm-03031912

Submitted on 30 Nov 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés. Design of Double-Upset Recoverable and Transient-Pulse Filterable Latches for Low-Power and Low-Orbit Aerospace Applications

AIBIN YAN<sup>®</sup> YAN CHEN<sup>®</sup> ZHELONG XU ZHILI CHEN<sup>®</sup> JIE CUI<sup>®</sup> Anhui University, Hefei, China

**ZHENGFENG HUANG** Hefei University of Technology, Hefei, China

**PATRICK GIRARD**<sup>(D)</sup>, Fellow, IEEE University of Montpellier / CNRS, Montpellier, France

XIAOQING WEN<sup>(D)</sup>, Fellow, IEEE Kyushu Institute of Technology, Fukuoka, Japan

Manuscript received October 30, 2019; revised January 27, 2020 and February 25, 2020; released for publication March 14, 2020. Date of publication March 20, 2020; date of current version October 9, 2020.

DOI. No. 10.1109/TAES.2020.2982341

Refereeing of this contribution was handled Z. Davis.

This work was supported in part by the National Natural Science Foundation of China under Grant 61974001, Grant 61874156, Grant 61674048, Grant 61904001, Grant 61872001, and Grant 61834006, and in part by the Anhui University Doctor Startup Fund under Grant Y040435009. This paper was presented in part at the Conference and Exhibition on Design, Automation and Test in Europe, Florence, Italy, March 2019.

Authors' addresses: Aibin Yan, Yan Chen, Zhelong Xu, Zhili Chen, and Jie Cui are with the Anhui Engineering Laboratory of IoT Security Technologies, and School of Computer Science and Technology, Anhui University, Hefei 230039, China, E-mail: (abyan@mail.ustc. edu.cn; yanchenvv@qq.com; restraintxu@qq.com; zlchen@ahu.edu.cn; cuijie@mail.ustc.edu.cn); Zhengfeng Huang is with the School of Electronic Science and Applied Physics, Hefei University of Technology, Hefei 230009, China, E-mail: (huangzhengfeng@139.com); Patrick Girard is with the Laboratory of Informatics, Robotics and Microelectronics of Montpellier, University of Montpellier/CNRS, 34095 Montpellier, France, E-mail: (girard@lirmm.fr); Xiaoqing Wen is with the Graduate School of Computer Science and Systems Engineering, Kyushu Institute of Technology, Fukuoka 8208502, Japan, E-mail: (wen@cse.kyutech.ac.jp). (*Corresponding author: Zhengfeng Huang.*)

To meet the requirements of both high reliability and low power in low-orbit aerospace applications, this article first presents a singleevent Double-Upset (SEDU) self-Recoverable and single-event Transient (SET) Pulse Filterable (DURTPF) latch design with low power. The DURTPF latch mainly consists of eight mutually feeding-back C-elements (CEs) and an SET pulse filterable Schmitt-trigger (ST). To make an ST behave not only as a pulse filterable ST but also as an error interceptive CE, an input-split ST is created, leading to an enhancedversion of the DURTPF latch, namely DURTPF-EV. The DURTPF-EV latch mainly consists of seven mutually feeding-back CEs including an input-split ST. Simulation results demonstrate both the SEDU self-recoverability and SET pulse filterability of the proposed latches at the cost of moderate silicon area. Using the clock gating technology, the DURTPF latch reduces power dissipation by about 63% on average compared with the state-of-the-art SEDU self-recoverable latch designs that are not SET-pulse filterable. Moreover, the DURTPF-EV latch is more cost-effective and its reliability is also enhanced, making it more suitable for low power and low-orbit aerospace applications.

#### I. INTRODUCTION

Nano-scale complementary metal-oxide semiconductor (CMOS) chips make it possible for aerospace vehicles, relay satellites, 5G terminals, etc., to connect, interact, and exchange data with each other. However, for unhardened electronic devices fabricated using the advanced nano-scale CMOS technologies, radiation effects can easily cause soft errors due to the strike of high-energy particles such as neutrons, protons, alpha particles, and electrons [1]. Soft errors behave as transient but not permanent errors, and with technology scaling, more and more represent a serious concern for circuit reliability [2]. This implies that the logic states of circuit nodes become more easily disturbed by striking-particles in silicon, causing data corruptions, execution errors, or even system crashes. Therefore, integrated circuits in aerospace applications and even terrestrial medical devices require novel designs for efficient radiation tolerance [3].

Single-event upset (SEU), single-event double-upset (SEDU), and single-event transient (SET) are the typical types of soft errors for low-orbit aerospace applications and even terrestrial medical devices. In deep-submicron technologies, the strike of a particle can invalidly change the logic state of a single node in a storage cell, resulting in an SEU. However, in the advanced nano-scale CMOS technologies, the strike of a particle can simultaneously change the logic states of a node pair, resulting in an SEDU. This may also result in a transient pulse at the output of a logic gate in a combinational circuit, resulting in an SET. If an SET pulse propagates through logical gates and arrives at a downstream storage cell, it may be captured by the cell [4]. Like SEUs and SEDUs, SETs can also cause data corruptions, execution errors, or even system crashes. Therefore, it is crucial to propose novel storage cells that are robust against SEUs, SEDUs, and SETs, especially for low-orbit aerospace applications and even terrestrial medical devices that face to moderate radiation effects.

Many novel schemes have been proposed to effectively tolerate SEUs [5]–[18]. Using redundant hold nodes or techniques such as transistor resizing and dual-modular

<sup>0018-9251 © 2020</sup> IEEE.

redundancy, most of these schemes can robustly retain values against SEUs. Note that, using temporal redundancy, some of these schemes are also SET-pulse filterable, especially for the latch designs in [14]–[16], and [18]. However, SEU and/or SET hardening only are not sufficient for low-orbit aerospace applications. It has been reported that ever-increasing integration scale, ever-decreasing transistor sizes, and ever-lowering supply voltages can allow striking-particle induced single-event charge collection to affect double nodes and cause SEDUs [19]. In [20], it is reported that SEDUs are becoming more prominent and the soft error rate of circuits and systems caused by SEDUs is rising. Hence, existing SEU and/or SET hardened schemes are not robust, making them not applicable to low-orbit aerospace applications.

Many state-of-the-art schemes have been proposed to effectively tolerate SEDUs [21]-[28]. Enlarging transistors seems a feasible method to tolerate SEDUs, but the weak node pairs can nevertheless be flipped especially when the energy of the radiation particle is high. Similarly, layoutbased solutions such as well isolation and node spacing increase can also make a circuit SEDU tolerant, but these techniques can increase the complexity of integrated circuit designs [25]. Hence, an efficient way to tolerate SE-DUs relies on the radiation hardening by design (RHBD) technique using multiple-modular redundancy or redundant hold nodes. Despite its efficiency, this technique suffers from severe problems in terms of SEDU self-recoverability, SET pulse filterability, and cost effectiveness. Moreover, although some triple-node upset tolerant latches have been proposed [29]-[31], these designs are mainly used for applications that have to face very harsh radiation environments. Online self-recoverability is crucial for aerospace applications as indicated in [30], and this motivates us to provide the SEDU self-recoverability of our proposed latch designs.

In this article, an SEDU self-recoverable and SET pulse filterable (DURTPF) latch design is first proposed. To the best of our knowledge, the latch is the first ever latch that is SEDU self-recoverable and SET pulse filterable. The DURTPF latch mainly employs eight mutually feedingback C-elements (CEs) and a Schmitt-trigger (ST), making the latch not only SEDU self-recoverable but also SET pulse filterable under moderate striking-particle energy. Second, to harden against some particles that have higher energy, an enhanced version of DURTPF, namely a DURTPF-EV latch, is proposed using seven mutually feeding-back CEs including an input-split ST (ISST). The ISST is created through splitting the original input of the ST into two inputs, making the ISST behave not only as an ST but also as a CE. Simulation results demonstrate the SEDU selfrecoverability and SET pulse filterability of the proposed latches under moderate and higher striking-particle energy, respectively. Moreover, the DURTPF-EV latch consumes less power due to the use of a few transistors and the clockgating (CG) technology, making the latch more suitable for low power and low-orbit aerospace applications.

The contribution of this article can be summarized as follows.

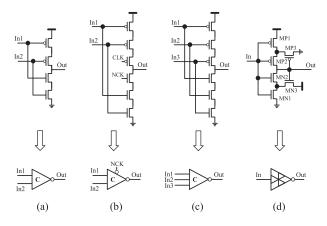

Fig. 1. Widely used components for radiation hardened latch designs.(a) Two-input C-element. (b) Clock gating based two-input C-element.(c) three-input C-element. (d) Schmitt trigger.

- We first propose a DURTPF latch that allows both SEDU self-recoverability and SET pulse filterability using several CEs and an ST, in the case of moderate striking-particle energy.

- We then propose an enhanced version of the latch (DURTPF-EV) that allows both SEDU selfrecoverability and SET pulse filterability using several CEs and an ISST, in the case of higher strikingparticle energy.

- 3) Using the CG technology, the power dissipation of the two proposed latches is low. Using a few transistors, the power dissipation of the enhanced DURTPF-EV latch is much lower.

The rest of the article is organized as follows. Section II reviews previous hardened latch designs. Section III presents the schematics, working principles and validations of the proposed DURTPF and DURTPF-EV latches, respectively. Section V quantitatively shows the overhead comparison results. Finally, Section V concludes this article.

#### II. PREVIOUS HARDENED LATCH DESIGNS

Fig. 1 shows the widely used components of many hardened latch designs. A two-input CE behaves as an inverter if its inputs are identical and it retains its previous value if its inputs become different. As for a CG based two-input C-element, its behavior can also be controlled by system clock (CLK) and negative system clock (NCK) signals. We will discuss the ST in the following section.

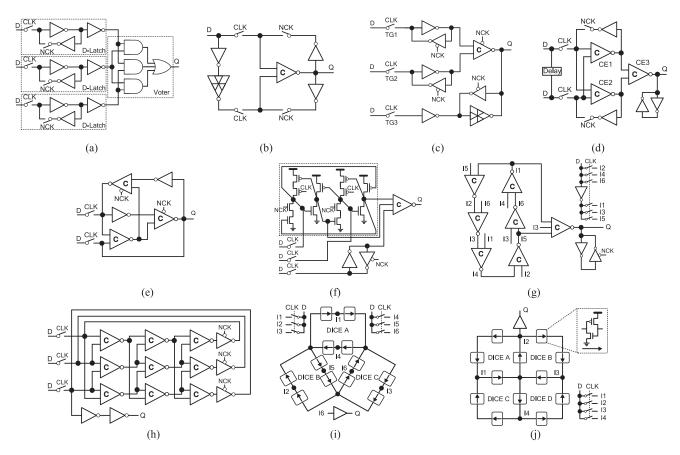

Fig. 2 shows the schematics of the representative SEU, SEDU, and/or SET hardened latch designs. The TMR latch in Fig. 2(a) uses three traditional D-latches and a voter to tolerate SEUs. However, the latch cannot tolerate SEDUs and SET pulses. The DET-SEHP latch [14] in Fig. 2(b) mainly uses an ST to filter SET pulses and a CE feeding back to its inputs to tolerate SEUs. However, if there is an SEU at Q or an SEDU at the inputs of the CE, the latch will retain an invalid value. The LCHR latch [15] in Fig. 2(c) employs three keepers feeding a CE to tolerate SEUs and uses an ST to filter SET pulses. However, if there is an

Fig. 2. Schematics of the previous hardened latch designs. (a) TMR. (b) DET-SEHP [14]. (c) LCHR [15]. (d) FERST-EV [16]. (e) RFC [17]. (f) CLCT [24]. (g) DNCS [25]. (h) NTHLTCH [26]. (i) DeltaDICE [27]. (j) DONUT [28].

SEDU at the inputs of the CE, the latch cannot tolerate it. The FERST-EV latch [16] in Fig. 2(d) mainly employs temporal redundancy to filter SET pulses and uses two interlocked feedback loops connecting to CE3 to tolerate SEUs. However, if there is an SEDU at the inputs of CE3, the latch cannot tolerate it. The RFC latch [17] in Fig. 2(e) employs three interlocked and mutually feeding-back CEs to achieve SEU self-recoverability. However, if the outputs of the two CEs are flipped due to an SEDU, the latch will retain an invalid value. In addition, the latch cannot filter SET pulses.

The CLCT latch [24] in Fig. 2(f) mainly uses a CG-based DICE cell [32] and a keeper connecting to a three-input CE to tolerate SEDUs. However, there are many node pairs that cannot self-recover from SEDUs in the latch and the latch cannot filter SET pulses. As shown in Fig. 2(g), using a feedback loop connecting to a three-input CE, the DNCS latch [25] tolerates SEDUs. However, like the CLCT latch, the latch cannot provide SEDU self-recoverability and SET pulse filterability. The NTHLTCH latch [26] in Fig. 2(h) mainly employs nine two-input CEs and three CG based inverters to achieve SEDU self-recoverability. However, the latch cannot filter SET pulses. The DeltaDICE latch [27] in Fig. 2(i) uses three interlocked DICE cells to achieve SEDU self-recoverability. However, the latch has the same drawbacks compared with the DONUT latch that will be

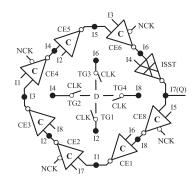

Fig. 3. Circuit schematic of the proposed DURTPF latch design.

described here. The DONUT latch [28] in Fig. 2(j) comprises four interconnected DICE cells to provide enough redundant nodes to ensure SEDU self-recoverability. However, the latch cannot filter SET pulses and has large power dissipation due to more current competition between many internal nodes.

#### III. PROPOSED LATCH DESIGNS

#### A. Proposed DURTPF Latch

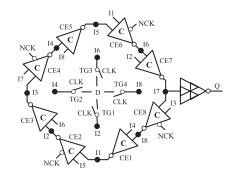

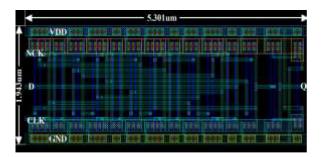

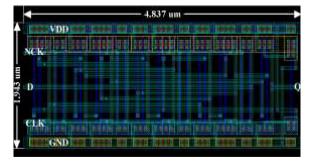

The circuit schematic of our proposed DURTPF latch design is depicted in Fig. 3. Fig. 4 shows the layout of the

Fig. 4. Layout of the proposed DURTPF latch design.

latch. It can be seen that it is constructed from eight twoinput CEs (CE1 to CE8), four transmission gates (TG1 to TG4), and one ST at the output stage of the latch. Note that, CE2, CE4, CE6, and CE8 are CG-based CEs. In the latch, D is the input, I1 to I8 are the internal nodes, and Q is the output, respectively.

When CLK is high and NCK is low, the transmission gates are ON and the latch works in transparent mode. In this mode, all clock-signal controlled transistors in the CGbased CEs are OFF. It can be seen from Fig. 3 that the inputs of both CE1 and CE5 are driven by D through TG2 and TG4, respectively; thus, the outputs of CE1 and CE5 can be known. Similarly, the outputs of CE3 and CE7 can be known. Therefore, we can get the output of any CE among CE1, CE3, CE5, and CE7.

It can be seen from Fig. 3 that the inputs of CE2 are driven by the outputs of CE1 and CE5; however, the output of CE2 is blocked using the CG technology. This avoids current competition at the output of CE2 so as to save power dissipation. Similarly, the outputs of CE4, CE6, and CE8 are blocked to save power dissipation. On the other hand, since the output of CE7 feeds the ST at the output stage of the latch, we can get the output of the latch and thus all the transistors in the latch are biased properly.

The reason why the latch is SET pulse filterable when working in transparent mode is described as follows. If an SET pulse arrives at D, the pulse will be first reversed by CE7 and then will be filtered by the ST. Here, as an example, we consider the case of a positive SET pulse (low-highlow). The transistors MP1, MP2, and MN3 in Fig. 1(d) are precharged and biased properly. As a result, when D changes from low to high (the rise stage), the output of the ST will not change until the drain of MN1 is discharged from high to low. This needs a period of time especially when the aspect ratios of MN1 and MN3 are large. Within that period of time, D may change from high to low (the fall stage), and the output of the ST will not change, i.e., the SET pulse is masked/filtered.

When CLK is low and NCK is high, the transmission gates are OFF and the latch switches to hold mode. In this mode, all clock-signal controlled transistors in the CGbased CEs are ON. Thus, the outputs of the CG-based CEs are prevented from being driven by D through the transmission gates and instead they are driven by the CG-based CEs. This way, all the interlocked feedback loops in the latch are constructed to effectively keep values. The feedback rule for the CEs is as follows. The output of any CE in the ordered and circulated CE list <CE1, CE2, CE3, CE4, CE5, CE6, CE7, CE8> is fed back to both one input of the next CE and one input of the previously third CE. Finally, Q is robustly driven by the output of CE7 through the ST to keep values.

In the presence of an SEU for the latch when it works in hold mode, there are totally nine cases because an SEU may affect any of the internal nodes I1 to I8 as well as the output of the latch. Here, as an example, we consider the case where an SEU affects I1 resulting in a glitch. According to the CEs' feedback rule, the glitch can propagate to one input of CE2 as well as one input of CE6, but CE2 and CE6 can intercept the glitch. On the other hand, because the SEU cannot affect the inputs of CE1, I1 can restore back the correct value through the correct inputs of CE1. This way, the internal nodes of the latch can restore back the correct values from any SEU, and finally the output of the latch can restore back the correct value through the ST. Therefore, all nodes in the latch keep correct values, i.e., the latch is SEU self-recoverable.

In the presence of an SEDU for the latch when it works in hold mode, any node pair should be considered. In the circular structure of Fig. 3, since any two of the internal nodes I1 to I8 can be affected by an SEDU, there are totally  $C_8^2 = 28$  cases in the presence of an SEDU. On the other hand, since the output of the latch and one of the eight internal nodes I1 to I8 can also be affected by an SEDU, there are eight more cases in the presence of an SEDU. However, since the latch is SEU self-recoverable, as for the just mentioned eight more cases in the presence of an SEDU, the internal node can first self-recover and the output node can then self-recover from the SEDU. Hence, the latch is SEDU self-recoverable for the eight cases and we only have to prove that the circular structure of the latch is SEDU self-recoverable (totally 28 cases).

As for two adjacent CEs in the circular structure of the latch, if we denote the node distance between their outputs by  $\lambda$ , we can get all output-node distances between CEs as and only as  $\lambda$ ,  $2\lambda$ ,  $3\lambda$ , and  $4\lambda$ . This is because the CEs are ordered, circulated, and symmetrical as presented in Fig. 3. Hence, we only need four indicative node pairs such as <II, I2>, <II, I3>, <II, I4>, and <II, I5> for the 28 cases in the presence of an SEDU to prove the self-recoverability for the latch.

In the presence of an SEDU for <I1, I2> resulting in glitches, according to the above-mentioned CEs' feedback rule, the glitch at I1 can propagate to one input of CE2 and one input of CE6, the glitch at I2 can propagate to one input of CE3 and one input of CE7; however, all the other one or two inputs of all the other CEs are not affected by the SEDU. Since a CE can intercept a glitch although one of its inputs is affected, CE6 and CE7 can intercept the glitches. Thus, the outputs of them, i.e., I6 and I7, are correct. Meanwhile, since I6 is fed back to one input of CE3, the output (I3) of CE3 is correct as well. On the other hand, since the outputs of CE3 and CE4 are correct, I1 can restore back to the correct value through CE1, and finally I2 can restore back

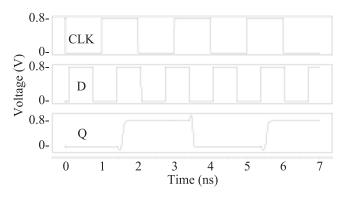

Fig. 5. Simulation results of the DURTPF latch considering error free case.

to the correct value through CE2. Therefore, the latch can self-recover from the SEDU at <11, 12>. Similarly, it can be easily known that in the presence of an SEDU for <11, 13> or <11, 14> resulting in glitches, they can also self-recover from the SEDU.

In the presence of an SEDU for <11, 15> resulting in glitches, if the striking-particle has moderate energy, the node pair can still self-recover from the SEDU. This is because the striking-particle induced SEDU only behaves as transient pulses at 11 and 15, and CE2 and CE6 can intercept the small glitches. However, if the striking-particle has higher energy causing an SEDU at the node pair <11, 15>, the node pair can be flipped causing invalid value retention, since 11 and 15 are the inputs of CE2 and CE6 and the error can propagate to I2 and I6, and finally, to Q through CE3, CE7, and the ST. This case motivates us to propose an enhanced latch version to self-recover from SEDUs for these four indicative node pairs when the striking-particle energy is higher. This enhanced version will be presented in the following section.

As discussed earlier, the latch can properly operate in transparent mode and can retain values in hold mode. Moreover, the latch can filter SET pulses in transparent mode due to the employment of the ST. When the striking-particle has moderate energy, the latch can self-recover from SEDUs in hold mode.

The DURTPF latch was implemented with an advanced 22 nm CMOS technology and the validations for the SET pulse filterability and SEDU self-recoverability of the latch using Synopsys HSPICE tool were performed. The supply voltage was set to 0.8 V. The working temperature was set to room temperature.

The transistor sizes for the latch design are as follows: a) for the normal CEs, the PMOS transistor had W/L = 130/22 nm, the NMOS transistor had W/L = 40/22 nm; b) for the CG based CEs, the PMOS transistor had W/L = 130/22 nm, the NMOS transistor had W/L = 80/22 nm; c) for the ST, the PMOS transistor had W/L = 120/44 nm, the NMOS transistor had W/L = 120/44 nm.

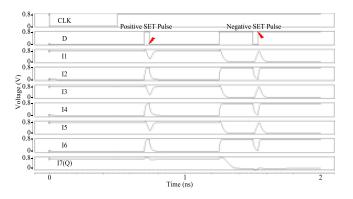

To verify the normal operation of the proposed DURTPF latch, the simulation for the latch considering the error free

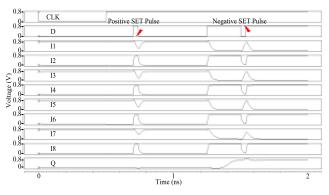

Fig. 6. Simulation results of the DURTPF latch considering the negative and positive SET pulses.

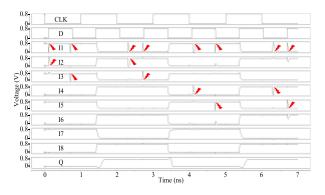

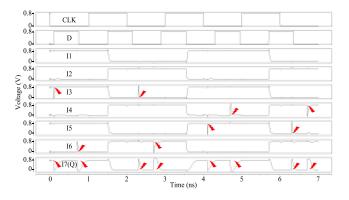

Fig. 7. Simulation results of the DURTPF latch considering SEDUs at key node pairs <11, 12>, <11, 13>, <11, 14>, and <11, 15>.

case was performed as presented in Fig. 5. The simulation results show that the normal operation of the latch in transparent and hold mode is similar to that of a traditional D-latch.

To verify the SET pulse filterability of our proposed DURTPF latch, Fig. 6 shows the simulation results of the DURTPF latch considering the representative negative and positive SET pulses. Note that Fig. 6 is only illustrated for the filtering ability of the latch, and the filterable-pulse widths will be listed and evaluated in Section IV. It can be seen from Fig. 6 that the injected pulses cause nearly no any effect on Q, i.e., these pulses are filtered by the latch. Therefore, the latch is SET pulse filterable. It should be noted that, to filter higher-energy striking-particle-induced large SET pulses, large transistor sizes and/or D to Q transmission delay should be introduced for latches, which will be introduced in Section IV.

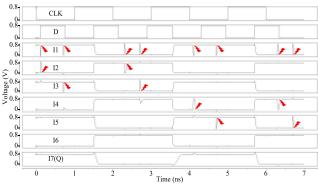

To verify the SEDU self-recoverability of the proposed DURTPF latch, Fig. 7 shows the simulation results considering SEDUs at key node pairs <11, I2>, <11, I3>, <11, I4>, and <11, I5>. As presented in Fig. 7, at 0.3, 0.7, 2.3, 2.7, 4.3, 4.7, 6.3, and 6.7 ns, an SEDU was, respectively, injected at node pairs <11, I2>, <11, I3>, <11, I2>, <11, I3>, <11, I3>, <11, I3>, <11, I2>, <11, I3>, <11, I4>, and <11, I5>, but the node pairs can restore back to the correct values. Therefore, all the key node pairs can self-recover from an SEDU, no matter was the correct value (high or low), i.e., the latch is SEDU self-recoverable for all these key node pairs.

YAN ET AL.: DESIGN OF DOUBLE-UPSET RECOVERABLE AND TRANSIENT-PULSE FILTERABLE LATCHES

Fig. 8. Simulation results of the DURTPF latch considering SEDUs at key node pairs <17, Q>, <16, Q>, <15, Q>, and <14, Q>.

Fig. 9. Circuit schematic of the proposed DURTPF-EV latch design.

On the other hand, as for a node pair including the output of the latch and one of the eight internal nodes I1 to I8, Fig. 8 shows the simulation results for the DURTPF latch considering key node pairs <I7, Q>, <I6, Q>, <I5, Q>, and <I4, Q>. At 0.3, 0.7, 2.3, 2.7, 4.3, 4.7, 6.3, and 6.7 ns, an SEDU was, respectively, injected at node pairs <I7, Q>, <I6, Q>, <I7, Q>, <I6, Q>, <I5, Q>, <I4, Q>, <I5, Q>, and <I4, Q>, and these node pairs can also restore back to the correct values. Therefore, all key node pairs can selfrecover from an SEDU no matter was the correct value (high or low), i.e., the latch is SEDU self-recoverable for all these node pairs. Note that the abovementioned simulations were under moderate striking-particle energy (i.e., the injected erroneous charge is up to 8.0 fC).

In summary, simulation results have demonstrated the SET pulse filterability as well as SEDU self-recoverability of the DURTPF latch under moderate striking-particle energy. In the abovementioned simulations, we used a controllable double-exponential current source model to perform the SET and SEDU injections as in [25] to simulate striking-particles. The time constants of the rise and the fall of the current pulse were set to 0.1 and 3.0 ps, respectively.

#### B. Proposed DURTPF-EV Latch

The circuit schematic of the proposed DURTPF-EV latch is shown in Figs. 9, and Fig. 10 shows the layout of the DURTPF-EV latch. Based on the DURTPF latch, the DURTPF-EV latch is constructed by replacing CE7 in the DURTPF latch with an ISST, and the original ST

Fig. 10. Layout of the proposed DURTPF-EV latch design.

is removed. Moreover, the feedback rule for the CEs and ISST is enhanced in order to achieve the advanced SEDU self-recoverability, i.e., the DURTPF-EV latch can consistently provide the SEDU self-recoverability when the striking-particle energy is higher.

Note that, the ISST is constructed by splitting the input "In" in Fig. 1(d) into two inputs "In1" and "In2," i.e., the gate terminals of the transistors MP1 and MN2 are connected as "In1" and the gate terminals of the transistors MN1 and MP2 are connected as "In2." By this way, the ISST has the functions of both a CE and an ST. The input D and the clock signals CLK and NCK of the DURTPF-EV latch are the same as those of the DURTPF latch, and I7 is reused for the output of the DURTPF-EV latch.

It can be easily seen that, when the DURTPF-EV latch works in transparent mode, its normal working, and SET pulse filtering principles are similar to those of the DURTPF latch. In the presence of an SEU for the DURTPF-EV latch in hold mode, the SEU recovery principle is also similar to that of the DURTPF latch. However, in the presence of an SEDU for the DURTPF-EV latch in hold mode, a total of  $C_8^2 = 28$  node-pair cases must be evaluated to prove that the latch is SEDU self-recoverable under the new feedback rule.

For two adjacent CEs including the ISST, in the circular structure of the latch, similarly, if we denote the node distance between their outputs as  $\lambda$ , we can get all output-node distances as and only as  $\lambda$ ,  $2\lambda$ ,  $3\lambda$ , and  $4\lambda$ . Since the CEs including the ISST are ordered, circulated, and symmetrical as presented in Fig. 9, we only need to consider four indicative node pairs such as <I1, I2>, <I1, I3>, <I1, I4>, and <I1, I5> for the 28 cases in the presence of an SEDU to prove the self-recoverability for the latch.

In the presence of an SEDU for <I1, I2> resulting in glitches, it is obvious that the glitch at I1 can propagate to one input of CE2 and one input of CE4, and the glitch at I2 can propagate to one input of CE3 and one input of CE5. However, all the inputs of all the other CEs or the ISST are not affected by the SEDU. Since a CE can intercept a glitch although one of its inputs is affected, CE3 to CE5 can intercept the glitches and the outputs of them (i.e., I3 to I5) are correct. Since I3 and I5 are fed back to the inputs of CE6, the output (I6) of CE6 is correct as well. This way, I7 and I8 are still correct, making I1 to restore back to the correct value through CE1, and finally, I2 can also restore

Fig. 11. Simulation results of the DURTPF-EV latch considering the negative and positive SET pulses.

back to the correct value through CE2. Therefore, the latch can self-recover from the SEDU at <11, 12>. Similarly, it can be easily found that in the presence of an SEDU for <11, 13> or <11, 14> resulting in glitches, they can also self-recover from the SEDU.

In the presence of an SEDU for <I1, I5> resulting in glitches, it is obvious that the glitch at I1 can propagate to one input of CE2 and one input of CE4, the glitch at I5 can propagate to one input of CE6 and one input of CE8. However, all inputs of all the other CEs are not directly affected by the SEDU. Since a CE can intercept a glitch although one of its inputs is affected, CE2, CE4, CE6, and CE8 can intercept the glitches and the outputs of them (i.e., 12, I4, I6, and I8) are correct. Moreover, I2, I4, I6, and I8 are the inputs of CE1, CE3, CE5, and the ISST, and thus, their outputs I1, I3, I5, and I7 (Q) can restore back to their correct values through CE1, CE3, CE5, and the ISST. Therefore, the latch can self-recover from the SEDU at <11, 15>. Note that the abovementioned analysis in this section still holds true for the case of higher striking-particle energy, and the amount of the injected current charge will be introduced in the following.

As discussed earlier, the latch can properly operate in transparent mode and can retain values in hold mode. In addition, the latch can filter SET pulses in transparent mode and can self-recover from SEDUs in hold mode, i.e., the latch is SEDU self-recoverable and SET pulse filterable. In the following, SEDU simulation results will be shown under the assumption of higher striking-particle energy.

Using all the same design parameters for the DURTPF latch, the DURTPF-EV latch was also implemented. Comprehensive simulation results demonstrate that the normal operation of the DURTPF-EV latch in transparent and hold mode is still similar to that of a traditional D-latch.

Figs. 11–13 show the simulation results considering SETs and SEDUs. It can be seen from Fig. 11 that the DURTPF-EV latch can still effectively filter SET pulses. Note that Fig. 11 is only illustrated for the filtering ability of the DURTPF-EV latch, and the filterable-pulse widths will be listed and evaluated in Section IV. For the SEDU selfrecoverability verification, a striking-particle with higher

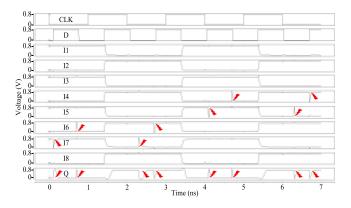

Fig. 12. Simulation results of the DURTPF-EV latch considering SEDUs at key node pairs <II, I2>, <I1, I3>, <I1, I4>, and <I1, I5>.

Fig. 13. Simulation results of the DURTPF-EV latch considering SEDUs at key node pairs <I7, Q>, <I6, Q>, <I5, Q>, and <I4, Q>.

energy (i.e., the smallest injected current charge is about 11.0 fC, which is large enough to simulate the worst case operations for the latch) was assumed. Note that, the verification methodology is the same as that of the DURTPF latch as described in the abovementioned section. Thus, the validation results are directly described here. It can be seen from Figs. 12 and 13 that, the DURTPF-EV latch can effectively self-recover from an SEDU at key node pairs <I1, I2>, <I1, I3>, <I1, I4>, <I1, I5>, <I3, Q>, <I4, Q>, <I5, Q>, and <I6, Q>, respectively, under higher striking-particle energy. Note that, for the sake of brevity, the redundant signal I8 is omitted in Figs. 11 to 13.

#### IV. LATCH COMPARISON AND EVALUATION RESULTS

To make a fair quantitative comparison, the latch designs reviewed in Section II were implemented using the same parameters as the proposed latch designs. Detailed comparison results among the latch designs including ours are presented in Table I, with respect to the average (dynamic and static) power dissipation, D to Q transmission delay (i.e., the average of rise and fall delays of D to Q), silicon area, average filterable-SET-pulse width (AFSW), powerdelay-width product (PDWP), and SET pulse filtering ability (SPFA), respectively. The PDWP and SPFA calculation

YAN ET AL.: DESIGN OF DOUBLE-UPSET RECOVERABLE AND TRANSIENT-PULSE FILTERABLE LATCHES

TABLE I Comparison Results for Alternative SEU/SEDU/SET Hardened Latch Designs

|    | Latch Name | D.f      | Overhead |        |                       |           |        |          |

|----|------------|----------|----------|--------|-----------------------|-----------|--------|----------|

| #  |            | Ref.     | Power    | Delay  | 10 <sup>2</sup> ×Area | AFSW (ps) | PDWP   | SPFA (%) |

|    |            |          | (µW)     | (ps)   | (µm <sup>2</sup> )    |           |        |          |

| 1  | TMR        | -        | 1.51     | 47.67  | 13.52                 | -         | 71.98  | -        |

| 2  | DET-SEHP   | [14]     | 1.52     | 154.52 | 5.89                  | 118.41    | 54.89  | 76.63    |

| 3  | LCHR       | [15]     | 0.98     | 111.02 | 7.93                  | 39.08     | 70.50  | 35.20    |

| 4  | FERST-EV   | [16]     | 1.25     | 73.84  | 6.15                  | 43.42     | 38.03  | 58.80    |

| 5  | RFC        | [17]     | 0.45     | 4.58   | 4.82                  | -         | 2.06   | -        |

| 6  | CLCT       | [24]     | 0.65     | 31.68  | 5.85                  | -         | 20.59  | -        |

| 7  | DNCS       | [25]     | 1.72     | 63.12  | 10.21                 | -         | 108.57 | -        |

| 8  | NTHLTCH    | [26]     | 2.87     | 16.19  | 12.42                 | -         | 46.47  | -        |

| 9  | DeltaDICE  | [27]     | 1.95     | 7.09   | 14.32                 | -         | 13.83  | -        |

| 10 | DOUNT      | [28]     | 2.96     | 20.24  | 10.32                 | -         | 59.91  | -        |

| 11 | DURTPF     | Proposed | 0.93     | 135.65 | 12.83                 | 78.19     | 53.44  | 57.64    |

| 12 | DURTPF-EV  | Proposed | 0.82     | 109.83 | 12.08                 | 48.57     | 50.23  | 44.22    |

formulas are given as follows:

$$PDWP = Power \times (Delay - Width)$$

(1)

$$SPFA = (Width/Delay) \times 100\%.$$

(2)

In the abovementioned formulas, power is the average power dissipation, delay is D to Q transmission delay, and width is the AFSW whose value is not available for SETnot-filterable latch designs. It can be seen that, among the same type latch designs (e.g., SET pulse filterable ones), a smaller PDWP, and/or a larger SPFA is better.

It can be seen from Table I that, in order to ensure SEDU self-recoverability and SET pulse filterability, larger silicon area is needed for the proposed DURTPF latch. However, compared with SET pulse filterable (second to fourth) or the SEDU self-recoverable (eighth to tenth) latches, our proposed latches have the smallest power dissipation due to the use of the CG technology. As for the DURTPF-EV latch, the delay is smaller than the DURTPF latch since a few transistors are employed between the input and the output of the latch. Besides, the SPFAs of the FERST-EV latch and the DET-SHEP latch are large due to the multiplelevel filtering mechanism of CEs; however, the SPFA of our proposed latch designs is comparable to that of most of the SET filterable latches.

To make further detailed quantitative comparisons, the relative overhead in terms of power ( $\Delta$ Power), delay  $(\Delta Delay)$ , area  $(\Delta Area)$ , and PDWP  $(\Delta PDWP)$  among the reference latch designs compared with our designs have been listed in Tables II–V, and the calculation formula is given as follows:

#### $\Delta = (\text{Compared} - \text{Proposed}) / \text{Compared} \times 100\%.$ (3)

As for the DURTPF latch, it can be seen from Table II that, to perform both SEDU and SET hardening, compared with the SEDU self-recoverable latches, our latch consumes 5.74% extra silicon area on average. However, owing to the employment of the CG technology, our latch saves about 62.83% power dissipation on average, and these compared 3938

TABLE II Relative Overhead of SEDU Self-Recoverable Latch Designs Compared With the DURTPF Latch

| Latch<br>Name                | ΔPower<br>(%) | ΔDelay<br>(%) | ΔArea<br>(%) |

|------------------------------|---------------|---------------|--------------|

| NTHLTCH [26]                 | 67.60         | -             | -3.30        |

| DeltaDICE [27]               | 52.31         | -             | 10.41        |

| DONUT [28]                   | 68.58         | -             | -24.32       |

| Average<br>(Savings of ours) | 62.83         | -             | -5.74        |

TABLE III Relative Overhead of SET Pulse Filterable Latch Designs Compared With the DURTPF Latch

| Latch<br>Name                | ΔPower<br>(%) | ΔDelay<br>(%) | ΔArea<br>(%) |

|------------------------------|---------------|---------------|--------------|

| DET-SEHP [14]                | 38.82         | 12.21         | -117.83      |

| LCHR [15]                    | 5.10          | -22.19        | -61.79       |

| FERST-EV [16]                | 25.60         | -83.71        | -108.62      |

| Average<br>(Savings of ours) | 23.17         | -31.23        | -96.08       |

TABLE IV Relative Overhead of SEDU Self-Recoverable Latch Designs Compared With the DURTPF-EV Latch

| Latch<br>Name                | ΔPower<br>(%) | ΔDelay<br>(%) | <b>ΔArea</b><br>(%) |

|------------------------------|---------------|---------------|---------------------|

| NTHLTCH [26]                 | 71.43         | -             | 2.74                |

| DeltaDICE [27]               | 57.95         | -             | 15.64               |

| DONUT [28]                   | 72.30         | -             | -17.05              |

| Average<br>(Savings of ours) | 67.23         | -             | 0.44                |

latches are not SET filterable. Note that the  $\Delta$ Delay is not suitable for comparisons since these latches and ours are not of the same type. Table III presents comparisons of SET pulse filterable latches. It can be seen from Table III that, compared with the SET pulse filterable latches, all the average data of our DURTPF latch are not bad except for  $\triangle$ Area since our latch can achieve not only SEDU self-recoverability under moderate striking-particle energy IEEE TRANSACTIONS ON AEROSPACE AND ELECTRONIC SYSTEMS VOL. 56, NO. 5 OCTOBER 2020

TABLE V Relative Overhead of SET Pulse Filterable Latch Designs Compared With the DURTPF-EV Latch

| Latch<br>Name                | ΔPower<br>(%) | ΔDelay<br>(%) | ΔArea<br>(%) |

|------------------------------|---------------|---------------|--------------|

| DET-SEHP [14]                | 46.05         | 28.92         | -105.09      |

| LCHR [15]                    | 16.33         | 1.07          | 52.33        |

| FERST-EV [16]                | 34.40         | -48.74        | -96.42       |

| Average<br>(Savings of ours) | 32.26         | -6.25         | -84.61       |

TABLE VI Simulation Results using Differently Sized ST for the DURTPF Latch

| ST Tran-<br>sistor Sizes<br>(Length,<br>Width)<br>(nm) | Power<br>(uW) | Delay<br>(ps) | 10 <sup>2</sup> ×Area<br>(μm²) | AFSW<br>(ps) | SPFA<br>(%) |

|--------------------------------------------------------|---------------|---------------|--------------------------------|--------------|-------------|

| (44,120)                                               | 0.93          | 135.65        | 12.83                          | 78.19        | 57.64       |

| (88,120)                                               | 1.03          | 279.23        | 16.00                          | 127.56       | 45.68       |

| (44,240)                                               | 1.28          | 163.97        | 16.00                          | 101.88       | 62.13       |

| (88,240)                                               | 1.46          | 316.38        | 22.33                          | 166.32       | 52.57       |

but also SET filterability at the cost of extra silicon area. In summary, we have introduced redundant silicon area to achieve high reliability and low power for the proposed DURTPF latch.

As for the DURTPF-EV latch, it can be seen from Table IV that, compared with the SEDU self-recoverable latches, the DURTPF-EV latch saves about 0.44% silicon area on average. In addition, due to the employment of the CG technology and a few transistors, the DURTPF-EV latch saves about 67.23% power dissipation on average. However, these SEDU self-recoverable latches are not SET filterable. Moreover, it can be seen from Table V that, compared with the SET pulse filterable latches, all the simulation data of the DURTPF-EV latch are not bad except for  $\triangle$ Area since the SEDU self-recoverability and the SET filterability of the DURTPF-EV latch are still at the cost of extra silicon area. The increase in silicon area may make our latch vulnerable to soft errors. However, our latch can online self-recover from SEUs and SEDUs and can filter SET pulses. In summary, we have introduced redundant silicon area to achieve high reliability and low power for our proposed latches. Meanwhile, compared with the DURTPF latch, the DURTPF-EV latch can save more power dissipation, delay, and PDWP, making the DURTPF-EV latch more suitable for low-orbit aerospace applications that require high reliability and low cost. Note that propagation-induced pulse broadening (PIPB) not occur through simulations in the proposed latches. PIPB mainly occur in combinational logic circuits [33].

ST and ISST can filter SET pulses, but different transistor sizes of ST and ISST can cause different SET-filtering ability and latch overhead. Tables VI and VII show the simulation results using differently sized ST and ISST for

TABLE VII Simulation Results Using Differently Sized ISST for the DURTPF-EV Latch

| ISST<br>Transistor<br>Sizes<br>(Length,<br>Width)<br>(nm) | Transistor<br>Sizes Power<br>(Length, (uW)<br>Width) |        | 10 <sup>2</sup> ×Area<br>(μm²) | AFSW<br>(ps) | SPFA<br>(%) |

|-----------------------------------------------------------|------------------------------------------------------|--------|--------------------------------|--------------|-------------|

| (44,120)                                                  | 0.82                                                 | 109.83 | 12.08                          | 48.57        | 44.22       |

| (88,120)                                                  | 0.86                                                 | 274.78 | 15.25                          | 86.95        | 31.64       |

| (44,240)                                                  | 1.04                                                 | 108.62 | 15.25                          | 56.46        | 51.98       |

| (88,240)                                                  | 1.14                                                 | 264.47 | 21.59                          | 101.83       | 38.50       |

the proposed DURTPF and DURTPF-EV latches, respectively. It can be seen from these tables that increasing ST/ISST transistor sizes can provide large AFSW especially when only the width parameters of transistors are enlarged. However, the overhead in terms of power, delay, and area has to be introduced and the SPFA cannot be significantly enhanced. Therefore, the small transistor sizes of the ST and ISST as indicated in Tables VI and VII can provide a better balance between reliability and overhead of the proposed latches.

#### V. CONCLUSION

Technology scaling has made soft errors, such as SEUs, SEDUs, and SETs, a serious concern in advanced nanoscale CMOS technologies. However, most of the typical latch designs are either not hardened simultaneously against SEDUs and SETs, or they incur excessive overhead especially in terms of power dissipation, making them not suitable for low-orbit aerospace applications where both high reliability and low cost are required. This article has proposed a DURTPF latch design, which is SET pulse filterable and SEDU self-recoverable in the case of moderate striking-particle energy. This article has further proposed an enhanced version of DURTPF, namely DURTPF-EV, which is SEDU self-recoverable even in the case of higher strikingparticle energy. Comprehensive simulations have demonstrated the SET pulse filterability, SEDU self-recoverability, and low-power consumption of the proposed latch designs at the cost of moderate silicon area overhead. Compared with DURTPF, DURTPF-EV is more robust and low power, making it more suitable for low-orbit aerospace applications that require high reliability and low cost.

#### REFERENCES

- M. J. Gadlage, A. H. Roach, A. R. Duncan, A. M. Williams, D. P. Bossev, and M. J. Kay Soft errors induced by high-energy electrons *IEEE Trans. Device Mater. Rel.*, vol. 17, no. 1, pp. 157–162, Mar. 2017.

S. Anjan and B. Maryam

- 2] S. Anjan and B. Maryani Robust soft error tolerant CMOS latch configurations *IEEE Trans. Comput.*, vol. 65, no. 9, pp. 2820–2834, Sep. 2016.

YAN ET AL.: DESIGN OF DOUBLE-UPSET RECOVERABLE AND TRANSIENT-PULSE FILTERABLE LATCHES

- [3] G. Hilson Medical devices require radiation-tolerant memory EE[Times, 2014. [Online]. Available: https://www.eetimes. com/document.asp?doc\_id = 1323022. Accessed: Jan. 26, 2019.

- S. Cai *et al.* Single event transient propagation probabilities analysis for nanometer CMOS circuits

J. Electron. Testing, vol. 35, no. 2, pp. 163–172, 2019.

- [5] C. Peng *et al.* Radiation-hardened 14T SRAM bitcell with speed and power optimized for space application

*IEEE Trans. Very Large Scale Integr. Syst.*, vol. 27, no. 2, pp. 407–415, Feb. 2019.

- [6] M. Alioto, E. Consoli, and G. Palumbo Variations in nanometer CMOS flip-flops: part I - Timing and impact of process variations *IEEE Trans. Circuits Syst. I: Reg. Papers*, vol. 62, no. 8, pp. 2035–2043, Jan. 2015.

- J. Shah, D. Nairn, and M. Sachdev

A 32 kb macro with 8T soft error robust, SRAM cell in 65-nm CMOS

*IEEE Trans. Nuclear Sci.*, vol. 62, no. 3, pp. 1367–1374, Jun. 2015.

- [8] M. Omana, D. Rossi, and C. Metra High-performance robust latches *IEEE Trans. Comput.*, vol. 59, no. 11, pp. 1455–1465, Jan. 2010.

- S. Mitra, M. Zhang, N. Seifert, T. Mak, and K. Kim Built-in soft error resilience for robust system design In *Proc. Int. Conf. Integr. Circuit Design Techn.*, Jun. 2007, pp. 1–6.

- [10] C. Peng, L. Guan, W. Lu, X. Wu, and X. Ji Read/write margin enhanced 10T SRAM for low voltage application *IEICE Electron. Exp.*, vol. 13, no. 12, pp. 1–10, Jun. 2016.

- H. Wang *et al.* An area efficient stacked latch design tolerant to SEU in 28 nm FDSOI technology

*IEEE Trans. Nuclear Sci.*, vol. 63, no. 6, pp. 3003–3009, Nov. 2016.

- Z. Huang, H. Liang, and S. Hellebrand A high performance SEU tolerant latch *J. Electron. Testing*, vol. 31, no. 4, pp. 349–359, Jul. 2015.

- [13] C. Peng *et al.* A radiation harden enhanced Quatro (RHEQ) SRAM cell *IEICE Electron. Exp.*, vol. 14, no. 18, pp. 1–12, Sep. 2017.

- [14] H. Alidash and V. Oklobdzija Low-power soft error hardened latch *J. Low Power Electron.*, vol. 6, no. 1, pp. 218–226, Jan. 2010.

[15] C. Qi *et al.*

- Low cost and highly reliable radiation hardened latch design in 65 nm CMOS technology *Microelectron. Rel.*, vol. 55, pp. 863–872, Apr. 2015.

- M. Fazeli *et al.* Low energy single event upset/single event transient-tolerant latch for deep subMicron technologies

*IET Comput. Digit. Techn.*, vol. 3, no. 3, pp. 289–303, Oct. 2009.

- [17] A. Yan, H. Liang, Z. Huang, C. Jiang, and M. Yi A self-recoverable, frequency-aware and cost-effective robust latch design for nano-scale CMOS technology *IEICE Trans. Electron.*, vol. 98, no. 12, pp. 1171–1178, Dec. 2015.

- [18] R. Rajaei, M. Tabandeh, and M. Fazeli Low cost soft error hardened latch designs for nano-scale CMOS technology in presence of process variation *Microelectron. Rel.*, vol. 53, pp. 912–924, Mar. 2013.

- [19] R. Rajaei, B. Asgari, M. Tabandeh, and M. Fazeli Design of robust SRAM cells against single-event multiple effects for nanometer technologies *IEEE Trans. Device Mater. Rel.*, vol. 15, no. 99, pp. 429–436, Sep. 2015.

- [20] J. Black, P. Dodd, and K. Warren Physics of multiple-node charge collection and impacts on single-event characterization and soft error rate prediction *IEEE Trans. Nuclear Sci.*, vol. 60, no. 3, pp. 1836–1851, Jun. 2013.

- [21] A. Yan, Y. Hu, J. Song, and X. Wen Single-event double-upset self-recoverable and single-event transient pulse filterable latch design for low power applications

- In Proc. IEEE Conf. Exhib. Des., Autom. Test Eur., Mar. 2019, pp. 1–6.

- [22] W. Wei, K. Namba, Y. Kim, and F. Lombardi A novel scheme for tolerating single event/multiple bit upsets (SEU/MBU) in non-volatile memories *IEEE Trans. Comput.*, vol. 65, no. 3, pp. 781–790, Mar. 2016.

[23] N. Eftaxiopoulos, N. Axelos, and K. Pekmestzi

- DIRT latch: A novel low cost double node upset tolerant latch *Microelectron. Rel.*, vol. 68, pp. 57–68, Nov. 2017.

- [24] X. Hui and Z. Yun Circuit and layout combination technique to enhance multiple nodes upset tolerance in latches *IEICE Electron. Exp.*, vol. 12, no. 9, pp. 1–7, May 2015.

- [25] K. Katsarou and Y. Tsiatouhas Soft error interception latch: double node charge sharing SEU tolerant design *Electron. Lett.*, vol. 51, no. 4, pp. 330–332, Feb. 2015.

- Y. Li *et al.* Double node upsets hardened latch circuits

*J. Electron. Testing*, vol. 31, no. 1, pp. 537–548, Nov. 2015.

N. Eftaxiopoulos, N. Axelos, G. Zervakis, K. Tsoumanis, and K.

- Pekmestzi Delta DICE: A double node upset self-recoverable latch In Proc. Int. Midwest Symp. Circuits Syst., Aug. 2015, pp. 1–4.

- [28] N. Eftaxiopoulos, N. Axelos, and K. Pekmestzi DONUT: A double node upset tolerant latch In *Proc. IEEE Comput. Soc. Annu. Symp. VLSI*, Jul. 2015, pp. 509–514.

- [29] A. Yan et al. Novel low cost, double-and-triple-node-upset-tolerant latch designs for nano-scale CMOS *IEEE Trans. Emerg. Topics Comput.*, to be published, doi: 10.1109/TETC.2018.2871861.

- [30] A. Yan et al. Design of a triple-node-upset self-recoverable latch for aerospace applications in harsh radiation environments *IEEE Trans. Aerosp. Electron. Syst.*, vol. 56, no. 2, pp. 1163– 1171, Apr. 2020.

- [31] A. Watkins and S. Tragoudas Radiation hardened latch designs for double and triple node upsets *IEEE Trans. Emerg. Topics Comput.*, to be published, doi: 10.1109/TETC.2017.2776285.

- [32] T. Calin, M. Nicolaidis, and R. Velazco Upset hardened memory design for submicron CMOS technology *IEEE Trans. Nuclear Sci.*, vol. 43, no. 6, pp. 2874–2878, Dec. 1996.

- [33] A. Yan, Y. Ling, K. Yang, Z. Chen, and M. Yi Aging-temperature-and-propagation induced pulsebroadening aware soft error rate estimation for nano-scale CMOS In *Proc. IEEE Asian Test Symp.*, 2018, pp. 1–6.