# Digital test of ZigBee transmitters: Validation in industrial test environment

Thibault Vayssade, Florence Azaïs, Laurent Latorre, François Lefèvre

#### ▶ To cite this version:

Thibault Vayssade, Florence Azaïs, Laurent Latorre, François Lefèvre. Digital test of ZigBee transmitters: Validation in industrial test environment. DATE 2021 - 24th Design, Automation and Test in Europe Conference and Exhibition, Feb 2021, Grenoble, France. pp.396-401, 10.23919/DATE51398.2021.9474090. lirmm-03426209

### HAL Id: lirmm-03426209 https://hal-lirmm.ccsd.cnrs.fr/lirmm-03426209

Submitted on 12 Nov 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Digital test of ZigBee transmitters: Validation in industrial test environment

Thibault Vayssade

(1) LIRMM

Univ. Montpellier / CNRS

Montpellier, France

(2) NXP Semiconductors

Caen, France

Florence Azaïs

LIRMM

Univ. Montpellier / CNRS

Montpellier, France

Laurent Latorre

LIRMM

Univ. Montpellier / CNRS

Montpellier, France

François Lefèvre

NXP Semiconductors

Caen, France

Abstract— This paper presents the validation of a low-cost solution for production test of ZigBee transmitters in industrial environment. The solution relies on 1-bit acquisition of a 2.4GHz signal with a standard digital ATE channel using harmonic sampling. Dedicated post-processing algorithms are then applied on the low-frequency binary vector captured by the ATE to retrieve the RF signal characteristics and implement the tests specified by IEEE Std 802.15.4. Experimental results collected on more than 1.5 thousand pieces of a ZigBee transceiver from NXP Semiconductors are presented.

Keywords— RF test; digital ATE; Industrial production test; Digital signal processing; Wireless communication; ZigBee

#### I. INTRODUCTION

RF devices are nowadays part of our society, especially devices dedicated to the Internet-of-Things (IoT) market. Production test of these devices is an important contributor to the global manufacturing cost, because it classically requires the use of an Automatic Test Equipment (ATE) equipped with expensive RF test resources. There is therefore a strong demand to reduce the testing cost of these devices.

An interesting approach is to develop solutions that can be applied on a digital ATE. A number of works can be found in the literature, e.g. based on the use of a reference transceiver accompanied by a FPGA to handle the interface between the reference transceiver and the digital ATE [1], or based on the use of a processor embedded in a radio SoC to implement self-test and provide low-frequency digital output [2], or defining a digital ATE system with multi-level drivers and comparators for direct modulation/demodulation of QAM signals [3]. Another approach is to perform a direct 1-bit oversampled acquisition, as suggested in [4] for the demodulation of basic AM/FM schemes or in [5] for phase noise characterization of IF signals.

In this work, we exploit a direct 1-bit acquisition, but using harmonic sampling on an RF signal. The targeted device is a ZigBee transmitter that delivers a 2.4GHz OQPSK signal and the objective is to implement the tests specified by IEEE Std 802.15.4<sup>TM</sup> in an industrial environment.

#### II. BACKGROUND

#### A. Signal Under Test Characteristics (ZigBee)

The main characteristics of a ZigBee signal are specified by the IEEE Std 802.15.4<sup>TM</sup>. In this work, we focus on the 2.4GHz band, which is an ISM band accepted worldwide. The modulation format is Offset Quadrature Phase Shift Keying (OQPSK) with half-sine pulse shaping. The standard also specifies the use of Direct Sequence Spread Spectrum (DSSS) technique in order to reduce the overall signal interference. The RF-modulated signal is therefore a signal at 2.4GHz with

a constant envelope; the input data rate is 250kb/s and the chip rate at the input of the modulator is 2Mchip/s.

#### B. Current Test Practice

The current industrial practice for production testing of RF devices relies on the use of an ATE equipped with expensive RF tester channels. Such channels comprise specific hardware resources (mixer, filters, ADC) that realize the acquisition of an RF signal and convert it into a digitized version in the Intermediate Frequency (IF) band; software DSP procedures are then applied on the digitized data to implement various measurements. For ZigBee products, the tests specified by the IEEE Std 802.15.4<sup>TM</sup> are a power test, a spectral mask test and EVM measurement as described hereafter.

The goal of the power test is to verify that the power emitted by the circuit meets specifications defined by the standard, over the full range of circuit power programming. In practice, the power level is checked for three programming levels (typically +10, 0 and -10dBm). For each level, the test equipment performs a measurement of the peak voltage  $V_p$  of the signal emitted by the circuit on a characteristic impedance  $Z_0$  and compute the corresponding power with  $P = V_p^2/2Z_0$ .

The goal of the spectral test is to ensure that the spectrum of the transmitted signal is within the mask imposed by the standard. In particular, Std 802.15.4 specifies that the third secondary lobes located at ±3.5MHz of the carrier frequency must be at least 20dB lower than the power of the main lobe and their power must not exceed -30dBm. In practice, the test equipment calculates the spectrum of the signal captured with an FFT ("Fast Fourier Transform") and verifies that the spectrum obtained falls within the specified mask.

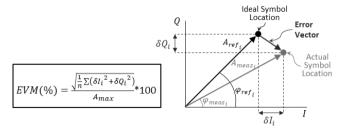

Fig. 1. Error vector magnitude (EVM) definition

Finally, the last test concerns Error Vector Magnitude (EVM), which expresses modulation quality by measuring the deviation of the signal constellation from its ideal reference. It is computed from error vectors defined in the I-Q plane at the instants in time when symbols are detected. As illustrated in Fig.1, the error vector is the difference at a given time between the actual symbol location and the ideal one. EVM is then defined as the Root Mean Square (RMS) amplitude of the

error vector over a sequence of emitted symbols, normalized to ideal signal amplitude reference (maximum amplitude in case of ZigBee as specified by the standard).

#### III. PROPOSED DIGITAL TEST SOLUTION

#### A. Principle

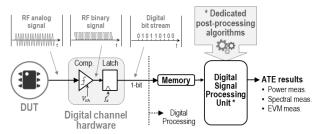

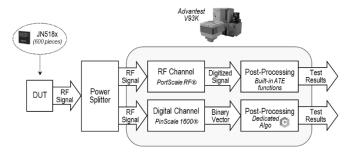

Our strategy to reduce RF testing costs is to propose new solutions that can be applied using low-cost standard digital tester channels instead of expensive RF tester channels. As illustrated in Fig.2, the basic principle is to perform 1-bit acquisition of the RF signal using the comparator and the latch comprised in a digital tester channel and then to apply a dedicated processing algorithm able to retrieve the RF signal characteristics from the captured binary vector. Key challenges are (i) to determine appropriate conditions for the digital capture that permit to preserve the essential information contained in the RF signal and (ii) to define the dedicated processing algorithm able to retrieve the desired signal characteristics.

Fig. 2. Proposed digital approach for testing ZigBee devices

#### B. Digital Acquisition with Harmonic Sampling

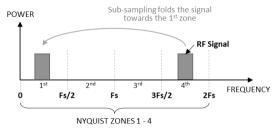

Regarding the digital capture, the fundamental concept is to use harmonic sampling (also called under-sampling or bandpass sampling) in order to overcome the frequency limitation of the test equipment (typically 1.6GS/s for a standard digital ATE channel). The idea is to use a sampling frequency much lower than the signal frequency and to take advantage of the aliasing effect that creates a baseband image of the high-frequency signal [6].

Harmonic sampling is particularly adapted for the analysis of narrow-bandwidth signals, which is the case of ZigBee signals. However, the sampling frequency should be carefully chosen to avoid overlap between the created aliases. The general criterion for a non-destructive sampling is given by:

$$\frac{2f_c + B}{n} \le f_s \le \frac{2f_c - B}{n - 1}$$

for any integer  $n$  satisfying  $2 < n \le \left\lfloor \frac{1}{2} + \frac{f_c}{B} \right\rfloor$  (1)

where  $f_s$  is the sampling frequency,  $f_c$  is the central frequency of the RF signal and B is its bandwidth. Such harmonic sampling is illustrated in Fig.3 for n = 4.

Fig. 3. Harmonic sampling down-conversion (n = 4)

In our case, harmonic sampling is not directly applied on the RF signal. Indeed, the RF signal is first converted into a binary signal with a level-crossing operation implemented by the comparator. Harmonic sampling is then applied on this binary signal. The resulting signal is a digital signal with a fundamental frequency  $f_b = |nf_s/2 - f_c|$ . Despite the level-crossing and down-conversion operations, the low-frequency digital signal still contains relevant information on the phase and amplitude of the original RF signal. It is the role of the post-processing algorithm to retrieve this information.

#### C. Post-Processing Algorithm

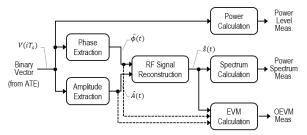

A number of processing functions have already been developed in previous works for the implementation of symbol error detection, power and spectral measurements, as well as EVM measurements. In this work, all these functions are assembled in a global algorithm in order to implement all the tests specified by the standard.

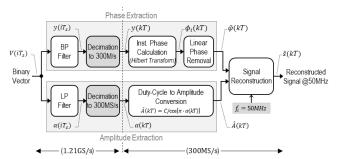

The general architecture of the post-processing algorithm is illustrated in Fig.4. The first steps are to extract information on phase and amplitude fluctuations of the RF signal from the binary vector captured by the ATE. From these two extractions, a reconstructed software version of the original RF signal is computed. Finally, power, spectrum and EVM calculations are performed. For details on the implemented functions, refer to [7] for the phase extraction process, [8] for the amplitude extraction, signal reconstruction, power and spectrum calculation processes, and [9] for the EVM calculation process.

Fig. 4. Block diagram of the post-processing algorithm

#### IV. ADAPTATION TO INDUSTRIAL ATE

#### A. Choice of the ATE Sampling Frequency

The first constraint imposed by the test equipment is that the sampling frequency  $f_s$  must comply with the maximum sampling rate of a digital channel (typically 1.6GS/s). The smallest integer that permits to satisfy both this constraint and the condition of non-destructive harmonic sampling defined in Eq.(1) is n = 4 (1.2043 $GHz \le f_s \le 1.6010GHz$ ). This is the choice used in this work.

The test equipment also imposes another restriction. Indeed, the adjustment of the sampling frequency is done by the setting of the cycle duration (tester period). On the considered equipment, a cycle can contain up to 8 edges, each one associated either to a read or write event. The minimum cycle duration is 5ns, which corresponds to the maximum sampling rate of 1.6GS/s (8 edges associated with a read event and uniformly spread over one tester period). However, the setting of the cycle duration can be done only with a fixed resolution of 0.1ns, which means that the sampling rate can take only a certain number of discrete values. In our case, 16 values satisfy the condition of non-destructive harmonic sampling. The first one is a cycle of 5ns, which corresponds to a sampling frequency of 1.6GHz and produces an aliased

digital signal at 795MHz with a resolution of about 2 samples per period. The last one is a cycle of 6.6ns, which corresponds to a sampling frequency of 1.21GHz and produces an aliased digital signal at 19.2MHz with a resolution of about 63 samples per period. It is clear that the better the resolution of the digital signal captured by the ATE, the more precise the time-domain information extracted from this signal. Therefore, the choice is to use a tester period of 6.6ns, which corresponds to a sampling frequency of 1.21GHz.

#### B. Post-Processing Algorithm Adaptations

The post-processing algorithm, initially developed in the Matlab® environment, has been optimized and ported to C to be executed directly within the ATE software. Some modifications have also been made to optimize its execution time. Indeed in production, test time is an essential factor which has a significant impact on the test cost.

The first modification aims at reducing the computation time. The idea is to decrease the number of points to be processed by reconstructing the signal at a lower frequency than the original 2.4GHz frequency. By lowering the signal frequency, we can diminish the number of points required for its representation. Practically, we have chosen to reconstruct the signal at 50MHz with a sampling rate of 300Ms/s.

Fig. 5. Signal reconstruction at intermediate frequency

The phase and amplitude extraction procedures have been modified, as illustrated in Fig.5. Initially a spline interpolation was realized just after the filtering of the binary vector captured by the ATE to obtain a time resolution compatible with a signal reconstruction at 2.4GHz. This interpolation is now replaced by a decimation towards 300Ms/s. The rest of the procedure is identical, except that the carrier frequency for signal reconstruction is set at 50MHz. Thanks to this adaptation, the number of points to be processed after the filtering operations is reduced by about a factor of 4, which greatly improves the calculation time. The reconstruction of a signal with a duration of 500 $\mu$ s is now performed in 60ms instead of 570ms in the initial version, i.e. a speed-up by about a factor of 10.

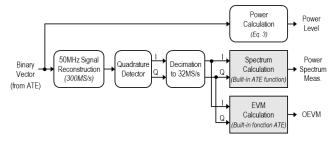

The second modification concerns the functions dedicated to power spectrum and EVM measurements. Indeed, similar functions exist in the ATE software libraries and we assume that they are more optimized than the ones we have developed in Matlab. The idea is therefore to use the built-in functions developed by the ATE manufacturer. However, a main difference is that our functions operate on the RF-modulated signal while the ones available in the ATE software operate on the digitized I and Q waveforms obtained from the acquisition with an RF channel. An adaptation of the algorithm is thus necessary. Concretely, the post-processing algorithm has been modified as illustrated in Fig.6.

A software quadrature detector has been implemented after signal reconstruction at 50MHz. This detector recovers the I and Q waveforms by multiplying the reconstructed signal with a sine and a cosine of same frequency than the signal carrier frequency and applying a low-pass filter to eliminate the double frequency component. The detector outputs are a digitized version of the I and Q waveforms at 300MS/s. A decimation towards 32MS/s is then applied on these signals, 32MS/s being the sampling rate of the signals digitized by the ADC in an RF tester channel. These data are then simply fed to the built-in ATE functions to obtain power spectrum and OEVM values. Regarding power level measurements, there is no advantage to use a built-in ATE function because the implemented function is extremely simple. Indeed, the power level can be directly computed from the ratio between the number of '1s and the number of bits contained in the binary vector captured by the ATE with:

$$P = \frac{1}{2Z_0} \cdot \left(\frac{C}{\cos\left(\pi \frac{\#I_{1S}I}{\#bits}\right)}\right)^2 \tag{2}$$

where C is the comparator threshold value.

Fig. 6. Block diagram of the post-processing algorithm adapted for its integration within the ATE software

#### V. RESULTS

#### A. Preliminary Experiment

Prior to launching large volume measurement campaigns, a preliminary experiment was carried out on one piece of a ZigBee transceiver developed and fabricated by NXP Semiconductors (NXP JN518x). This product is equipped with a test mode in which an RF-modulated signal is generated with random DSSS sequences. It also contains many internal configuration registers, one of which can be programmed with three different values impacting the EVM of the generated signal. These configurations are hereafter referred as SPSF0, SPSF1 and SPSF2, SPSF2 being the nominal configuration which produces a signal with minimum EVM.

#### 1) Power Level Measurements

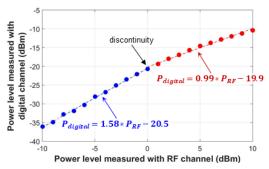

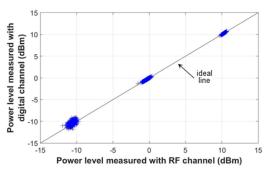

Power measurements were realized using the RF channel on the one hand and the digital channel on the other hand, varying the circuit power level between -10 and +10dBm. Fig.7 shows the power estimated from the digital acquisition as a function of the power measured by the RF channel. A first comment is that the power level measured with the digital channel is much lower than the power level measured with the RF channel. This is explained by the fact that, for the purpose of the experiment, a cobbled connection has been created between the RF output of the circuit to the digital tester channel. This connection is not optimized to handle 2.4GHz and introduce a strong attenuation. The comparator of the digital channel might also contribute to this attenuation. A second comment is that two distinct operating zones can be identified, separated by a discontinuity in the linear behavior around -20dBm (power received by the digital channel). In the first zone corresponding to the highest power levels, the digital measurement exhibits a linear behavior with a slope close to the ideal slope of 1, while in the second zone for lower power levels, it still exhibits a linear behavior but with a slope higher than 1. Investigations were carried out to explain this discontinuity, but all our hypotheses were inconclusive. This phenomenon could be related to the analog behavior of the comparator, but remains unexplained so far.

Fig. 7. Power level measured with digital channel vs. power level measured with RF channel

A pragmatic solution to overcome this problem is to realize a characterization of the digital channel before the mass production test. Indeed, it is easy to determine the offset and slope coefficients corresponding to the two operating zones; these coefficients will be used to correct the digital measurements during the production test.

#### 2) Power Spectrum Measurements

Power spectrum measurements were realized using both digital and RF channels. Results are reported in Table I. There is good agreement between measurements realized on the spectrum of the reconstructed signal and those realized on the spectrum of the RF signal, with a difference of 0.16dB for the measurement on the main lobe and a difference of less than 0.85dB for measurements on the third lobes.

TABLE I. POWER MEASUREMENTS ON PRINCIPAL AND 3RD LOBES

|                     | Main lobe | Lower 3 <sup>rd</sup> lobe | Upper 3 <sup>rd</sup> lobe |

|---------------------|-----------|----------------------------|----------------------------|

| RF measurement      | -3.41dBm  | -40.82dBm                  | -40.19dBm                  |

| Digital measurement | -3.57dBm  | -40.17dBm                  | -41.03dBm                  |

#### 3) OEVM Measurements

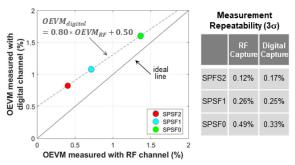

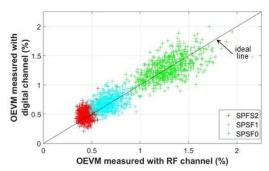

OEVM measurements were realized using both RF and digital channels in SPSF2, SPSF1 and SPSF0 configurations, with 50 repetitions in each configuration. Results are summarized in Fig.8, which presents the evolution of the mean value as well as the measurement repeatability.

Fig. 8. OEVM measured with digital channel vs. OEVM measured with RF channel

A linear relationship is observed between the mean value of the OEVM determined with the digital channel and the one measured with the RF channel. However, this linear trend is slightly above the ideal curve indicating an overestimation, overestimation that reduces as the signal EVM level increases. This behavior is similar to the one that can be observed in simulation when including jitter on the sampling clock of the digital channel. This behavior can be easily compensated based on an initial characterization of the digital channel.

Regarding the measurement variability, an increase is observed for both the digital and RF measurements as the EVM level gets higher. A similar dispersion is observed for both measurements in SPSF2 and SPSF1 configurations (around  $\pm 0.15\%$  and  $\pm 0.25\%$ ), and it is even smaller for the digital measurement in the SPSF0 configuration ( $\pm 0.33\%$  instead of  $\pm 0.49\%$ ).

#### B. First Validation Campaign

#### 1) Setup

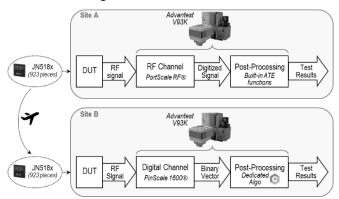

For the first validation campaign, 928 pieces previously evaluated during their production with a standard test on an Advantest 93k tester equipped with RF channels were taken back. These pieces were then subjected to a second evaluation, also carried out on an Advantest 93k tester but this time only using standard digital channels (PS 1600). This general setup is illustrated in Fig.9.

Fig. 9. Setup for the first validation campaign

The second evaluation took place in another geographic site with a different interface board and at a different time, which might entail a variation in the measured circuit performances. Moreover, the connection between the DUT and the digital tester channel was created on top on the existing interface board using a generic routing card. This connection is an ad-hoc connection not optimized to handle 2.4GHz signals. Also, no pre-characterization of the digital channel had been performed. The digital measurements were therefore adjusted by using correction coefficients derived from a regression using the mean of both RF and digital measurements on the 928 pieces.

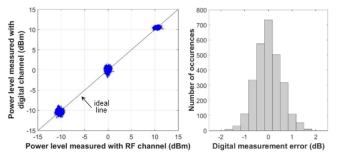

#### 2) Power Level Measurements

Fig.10 shows the results of the digital measurement as a function of the RF measurement after correction, as well as the histogram of the digital measurement error. A good agreement is obtained between the power estimated from the acquisition with the digital channel and the one measured with the RF channel. The maximum error is only of 1.8dB, over the three power levels. This is a fairly good result taking into account the imperfect setup and the fact the digital and RF evaluations have been realized in different sites and with a delay of several weeks. It should be highlight that when the

circuit starts up, it performs a self-calibration which may slightly differ at each start-up. These differences in conditions are likely to contribute to the measurement error.

Fig. 10. Power level measurements on 928 circuits

#### 3) Power Spectrum Measurements

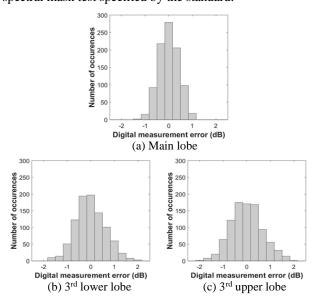

Results of power spectrum measurements are summarized Fig.11 which shows the histograms of the digital measurement error for measurements on the principal lobe and the third lower and upper lobes. All distributions are well centered on zero, showing that the proposed solution does not introduce bias. The error dispersion is lower on the main lobe than on the third lobes, which can be explained by the fact that the main lobe power (around -3dBm) is much higher than the 3<sup>rd</sup> lobes power (around -40dBm), favoring the measurement accuracy. However, even for measurements on the 3<sup>rd</sup> lobes, the error remains contained and does not exceed 2dB. This is a very satisfactory result taking into account that the symbol sequences used for the RF measurement are not identical to those used for the digital measurement, which introduces a variation in the lobe power. More generally, these results fully validate the proposed solution for the implementation of the spectral mask test specified by the standard.

Fig. 11. Histograms of the digital measurement error

#### 4) OEVM Measurements

The results of OEVM measurements on the 928 parts are shown in Fig.12. These results concern only the SPSF2 configuration, i.e. the best performance case. Indeed, the 928 pieces were tested solely under this configuration during their production; we therefore do not have results of the RF test under SPSF1 and SPSF0 configurations. Although there is no clear correlation observed between the digital and the RF measurements, it should be noted that all the 928 pieces have

a similar performance. Indeed, OEVM values measured by the RF test are contained between 0.28% and 0.82%, which corresponds to a variation of only 0.54%. This variation is smaller than the typical measurement uncertainty of an RF instrument, which is usually specified in a range between 0.6 and 1%. There is therefore no guarantee on the accuracy of the measured value. In this situation, it is rational that there is no visible correlation. Nevertheless, there is a good agreement between the digital and RF measurements since the digital measurements are contained between 0.24% and 0.76%, so in the same range than the RF ones. The maximal digital measurement error is only of 0.34%.

Fig. 12. OEVM measurements in SPSF2 configuration on 928 circuits

#### C. Second Validation Campaign

#### 1) Setup

A second validation campaign on 600 pieces was carried out to palliate some of the previous setup weaknesses and evaluate EVM measurements on larger dynamic range. In the new setup, the DUT is connected to both a digital channel and an RF channel using a power divider as illustrated in Fig.13. The circuit is started in test mode; a digital capture is first realized and then an RF acquisition once the digital capture is completed (acquisitions are not performed in parallel due to a material limitation). Finally, test results are evaluated with the standard ATE processing applied on the digitized RF signal on one hand, and with the dedicated algorithm applied on the binary vector on the other hand.

Fig. 13. Setup for the second validation campaign

Compared to the previous setup, both RF and digital captures are this time realized in the same environment and without any interruption of the device operation. Another significant difference is that a pre-characterization of the digital channel was realized by measuring one piece for the three power levels and the three SPSF configurations using both RF and digital acquisitions. Corrections applied on the digital measurements for all the following 600 pieces solely rely on this initial characterization. However, as in the previous setup, the connection between the DUT and the digital tester channel is an ad-hoc connection not optimized to handle 2.4GHz signals.

#### 2) Power Level Measurements

600 pieces were measured for three programmed power levels of +10, 0 and -10dBm. Results are illustrated in Fig.14 which shows the power level measured with the digital channel as a function of the power level measured with the RF channel, after correction. A very good agreement between the two measurements is observed.

Fig. 14. Power level measured with digital channel vs. power level measured with RF channel, on 600 circuits

Statistics of the digital measurement error are reported in Table II, for the three power levels. In all cases, satisfactory measurement accuracy is observed with a mean error close to zero. The maximum error is very low for +10dBm and 0dBm levels, i.e. only 0.10dB and 0.26dB. The maximum error increases to 1.44dB for -10dBm level, which can be explained that the fact that the amplitude of the signal received by the digital channel is only of few millivolts because of the strong attenuation introduced by the ad-hoc wiring. The measurement is clearly more affected by noise in this situation. An adapted design of the interface board between the DUT and the tester should permit to diminish this error below 0.5dB.

TABLE II. STATISTICS OF POWER LEVEL DIGITAL MEASUREMENT ERROR

|               | +10dBm  | 0dBm    | -10dBm |

|---------------|---------|---------|--------|

| Mean Error    | -0.00dB | -0.01dB | 0.23dB |

| Std Deviation | 0.03dB  | 0.05dB  | 0.39dB |

| Max Error     | 0.10dB  | 0.26dB  | 1.44dB |

#### 3) OEVM Measurements

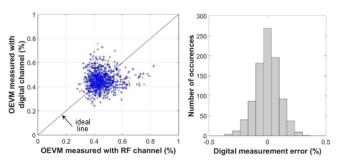

The 600 pieces were also measured in the three possible configurations (SPSF2, SPSF1 and SPSF0). Fig.15 shows the results of the digital measurement as a function of the RF measurement, after correction. A good correlation is observed between the two measurements, all points being well centered around the ideal line.

Fig. 15. OEVM measured with digital channel vs. OEVM measured with RF channel, on 600 circuits

To further refine the analysis, Table III gives the statistics of the digital measurement error, in each configuration. In all cases, satisfactory measurement accuracy is observed, with a mean error close to zero and a standard deviation that does not exceed 0.17%. The maximum error remains below 0.7%, which is within the typical RF measurement uncertainty. These results therefore validate the effectiveness of the proposed solution to perform EVM measurements using only standard digital tester channels.

TABLE III. STATISTICS OF OEVM DIGITAL MEASUREMENT ERROR

|  |               | SPSF2 Nominal Setting | SPSF1 Degraded Setting 1 | SPSF0 Degraded Setting 2 |

|--|---------------|-----------------------|--------------------------|--------------------------|

|  | Mean Error    | 0.05%                 | 0.02%                    | -0.00%                   |

|  | Std Deviation | 0.10%                 | 0.12%                    | 0.17%                    |

|  | Max Error     | 0.38%                 | 0.42%                    | 0.68%                    |

#### VI. CONCLUSION

In this paper, we have validated a low-cost solution for digital production test of ZigBee transmitters in industrial environment. The fundamental approach is to perform 1-bit acquisition of the RF signal with a standard digital ATE channel, using harmonic sampling. Dedicated algorithms optimized for an execution within the ATE software have been proposed to implement the different tests specified by IEEE Std 802.15.4. The solution has been validated on a ZigBee transceiver with measurements realized using both the conventional RF test and the digital one. Results of two measurement campaigns on more than 1.5 thousand of devices have demonstrated the effectiveness of the proposed digital solution to perform accurate power level, power spectrum and EVM measurements.

#### ACKNOWLEDGMENT

This work has been carried out under the framework of PENTA-EUREKA project "HADES: Hierarchy-Aware and secure embedded test infrastructure for Dependability and performance Enhancement of integrated Systems".

#### REFERENCES

- I. Kore et al., "Multi-site test of RF transceivers on low-cost digital ATE," Proc. IEEE International Test Conference (ITC), pp. 1-10, 2011.

- [2] C. H. Peng et al., "A novel RF self test for a combo SoC on digital ATE with multi-site applications," Proc. IEEE International Test Conference (ITC), pp. 1-8, 2014.

- [3] M. Ishida K. Ichiyama, "An ATE System for Testing RF Digital Communication Devices With QAM Signal Interfaces," IEEE Design & Test, vol. 33, no. 6, pp. 15-22, 2016.

- [4] N. Pous et al., J.,"A Level-Crossing Approach for the Analysis of RF Modulated Signals using only Digital Test Resources", J. of Electronic Testing: Theory and App. (JETTA), vol. 27, no. 3, pp 289-303, 2011

- [5] S. David-Grignot et al., "Low-cost phase noise testing of complex RF ICs using standard digital ATE," Proc. IEEE International Test Conference (ITC), pp. 1-9, 2014.

- [6] M. Kahrs, "50 years of RF and microwave sampling," IEEE Trans. on Microwave Theory and Tech., vol. 51, no. 6, pp. 1787–1805, 2003.

- [7] T. Vayssade et al., "Low-cost digital test solution for symbol error detection of RF ZigBee transmitters", IEEE Trans. on Device & Materials Reliability, vol. 19, no. 1, pp. 16-24, 2019.

- [8] T. Vayssade et al., "Power measurement and spectral test of ZigBee transmitters from 1-bit under-sampled acquisition", Proc. IEEE European Test Symposium (ETS), pp. 1-6, 2019

- [9] T. Vayssade et al., "EVM measurement of RF ZigBee transceivers using standard digital ATE", Proc. IEEE Defect and Fault Tolerance Symposium (DFTS), pp. 1-6, 2020