# A Generic Fast and Low Cost BIST Solution for CMOS Image Sensors

Julia Lefèvre, Philippe Debaud, Patrick Girard, Arnaud Virazel

# ▶ To cite this version:

Julia Lefèvre, Philippe Debaud, Patrick Girard, Arnaud Virazel. A Generic Fast and Low Cost BIST Solution for CMOS Image Sensors. ETS 2022 - 27th IEEE European Test Symposium, May 2022, Barcelona, Spain. pp.1-2, 10.1109/ETS54262.2022.9810458. lirmm-03770756

# HAL Id: lirmm-03770756 https://hal-lirmm.ccsd.cnrs.fr/lirmm-03770756v1

Submitted on 6 Sep 2022

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# A Generic Fast and Low Cost BIST Solution for CMOS Image Sensors

J. Lefevre 1, 2

P. Debaud <sup>1</sup>

P. Girard<sup>2</sup>

A. Virazel<sup>2</sup>

<sup>1</sup> STMicroelectronics Imaging division, DFT Grenoble, France

julia.lefevre@st.com, philippe.debaud@st.com

<sup>2</sup> LIRMM University of Montpellier / CNRS Montpellier, France <lastname>@lirmm.fr

Abstract—This paper demonstrates the generalization of a novel test solution embedded inside CMOS Image Sensors (CIS) to classify PASS/FAIL sensors during the test production phase. In [1], a Built-In Self-Test (BIST) solution was proposed to reduce the test time of a CIS, which can represent up to 30% of the final product cost. The major part of the test is dedicated to optical (i.e. image processsing) algorithms performed on the output images from the sensor under test with an Automatic Test Equipment (ATE). The BIST solution reuses these optical algorithms by simplifying and embedding them inside the sensor, to avoid a large amount of data storage and to limit the optical test time. First results on 4,800 output images from a package of sensors have shown a 99.95% correlation between results gathered from an ATE and those achieved with the proposed BIST, with a saving of approximately 30% in optical test time and a negligible area footprint. In this paper, to verify the effectiveness of the BIST solution on a wider set of different CIS (i.e., architecture, size and technology), we experimented the solution on a new database of 28,000 output images from a package of different sensors compared to the first package used in [1]. The BIST parameters have been configured to fit with the new type of sensors and results show a 99.64% correlation, which demonstrates the possible systematic implementation of the proposed BIST solution inside all CIS irrespective of their architecture and technology.

Keywords—CMOS image sensor, BIST, optical test, settings.

## I. Introduction

Nowadays, CIS can be found everywhere, e.g., in smartphones, autonomous cars or night vision systems. A CIS is used to convert a physical phenomenon into an electrical signal. Irrespective of the application domain, it is mandatory to test all the sensors to ensure that they all meet standard requirements. The test of a CIS is performed by an ATE and can represent up to 30% of the final product cost with 10 seconds to 1min dedicated to test [2]. The test flow is split into two parts, electrical and optical tests, to cover all elements inside the sensor. The optical test consumes the major part of the test time, mainly due to the use of two-dimensional (2D) image processing algorithms performed on the output images from the CIS.

In [1], we proposed a fast and low-cost BIST engine embedded directly inside the sensor to reduce approximately by 30% the optical test time with negligeable area overhead (about 0.25%). The BIST allows to apply approximately 50% of the optical algorithms inside the sensor without impacting the defect coverage. It reuses the optical algorithms usually applied by the ATE and simplifies the image processing techniques from a 2D computation which needs huge storage of images, to a **one-dimensional** computation, which supports **at-speed** test. Owing to several parameters used to define defects (pixel or group of pixels), the BIST is able to sort out good and bad sensors. To prove it, results over a package of more than 2,400 sensors have shown a good correlation (**99.95%**) between ATE-based test results and results gathered by the proposed BIST solution.

In this paper, we evaluate the efficiency and hence the generalization of the BIST solution on a different package of sensors compared to the one used in [1].

The paper is organized as follows. Section II gives some backgrounds on CIS testing. Section III briefly describes the operation and architecture of the BIST solution and explains the results of the BIST on two different packages of sensors.

#### II. BACKGROUND OF THE STUDY

# A. CMOS Image Sensor Generalities

A CIS is able to convert light information into an image. It is composed of optical elements to catch the light information and electrical elements to cary and adapt the signal. The optical part of the CIS is a pixel array. Each pixel contains a photosensitive element (photodiode) which represents 50-70% of the pixel area (called the fill factor) [3]. The photodiode converts photons in electrons through the photoelectric effect [4]. The electron flow is amplified by a column amplifier and the resulting voltage is converted as a digital pixel value by an ADC. The digital pixel values are then treated by the ISP (Image Signal Processor) ensuring calibration or filtering before to display properly the output image on a display module by using an output interface.

## B. CMOS Image Sensor Testing

CIS testing is done to find good versus bad sensors. A bad sensor contains too many defective pixels or a cluster of defective pixels (group, defective row or defective column) [1]. A defective pixel is a pixel value which cuts the

homogeneity of the local area, i.e. which differs too much from the values of its neighbours.

As said before, the test is split into optical and electrical tests. Electrical tests are relatively fast compared to optical tests, which explains the interest in reducing optical tests time. The optical tests are performed on output images from the sensor and lays on 2D image processing algorithms launched on the output captures of a CIS [5]. During optical tests, the CIS is put under several conditions of illumination (Dark and Light conditions, respectively no illumination and illumination) to be able to generate different output images. An image resulting from the Light condition has a shaded aspect (higher value in the middle) whereas an image from the Dark one is homogeneous (constant value). Other parameters can vary to create other images such as different integration time (Short or Long integration). The difference between Short and Long resulting images is a difference of values with higher values for Long integration images.

One image from each configuration is saved in a memory of the ATE, depending on the use-case of the sensor.

# III. BUILT-IN SELF TEST SOLUTION

#### A. BIST Overview

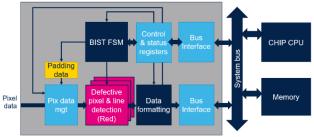

Inside the sensor, a sequencer block is able to sweep the pixel array in 1D, row by row. The BIST solution reuses this 1D reading ability to perform at-speed test avoiding the storage of the whole image. The BIST is split into a digital part embedded inside the CIS and a firmware on the CPU of the system. Figure 1 shows the BIST architecture.

Figure 1: General BIST architecture

The BIST operation is the following: a pixel (the pixel under test) and its neighbours are streamed by the sequencer block. The *Pixel Data Management* block computes the coordinates of the pixel under test to configure the type of the pixel (Red, Green or Blue (RGB) pixel in case of RGB sensor) to send it in the appropriate machine in the *Defective Pixel & Line Detection* (*DPLD*) block. The *DPLD* block is composed of three or more machines to do parallel computation, and to compute a local average thanks to the values of the neighbours of the pixel under test. The *Padding Data* block is enabled in case the pixel is located at the border of the image to compute a value from the neighbour's values.

If the pixel value is defined as defective by the *DPLD* block, the data of the pixel (coordinates, type and value) is formatted in the *Data Formatting* block to be saved in an external memory. Once the whole pixel array has been streamed, the firmware reads the memory to classify the defective pixels into several defect categories (singlet, couplet or cluster) [1].

The definition of a defective pixel depends on the parameters used in the *DPLD* block. The value of the pixel

under test is compared to thresholds (minimum and maximum) defining a range of correct values. Equation 1 specifies the range and needs to be the more generic as possible to be reused for both defective pixel and defective row definitions. Parameters  $a_{\min}$ ,  $a_{\max}$ ,  $b_{\min}$  and  $b_{\max}$  are fitted to minimize the errors between results from the ATE and results from the BIST in each defect category.

The parameters are adjusted based on the condition of illumination and the integration time variation. For examples, the parameters for a Dark image are constant and the ones for a Light image depend on a percentage of the local average.

# B. BIST results

A Python script is used to emulate the BIST engine. The validation of the BIST relies on two databases. A database is composed of a set of output images from sensors plus a file that summarizes the outputs of each test performed on sensors in the database.

A first database, composed of dark and light images (4,800 images for 2,400 sensors) has been used in [1]. The parameters in (1) have been configured in order to correlate the BIST results on the first database with the ATE results. A correlation of **99.95%** has been reached for 4,800 images.

The second database contains dark/light images and short/long images (28,000 images for 7,000 sensors). This database contains different sensors compared to the sensors in the first one (size and architecture). Similarly to the work done in [1] on the first database, the setting of the parameters allows to compare results from the BIST and results from the ATE. A correlation of **99.64%** is reached for 28,000 images. The use of the BIST on the second database highlighted a limitation on the detection of very fine defects.

An estimation of the size of the BIST engine in terms of additional logic gates shows that the BIST solution represents approximately 1,000FF, i.e. 0.25% of the total area overhead.

A precise study of optical algorithms reveals that the use of the BIST engine allows to gain approximately 30% of the optical test time by embedding 50% of the optical algorithms performed by an ATE.

By adapting the parameters of the BIST, the proposed solution can be used to test a CIS independently of its architecture, size and technology. Our future work will consist in performing experiments on other types of sensor to continue the validation process and to implement industrially the BIST solution inside CIS to perform a part of optical tests done today with an ATE.

## REFERENCES

- J. Lefevre, P. Debaud, P. Girard, and A. Virazel, "A Fast and Low-Cost Embedded Test Solution for CMOS Image Sensor", in Proc. IEEE International Test Conference, 2021.

- [2] A.Grochowski, D.Bhattacharya, T.R.Viswanathan, K.Laker, "Integrated Circuit Testing for Quality Assurance in Manufacturing: History, Current Status, and Future Trends", in Proc. IEEE Transactions on circuits and systems-II: analog and digital signal processing, vol. 44, NO.8, 1997.

- [3] L. Lizarraga, "Autotest technique for CMOS imager", PhD dissertation, Institut National Polytechnique de Grenoble -INPG, 2008.

- [4] R.Fei. "Alternative Solution to Improve the Production Test of Optical Sensors in CMOS Technology", PhD dissertation, Grenoble Alpes University, 2015.

- [5] J. Chen, "CIS Testing Technology", Jetek Technology corporation, 2018. https://fr.slideserve.com/amos/cis-testing-technology