# Designs of Array Multipliers with an Optimized Delay in Quantum-Dot Cellular Automata

Aibin Yan, Xuehua Li, Runqi Liu, Zhengfeng Huang, Patrick Girard, Xiaoqing Wen

# ▶ To cite this version:

Aibin Yan, Xuehua Li, Runqi Liu, Zhengfeng Huang, Patrick Girard, et al.. Designs of Array Multipliers with an Optimized Delay in Quantum-Dot Cellular Automata. Electronics, 2023, 12 (14), pp.3189. 10.3390/electronics12143189. lirmm-04239247

# HAL Id: lirmm-04239247 https://hal-lirmm.ccsd.cnrs.fr/lirmm-04239247v1

Submitted on 12 Oct 2023

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

MDPI

Article

# Designs of Array Multipliers with an Optimized Delay in Quantum-Dot Cellular Automata

Aibin Yan 1,2,\* , Xuehua Li 1, Runqi Liu 1, Zhengfeng Huang 2, Patrick Girard 3 and Xiaoqing Wen 4

- School of Computer Science & Technology, Anhui University, Hefei 230601, China; e22201123@stu.ahu.edu.cn (X.L.); e21301141@stu.ahu.edu.cn (R.L.)

- School of Microelectronics, Hefei University of Technology, Hefei 230601, China; huangzhengfeng@139.com

- <sup>3</sup> LIRMM, University of Montpellier, CNRS, 34093 Montpellier, France; girard@lirmm.fr

- Department of Computer Science and Networks, Kyushu Institute of Technology, Fukuoka 820-8502, Japan; wen@cse.kyutech.ac.jp

- \* Correspondence: abyan@mail.ustc.edu.cn; Tel.: +86-186-551-12073

**Abstract:** Quantum-dot cellular automata (QCA) has been considered as a novel nano-electronic technology. With the advantages of low power consumption, high speed, and high integration, QCA has been treated as the potential replacement technology of the CMOS (complementary metal oxide semiconductor) which is currently used in the industry. This paper presents a QCA-based array multiplier with an optimized delay. This type of circuit is the basic building block of many arithmetic logic units and electronic communication systems. Compared to the existing array multipliers, the proposed multipliers have the smallest cell count and area. The proposed designs used a compact clock scheme to reduce the carry delay of the signals. The  $2 \times 2$  array multiplier clock delay was reduced by almost 65% compared to the existing designs. Moreover, since the multiplier exhibits a good scalability, for further proof, we proposed a  $3 \times 3$  array multiplier. Simulation results asserted the feasibility of the proposed multipliers. Extensive comparison results demonstrated that when the design scaling was increased, our proposed designs still displayed an efficient overhead in terms of the delay, cell count, and area. The QCADesigner tool was employed to validate the proposed array multipliers. The QCADesigner-E was used to measure the power dissipation of the alternative compared solutions.

Keywords: QCA; array multiplier; XOR gate; full adder

Citation: Yan, A.; Li, X.; Liu, R.; Huang, Z.; Girard, P.; Wen, X. Designs of Array Multipliers with an Optimized Delay in Quantum-Dot Cellular Automata. *Electronics* **2023**, 12, 3189. https://doi.org/10.3390/ electronics12143189

Academic Editor: Masum Hossain

Received: 21 June 2023 Revised: 15 July 2023 Accepted: 19 July 2023 Published: 23 July 2023

Copyright: © 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

# 1. Introduction

Transistor feature sizes of silicon-based CMOS elements are rapidly approaching their limits. The quantum tunneling effect and the coulomb blockade of devices are also becoming more and more severe, and together, all of these bring great challenges to the stability and reliability of the CMOS circuits [1].

Since nano-electronic devices possess the advantages of having a high speed, a low power dissipation, and a high integration ability, nano-electronic devices have become the research focus of the next-generation electronic devices. These devices mainly include organic thin-film transistors, transparent oxide-thin-film transistors, resonant tunneling diodes, single-electron transistors, carbon nanotubes, quantum dot cellular automata (QCA), and so on [2,3]. QCA is favored by researchers because of its unique operating mechanism and advantages. QCA circuits output data based on the cellular automata principle and the coulomb interaction force. A QCA cell comprises free electronics, quantum dots, and tunnel junctions. A QCA cell can represent binary data by the positions occupied by the electrons in the cell [4]. The mechanism of operations for the QCA circuits is quite different from that of the CMOS circuits. The QCA circuit transmits data through the coulomb force between cells. QCA circuits have very low power consumption, high integration, fast operation speeds, and stable operations at room temperature [5]. QCA

Electronics 2023, 12, 3189 2 of 12

technology provides a new solution to break through the performance bottleneck of the CMOS circuits. Currently, there are three main approaches to the physical implementation of QCA: molecular QCA, magnetic QCA, and electronic QCA. The advancement of nanofabrication technology has enabled the production of quantum dots on the nanoscale, which can be used to manipulate electrons in a controlled manner. This allows for the physical realization of the QCA cells and their simple circuits, thus validating the correctness of the QCA theory. Currently, there are four physical implementation schemes for QCA: semiconductor material-based, tunneling junction formation using metal materials, molecular material-based, and magnetic material-based schemes. Each of these schemes is supported by a substantial amount of theoretical and experimental research. However, at the current research level, there are still some challenges that need to be addressed. For the purposes of this article, the physical implementation of the current technology needs to be further explored, which will also become our future goal. In turn, QCA technology has been truly applied.

To the best of our knowledge, there are currently four different QCA models. Nanomagnets-based fan-out lines, silicon-based QCA lines, and ferrocene molecules-based QCA lines have all been proven through experimentation [6,7]. Meanwhile, logic circuit blocks, such as full-adders, XOR gates, multipliers, as well as dividers have already been verified through pertinent simulations.

Previous studies have assessed the impacts of array multipliers. In 2004, Walus et al. proposed a novel bit-serial/parallel multiplier based on a bit-serial-adder [8]. One input of the multiplier is serially loaded into the adder, while the other input is effectively loaded in parallel. The multiplier calculates the partial product and adds it to the sum immediately. In 2007, Hanninen et al. proposed a novel QCA-based pipelined array multiplier [9]. This design used a reasonable clock allocation to operate reliably without suffering from the effects of noise coupling. The design of the multiplier unit is typically complex, resulting in a large overall cost. In 2010, Lu et al. designed and analyzed a QCA-based systolic matrix multiplier [10]. The 2  $\times$  2 systolic matrix multiplier consisted of four processing elements (PEs), each of them including an advanced 2-bit serial-multiplier as well as a novel 4-bit accumulator. In 2016, Chudasama et al. used a carry save adder to construct a QCA-based  $4 \times 4$  Vedic multiplier [11]. In 2018, Babaie et al. proposed an efficient multilayer arithmetic logic unit [12] and Torres et al. proposed a model to explore performance and energy of QCA [13]. In 2019, Bhoi et al. proposed a novel, accurate method to synthesizing while also optimizing the Baugh–Wooley-multiplier [14]. In 2019, Yang et al. proposed a  $2 \times 2$  array multiplier circuit, which uses an efficient full adder structure. Meanwhile, Bahar et al. proposed a serial Parallel Multiplier [15]. In 2020, Chu et al. proposed BCD adder with xor gates and majority gates [16] and other researches proposed Decimal full adders with different devices [17–19]. In 2021, Perri et al. proposed low-energy multi-bit approximate adders [20] and Khanet al. proposed efficient vedic square calculator [21]. The designs provided ideas for us to design multipliers. Dividers constructed using unit structures have also been proposed, including non-restoring dividers [22–27] and restoring dividers [28].

Currently, state-of-the-art works include many modules in traditional digital circuits, such as adders [29], multipliers [30,31], dividers [32,33] etc. In 2022, K Raja Sekar et al. proposed an array multiplier with a relatively high latency, and also proposed a high-speed serial–parallel multiplier. This is an efficient hardware circuit that has been used across different applications ranging from simple arithmetic circuits, to filters, and complex cryptographic systems. However, it uses a lot of cells and has a large area. In addition, a variety of QCA circuits have been proposed, such as: full adders [34,35], memory cell [36–38], multi-bit full comparator [39] and other circuits [40–45]. Sequential logic elements have also been implemented in these QCA circuits. In large-scale circuits, there are also programmable logic arrays and field-programable gate array circuits based on QCA technology. Indeed, QCA also has its unique research areas, such as clock schemes, logic synthesis, and layout algorithms. From the current level of research, there are still areas where QCA

Electronics **2023**, 12, 3189

circuits need to be improved, but these unique properties of QCAs are still considered by researchers to implement one of the most promising new nano-devices.

Considering the above existing problems, in this paper, we presented a novel QCA-based array multiplier. The proposed array multiplier was effectively simulated and verified through the QCADesigner tool [46]. Compared with existing designs, the proposed novel designs have the smallest delay, cell count, and area. Moreover, we analyzed the complexity of the n\*n design and made a theoretical comparison between the amount of employed QCA-based devices and their delay costs. We found that when the design scaling was increased, the proposed schemes demonstrated an excellent circuit performance.

The organization of the rest of this paper is as follows. In Section 2, the preliminaries of the QCA technology were introduced. In Section 3, the proposed array multipliers were described. In Section 4, the simulation results and comparisons were presented. In Section 5, the conclusions were outlined.

#### 2. Preliminaries

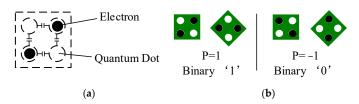

Figure 1 presents the structure as well as two types of QCA cells. Figure 1a presents the structure of the standard four quantum-dot QCA cell. As shown in Figure 1a, there is a tunnel junction present between each quantum-dot, and there exists two additional free-electrons in each QCA cell. Two free electrons can effectively tunnel between these quantum-dots through the tunnel junctions. Due to the coulomb repulsion between these electrons, when the cell is in a stable state, the electrons always occupy the diagonal position, meaning that the cell exhibits double-stable polarization states that can be effectively used to represent the binary data. Figure 1b shows two important types of QCA cells, i.e., the normal cells as well as the rotated cells.

**Figure 1.** Structure and types of QCA. (a) Structure and (b) two types of QCA cells.

QCA encompasses a unique clock mechanism. A QCA clock can control the direction of information transmission and provide the energy of the QCA circuit. Figure 2 presents a QCA clock, which consists of four phases: switch, hold, release, and relax. In the switch phase, the cell will be polarized by the adjacent cells in the hold phase; in the hold phase, the polarization of the cell remains unchanged, and in the switch phase it can polarize the adjacent cells. The polarization of the cell gradually decreases in the release phase; the cell is in a non-polarization state in the relax phase [4].

Figure 2. The QCA clock.

Electronics **2023**, 12, 3189 4 of 12

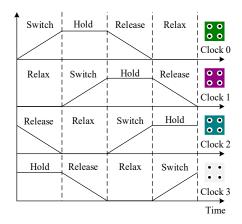

Figure 3 displays several QCA basic gates. Figure 3a shows an inverter, which can flip its input signal. Meanwhile, Figure 3b presents a novel majority gate, which can realize the function of Formula (1). The function of an AND gate or an OR gate can be realized through fixing an input of the majority gate as either 1 or 0 as M(A, B, 1) = A + B and M(A, B, 0) = AB, respectively. Figure 3c shows a 3-input XOR gate, which can implement the function of Formula (2). The 3-input XOR gate can realize the function of a 2-input XOR or XNOR gate by fixing one input as 1 or 0 as  $X(A, B, 0) = A \oplus B$  and  $X(A, B, 1) = \overline{A \oplus B}$ , respectively.

$$M(A, B, C) = AB + AC + BC$$

(1)

$$X(A,B,C) = A \bigoplus B \bigoplus C$$

(2)

$$M(A, B, C, D, E) = ABC + ABD + ABE + ACD + ACE +ADE + BCD + BCE + BDE + CDE$$

(3)

$$MUX(A, B, Sel) = \overline{Sel}A + SelB$$

(4)

**Figure 3.** QCA-based basic gates. (a) Inverter. (b) Three-input majority gate. (c) Three-input XOR gate. (d) Five-input majority gate. (e) Two-to-one multiplexer designed by the authors of [47].

Figure 3d displays a 5-input majority gate. Formula (3) shows the boolean expression of the 5-input majority gates. By setting two inputs of the 5-input majority gate to either 0 or 1, the functions of the AND gate and OR gate can be realized, respectively. Figure 3e shows a two-to-one multiplexer that was put forward by the authors of [47]. Formula (4) shows the boolean expression of the two-to-one multiplexer. The multiplexer can output either signal A or signal B depending on the signal (Sel) of the two-to-one multiplexer. In Figure 3, the blue cells are the input cells and the yellow cells is the output cells.

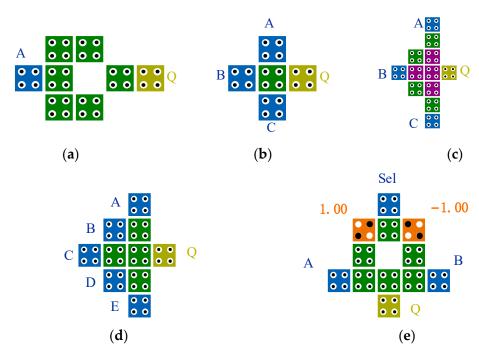

Crossovers can cross two signals, which are widely used in QCA circuits. Figure 4 shows two crossovers. Figure 4a shows the multi-layer crossover. A multi-layer crossover requires at least three layers to cross signals. Figure 4b shows a coplanar crossover implemented using rotated cells. The two signals can correctly flow through the coplanar crossover. Due to the orthogonal electron configuration of these cells, the coulomb force between the cells can not interfere with their neighboring cells.

Electronics **2023**, 12, 3189 5 of 12

**Figure 4.** Crossovers. (a) Multi-layer crossover. (b) Coplanar crossover implemented by the rotating QCA cells.

# 3. Proposed Array Multipliers

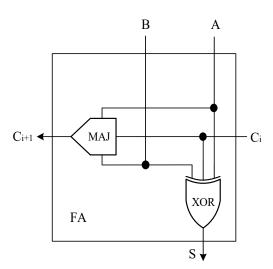

### 3.1. Full Adder

Figure 5 presents the structure of a QCA-based full adder (FA) [48]. We can see from Figure 5 how the structure of the FA only requires one 3-input majority gate as well as one 3-input XOR gate. A is the augend, B is the addend,  $C_i$  is the low carry input,  $C_{i+1}$  is the high carry output, and S represents the sum, respectively. Formulas (5) and (6) display the boolean functions of the FA.

$$S = A \bigoplus B \bigoplus C_i = X(A, B, C_i)$$

(5)

$$C_{i+1} = M(A, B, C_{i+1})$$

(6)

Figure 5. Schematic of the QCA-based FA outlined by the authors of [48].

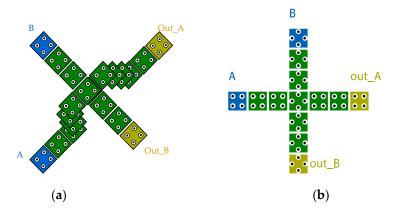

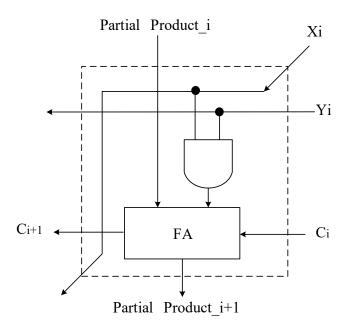

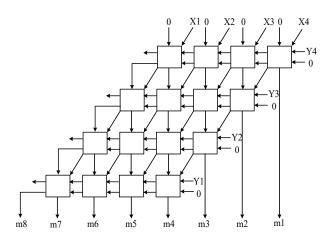

# 3.2. Array Multiplier

Figure 6 shows the schematic of the multiplier unit [9]. The basic unit of the array multiplier consists of an AND gate and a FA. The array multiplier can be built with multiplier units. Figure 7 shows the schematic of the array multiplier [9]. X1/X2/X3/X4 is the multiplicand, Y1/Y2/Y3/Y4 is the multiplier, and m1/m2/m3/m4/m5/m6/m7/m8 is the product, respectively. Each row of the array multiplier is built with ripple carry adders (RCAs). The array multiplier needs to check the bits of the multiplier one at a time and produces the next partial product. A sequence of add and shift micro-operations are required to obtain the final results. Each bit of the multiplier and each bit of the multiplicand

Electronics **2023**, 12, 3189 6 of 12

are ANDed together. The binary output of each AND gate and the partial product in the previous level are then added in parallel to produce a new partial product, and the last level of the array multiplier produces the final product. Although the array multiplier requires many gate devices, its internal structure is regular and highly standardized, making it suitable for the implementation of the VLSI circuits.

**Figure 6.** Schematic of the multiplier unit outlined by the authors of [9].

**Figure 7.** Schematic of the array multiplier outlined by the authors of [9].

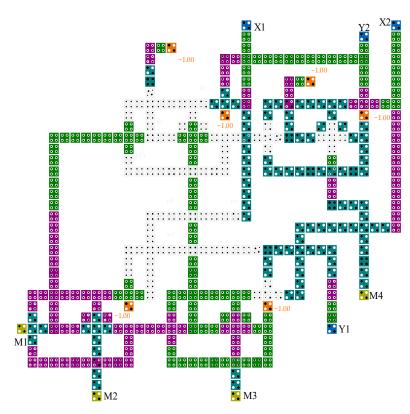

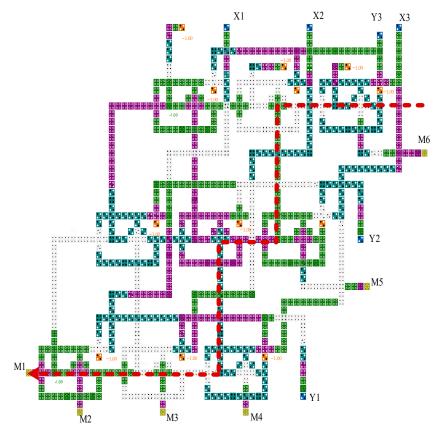

Figure 8 shows the proposed QCA-based 2  $\times$  2 array multiplier. The FA implemented by the authors of [29] was used to design the array multiplier. The multiplier unit is constructed with a FA and an AND gate. The proposed 2  $\times$  2 array multiplier comprises 439 cells, having an area of 0.49  $\mu m^2$ , as well as a delay of 1.75 clock-cycles. X1/X2 is the multiplicand, Y1/Y2 is the multiplier, and M1/M2/M3/M4 denotes the product, respectively. Figure 9 shows the proposed QCA-based 3  $\times$  3 array multiplier, which consists of a three-layer design. The proposed 3  $\times$  3 array multiplier comprises 1041 cells, having an area of 1.26  $\mu m^2$  and a delay of 2.50 clock-cycles. X1/X2/X3 is the multiplicand, Y1/Y2/Y3 is the multiplier, and M1/M2/M3/M4/M5/M6 represents the product, respectively. The used RCAs in each row of the proposed array multiplier adopt compact clock allocation in order to minimize carry delay. The array multiplier can output the calculation results after 2.50 clock cycles.

Electronics **2023**, 12, 3189 7 of 12

**Figure 8.** The proposed QCA-based  $2 \times 2$  array multiplier.

**Figure 9.** The proposed QCA-based  $3 \times 3$  array multiplier.

Electronics 2023, 12, 3189 8 of 12

# 4. Simulations and Comparisons

### 4.1. Simulations

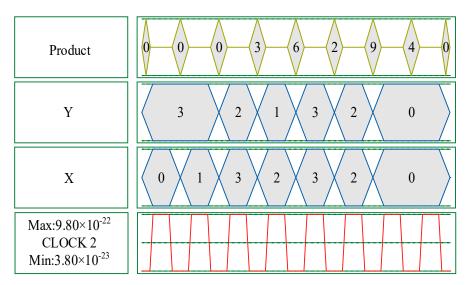

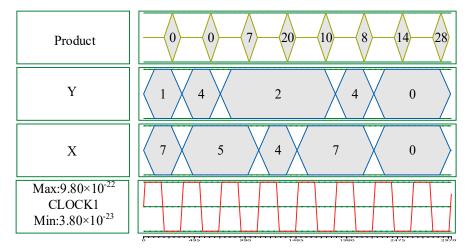

We simulated and verified the proposed designs with the QCADesigner tool. The simulation process requires two multipliers, which are placed in the X and Y inputs, respectively, while the product displays the output. Figure 10 presents the results of the simulations that were performed using the proposed QCA-based 2 × 2 array multiplier, and also displays the results of the six consecutive pairs of multipliers that were used. X was set to {0, 1, 3, 2, 3, 2}, and Y was set to {3, 3, 2, 1, 3, 2}, respectively. The product was {7, 20, 10, 8, 14, 28} following calculations. The calculation process of the proposed array multiplier required 1.75 clock cycles. Since there are four clock zones in a clock cycle and the clock regions are numbered from 0, the product is displayed in clock 2 as a result. For example, when the first pair has a multiplier of 0 and the other has a multiplier of 3, the correct result of the multiplier of that pair appears after 1.75 clock cycles. Figure 11 presents the results of the simulations that were performed for the proposed QCA-based  $3 \times 3$  array multiplier. Similarly, we set X and Y to the two multipliers, and the product to the output. X was set to {7, 5, 5, 4, 7, 7}, and Y was set to {1, 4, 2, 2, 2, 4}, respectively. The product was {7, 20, 10, 8, 14, 28} after calculations. The calculation process of the proposed array multiplier required 2.50 clock cycles. For example, when one multiplier is 1 and the other is 7, the product is calculated 7 after 2.5 clock cycles. In this context, this result was deemed to be correct.

**Figure 10.** Results of the simulations for the proposed QCA-based  $2 \times 2$  array multiplier.

**Figure 11.** Results of the simulations for the proposed QCA-based  $3 \times 3$  array multiplier.

Electronics **2023**, 12, 3189 9 of 12

### 4.2. Comparisons

Table 1 presents the results of the comparisons between the alternative multipliers. As multiplication does not require the judging of the most significant bit of each row, unlike division, but only requires the shift and add micro-operations, the delay of the array multipliers increases slowly with the increase in the design scaling. Compared with the work published by the authors of [49], the proposed array multiplier reduced the cell count, area, and delay by 10.95%, 31.94%, and 65.00%, respectively.

| Design                                    | Cell Count | Area (μm²) | Delay | Layer Type |

|-------------------------------------------|------------|------------|-------|------------|

| 2 × 2 matrix multiplier [10]              | 7102       | 15.69      | 20    | M          |

| 2-bit-serial multiplier [8]               | 306        | 0.48       | 8     | С          |

| 2-bit multiplier [9]                      | 1598       | 1.76       | 7     | С          |

| $2 \times 2$ Baugh–Wooley multiplier [14] | 688        | 0.91       | 3     | M          |

| $2 \times 2$ array multiplier [49]        | 493        | 0.72       | 5.00  | С          |

| Pro 2 $\times$ 2 array multiplier         | 439        | 0.49       | 1.75  | M          |

| Pro 3 $\times$ 3 array multiplier         | 1041       | 1.26       | 2.50  | M          |

**Table 1.** Results of the comparisons for the alternative multipliers.

Table 2 presents the results of the comparisons of energy consumption for the proposed designs. The energy consumption of the proposed designs under different temperatures was measured using the QCA-Designer-E tool [13], and other parameters present in the QCA-Designer-E tool were set as the default values. As clearly shown in Table 2, the energy consumption of the proposed array multiplier was deemed to be lower compared to the solution outlined by the authors of [49].

| Table 2. Results | of the comparisons of | f energy consumption | n for the proposed designs. |

|------------------|-----------------------|----------------------|-----------------------------|

|                  |                       |                      |                             |

| Design               | Total Energy<br>Dissipation (eV) | Average Energy Dissipation (eV) | Total Energy<br>Dissipation (eV) | Average Energy Dissipation (eV) |

|----------------------|----------------------------------|---------------------------------|----------------------------------|---------------------------------|

|                      | Temperature 1K                   |                                 | Temperature 2K                   |                                 |

| MUL 2 × 2 [49]       | $1.78 \times 10^{-1}$            | $1.62 \times 10^{-2}$           | $1.83 \times 10^{-1}$            | $1.66 \times 10^{-2}$           |

| Pro-MUL 2 $\times$ 2 | $1.56\times10^{-1}$              | $1.42 \times 10^{-2}$           | $1.54 \times 10^{-1}$            | $1.40 	imes 10^{-2}$            |

| Pro-MUL $3 \times 3$ | $3.79 \times 10^{-1}$            | $3.44 \times 10^{-2}$           | $3.76 \times 10^{-1}$            | $3.41 \times 10-2$              |

### 4.3. Complexity Analysis

The proposed designs were all constructed using separate QCA devices, such as 3-input majority gates, inverters, and 3-input XOR gates. The total amount of used QCA devices can be employed to effectively measure the area cost of n  $\times$  n designs. An n  $\times$  n multiplier requires 2n2 MGs and n2 XOR gates, and thus form a total of 3n2 QCA devices.

Formula (7) displays the theoretical delay of the  $n \times n$  multiplier. Formula (5) can be obtained through analyzing the delay of the red path displayed in Figure 9.  $D_{n\_MUL}$  represents the delay of the  $n^*n$  multiplier and DMUL denotes the delay of the multiplier unit, respectively. It is clearly shown that when the design scaling is increased, the delay from the input to the output of the proposed multiplier also increased linearly.

$$D_{n\_MUL} = (3n - 2) \cdot D_{MU} \tag{7}$$

#### 5. Conclusions

In this paper, we have proposed a new QCA-based  $2 \times 2$  array multiplier, and based on this structure, a higher-digit  $3 \times 3$  array multiplier has also been proposed. The improved clocking scheme reduces the carry delay, and the clock delay of the  $2 \times 2$  array multiplier is reduced by almost 65% compared to the existing designs. Furthermore, the number of cells and the area has also been optimized, resulting in a faster circuit calculation. It is

Electronics 2023, 12, 3189 10 of 12

beneficial to apply the proposed multiplier to a wider range of arithmetic logic units or communication system units. Moreover, according to our proposed design summary, as a complexity analysis method has been obtained, this can prove the rationality of the n\*n design that we proposed and permit calculations of the theoretical delay of the multiplier. In conclusion, the proposed array multiplier exhibits significant advantages in terms of the delay, cell counts, and area. Moreover, previous research has indicated that fault tolerance is also an important issue which remains to be considered [50,51]. Going forward, we will consider this issue and provide the simulation results.

**Author Contributions:** Conceptualization, A.Y., X.L. and P.G.; methodology, P.G. and X.W.; software, X.L.; validation, A.Y. and X.L.; formal analysis, R.L.; investigation, P.G. and Z.H.; resources, P.G.; data curation, Z.H. and X.L.; writing—original draft preparation, X.W. and R.L.; writing—review and editing, X.W. and X.L.; visualization, R.L.; supervision, Z.H.; proposal administration, A.Y.; funding support, X.W. All authors have read and agreed to the published version of the manuscript.

**Funding:** This research was funded in part by the NSFC of China grant number 61974001, and the APC was funded by 61974001.

**Institutional Review Board Statement:** Not applicable.

**Informed Consent Statement:** Not applicable.

**Data Availability Statement:** Not applicable.

**Conflicts of Interest:** The authors declare no conflict of interest.

## References

1. Fortes, J. Future challenges in vlsi system design. In Proceedings of the IEEE Computer Society Annual Symposium on VLSI, Tampa, FL, USA, 20–21 February 2003; pp. 5–7.

- 2. Oh, T. Organic thin-film transistors using pentacene and sioc film. IEEE Trans. Nanotechnol. 2006, 5, 23–29. [CrossRef]

- Appenzeller, J. Carbon nanotubes for high-performance electronics—Progress and prospect. Proc. IEEE 2008, 96, 201–211.

[CrossRef]

- 4. Lent, C.; Liu, M.; Lu, Y. Bennett clocking of quantum-dot cellular automata and the limits to binary logic scaling. *Nanotechnology* **2006**, *17*, 4240–4251. [CrossRef] [PubMed]

- 5. Timler, J.; Lent, C. Power gain and dissipation in quantum-dot cellular automata. J. Appl. Phys. 2002, 91, 823–831. [CrossRef]

- 6. Imre, A.; Csaba, G.; Ji, L.; Orlov, A. Majority logic gate for magnetic quantum-dot cellular automata. *Science* **2006**, *311*, 205–208. [CrossRef] [PubMed]

- 7. Pulimeno, A.; Graziano, M.; Demarchi, D.; Piccinini, G. Towards a molecular qca wire: Simulation of write-in and read-out systems. *Solid-State Electron.* **2012**, *77*, 101–107. [CrossRef]

- 8. Walus, K.; Jullien, G.; Dimitrov, V. Computer arithmetic structures for quantum cellular automata. In Proceedings of the The Thrity-Seventh Asilomar Conference on Signals, Systems & Computers, Pacific Grove, CA, USA, 9–12 November 2003; pp. 1435–1439.

- 9. Hanninen, I.; Takala, J. Pipelined array multiplier based on quantum-dot cellular automata. In Proceedings of the 2007 18th European Conference on Circuit Theory and Design, Seville, Spain, 27–30 August 2007; pp. 938–941.

- 10. Lu, L.; Liu, W.; O'Neill, M.; Swartzlander, E.E. QCA Systolic Matrix Multiplier. In Proceedings of the 2010 IEEE Computer Society Annual Symposium on VLSI, Lixouri, Greece, 5–7 July 2010; pp. 149–154.

- 11. Chudasama, A.; Sasamal, T. Implementation of 4 × 4 Vedic Multiplier Using Carry Save Adder in Quantum-dot Cellular Automata. In Proceedings of the 2016 International Conference on Communication and Signal Processing, Melmaruvathur, India, 6–8 April 2016; pp. 1260–1264.

- 12. Babaie, S.; Sadoghifar, A.; Bahar, A. Design of an Efficient Multilayer Arithmetic Logic Unit in Quantum-dot Cellular Automata (QCA). *IEEE Trans. Circuits Syst. II Express Briefs* **2018**, *66*, 963–967. [CrossRef]

- 13. Torres, F.S.; Wille, R.; Niemann, P.; Drechsler, R. An Energy-aware Model for the Logic Synthesis of Quantum-dot Cellular Automata. *IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst.* **2018**, *37*, 3031–3041. [CrossRef]

- 14. Bhoi, B.; Misra, N.; Pradhan, M.; Rout, R. Synthesis methods of baugh-wooley multiplier and non-restoring divider to enhance primitive's results of QCA circuits. In *Smart Intelligent Computing and Applications*; Springer: Singapore, 2019; pp. 237–245.

- 15. Bahar, A.; Wahid, K. Design of QCA-serial Parallel Multiplier (QSPM) with Energy Dissipation Analysis. *IEEE Trans. Circuits Syst. II Express Briefs* **2019**, *67*, 1939–1943. [CrossRef]

- 16. Chu, Z.; Li, Z.; Xia, Y.; Wang, L.; Liu, W. BCD Adder Designs Based on Three-input XOR and Majority Gates. *IEEE Trans. Circuits Syst. II Express Briefs* **2020**, *68*, 1942–1946. [CrossRef]

- 17. Cocorullo, G.; Corsonello, P.; Frustaci, F.; Perri, S. Design of Efficient BCD Adders in Quantum-dot Cellular Automata. *IEEE Trans. Circuits Syst. II Express Briefs* **2016**, *64*, 575–579. [CrossRef]

Electronics **2023**, 12, 3189

18. Abedi, D.; Jaberipur, G. Decimal full adders specially designed for quantum-dot cellular automata. *IEEE Trans. Circuits Syst. II Express Briefs* **2017**, *65*, 106–110. [CrossRef]

- 19. Zhang, T.; Pudi, V.; Liu, W. New Majority Gate-based Parallel BCD Adder Designs for Quantum-dot Cellular Automata. *IEEE Trans. Circuits Syst. II Express Briefs* **2018**, *66*, 1232–1236. [CrossRef]

- 20. Perri, S.; Spagnolo, F.; Frustaci, F.; Corsonello, P. Accuracy Improved Low-Energy Multi-Bit Approximate Adders in QCA. *IEEE Trans. Circuits Syst. II Express Briefs* **2021**, *68*, 3456–3460. [CrossRef]

- 21. Khan, A.; Bahar, A.; Arya, R. Efficient Design of Vedic Square Calculator using Quantum dot Cellular Automata (QCA). *IEEE Trans. Circuits Syst. II Express Briefs* **2021**, *69*, 1587–1591. [CrossRef]

- Jun, K.; Swartzlander, E. Modified Non-restoring Division Algorithm with Improved Delay Profile and Error Correction. In Proceedings of the 2012 Conference Record of the Forty Sixth Asilomar Conference on Signals, Systems and Computers, Pacific Grove, CA, USA, 4–7 November 2012; pp. 1460–1464.

- 23. Mohammadi, M.; Gorgin, S.; Mohammadi, M. Design of non-restoring divider in quantum-dot cellular automata technology. *IET Circuits Devices Syst.* **2017**, *11*, 135–141. [CrossRef]

- 24. Almatrood, A.; Singh, H. QCA Circuit Design of n-bit Non-restoring Binary Array Divider. J. Eng. 2018, 2018, 348–353. [CrossRef]

- 25. Cui, H.; Cai, L.; Yang, X.; Feng, C.; Qin, T. Design of Non-restoring Binary Array Divider in Quantum-dot Cellular Automata. *Micro Nano Lett.* **2014**, *9*, 464–467. [CrossRef]

- Sayedsalehi, S.; Azghadi, M.R.; Angizi, S.; Navi, K. Restoring and Non-restoring Array Divider Designs in Quantum-dot Cellular Automata. Inf. Sci. 2015, 311, 86–101. [CrossRef]

- 27. Sasamal, T.; Singh, A.; Ghanekar, U. Design of Non-restoring Binary Array Divider in Majority Logic-based QCA. *Electron. Lett.* **2016**, *52*, 2001–2003. [CrossRef]

- 28. Kim, S.; Swartzlander, E. Restoring divider design for quantum-dot cellular automata. In Proceedings of the 2011 11th IEEE International Conference on Nanotechnology, Portland, OR, USA, 15–18 August 2012; pp. 1295–1300.

- 29. Yan, A.; Liu, R.; Cui, J.; Ni, T.; Girard, P.; Wen, X.; Zhang, J. Designs of BCD adder based on excess-3 code in quantum-dot cellular automata. *IEEE Trans. Circuits Syst. II Express Briefs* **2023**, 70, 2256–2260. [CrossRef]

- 30. Sekar, K.R.; Marshal, R.; Lakshminarayanan, G. Reliable adder and multipliers in QCA technology. *Semicond. Sci. Technol.* **2022**, 37, 095006. [CrossRef]

- 31. Sekar, K.R.; Marshal, R.; Lakshminarayanan, G. High-speed serial–parallel multiplier in quantum-dot cellular automata. *IEEE Embed. Syst. Lett.* **2022**, *14*, 31–34. [CrossRef]

- 32. Safoev, N.; Samarov, X. Non-restoring QCA Array Divider Using CIXOR Functional Gate. In Proceedings of the 2021 International Conference on Information Science and Communications Technologies, Tashkent, Uzbekistan, 3–5 November 2021; pp. 1–3.

- 33. Kim, H.; Jeon, J. Non-Restoring Array Divider Using Optimized CAS Cells Based on Quantum-Dot Cellular Automata with Minimized Latency and Power Dissipation for Quantum Computing. *Nanomaterials* **2022**, *12*, 540. [CrossRef]

- 34. Patidar, M.; Gupta, N. Efficient Design and Implementation of a Robust Coplanar Crossover and Multilayer Hybrid Full Adder–subtractor Using QCA Technology. *J. Supercomput.* **2021**, 77, 7893–7915. [CrossRef]

- 35. Joy, U.B.; Chakraborty, S.; Das, J.; Tasnim, A.; Jarin, S. Area-Efficient Design of a Quantum-Dot Cellular Automata Based Full Adder Having Low Latency. In Proceedings of the 2022 International Conference on Innovations in Science, Engineering and Technology, Chittagong, Bangladesh, 26–27 February 2022; pp. 77–82.

- 36. Raj, M.; Gopalakrishnan, L. High Speed Memory Cell with Data Integrity in QCA. In Proceedings of the 2019 3rd International conference on Electronics, Communication and Aerospace Technology, Coimbatore, India, 12–14 June 2019; pp. 926–929.

- 37. Yan, A.; Liu, R.; Huang, Z.; Girard, P.; Wen, X. Designs of Level-Sensitive T Flip-Flops and Polar Encoders Based on Two XOR/XNOR Gates. *Electronics* **2022**, *11*, 1658. [CrossRef]

- 38. Zhang, Y.; Zhu, C.; Cheng, X.; Xie, G. Design and Implementation of SRAM for LUT and CLB Using Clocking Mechanism in Quantum-Dot Cellular Automata. *IEEE Trans. Circuits Syst. II Express Briefs* **2022**, *69*, 3909–3913. [CrossRef]

- 39. Perri, S.; Spagnolo, F.; Frustaci, F.; Corsonello, P. Multi-Bit Full Comparator Logic in Quantum-Dot Cellular Automata. *IEEE Trans. Circuits Syst. II Express Briefs* **2022**, *69*, 4508–4512.

- 40. Retallick, J.; Walus, K. Low-energy Eigenspectrum Decomposition (LEED) of Quantum-dot Cellular Automata Networks. *IEEE Trans. Nanotechnol.* **2021**, 20, 104–112. [CrossRef]

- 41. Cong, P.; Blair, E. Robust electric-field input circuits for clocked molecular quantum-dot cellular automata. *IEEE Trans. Nanotechnol.* **2022**, *21*, 424–433. [CrossRef]

- 42. Zhang, T.; Jiang, H.; Mo, H.; Liu, W.; Lombardi, F.; Liu, L.; Han, J. Design of Majority Logic-Based Approximate Booth Multipliers for Error-Tolerant Applications. *IEEE Trans. Nanotechnol.* **2022**, 21, 81–89. [CrossRef]

- 43. Blair, E. Electric-field Inputs for Molecular Quantum-dot Cellular Automata Circuits. *IEEE Trans. Nanotechnol.* **2019**, *18*, 453–460. [CrossRef]

- 44. Wang, L.; Xie, G. A novel XOR/XNOR structure for modular design of QCA circuits. *IEEE Trans. Circuits Syst. II Express Briefs* **2020**, 67, 3327–3331. [CrossRef]

- 45. Bahar, A.; Wahid, K. Design of an Efficient N× N Butterfly Switching Network in Quantum-dot Cellular Automata (QCA). *IEEE Trans. Nanotechnol.* **2020**, *99*, 147–155. [CrossRef]

- 46. Walus, K.; Dysart, T.J.; Jullien, G.A.; Budiman, R.A. QCA Designer: A Rapid Design and Simulation Tool for Quantum-dot Cellular Automata. *IEEE Trans. Nanotechnol.* **2004**, *3*, 26–31. [CrossRef]

Electronics **2023**, 12, 3189

47. Asfestani, M.; Heikalabad, S. A unique structure for the multiplexer in quantum-dot cellular automata to create a revolution in design of nanostructures. *Phys. B Condens. Matter* **2017**, *512*, 91–99. [CrossRef]

- 48. Gassoumi, I.; Touil, L.; Mtibaa, A. An Efficient Design of QCA Full-adder-subtractor with Low Power Dissipation. *J. Electr. Comput. Eng.* **2021**, 2021, 8856399. [CrossRef]

- 49. Yang, B.; Afrooz, S. A new coplanar design of multiplier based on nanoscale quantum-dot cellular automata. *Int. J. Theor. Phys.* **2019**, *58*, 3364–3374. [CrossRef]

- 50. Yan, A.; Chen, Y.; Xu, Z.; Chen, Z.; Cui, J.; Huang, Z.; Girard, P.; Wen, X. Design of double-upset recoverable and transient-pulse filterable latches for low-power and low-orbit aerospace applications. *IEEE Trans. Aerosp. Electron. Syst.* **2020**, *56*, 3931–3940. [CrossRef]

- 51. Song, Z.; Yan, A.; Cui, J.; Chen, Z.; Li, X.; Wen, X.; Lai, C.; Huang, Z.; Liang, H. A Novel Triple-Node-Upset-Tolerant CMOS Latch Design using Single-Node-Upset-Resilient Cells. In Proceedings of the 2019 IEEE International Test Conference in Asia (ITC-Asia), Tokyo, Japan, 3–5 September 2019; pp. 139–144.

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.