## Test and Diagnosis of Integrated Circuits Alberto Bosio

### ▶ To cite this version:

Alberto Bosio. Test and Diagnosis of Integrated Circuits. Micro and nanotechnologies/Microelectronics. Université de Montpellier 2, 2015. tel-01368840

## HAL Id: tel-01368840 https://hal-lirmm.ccsd.cnrs.fr/tel-01368840

Submitted on 20 Sep 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Laboratoire Informatique Robotique Microélectronique Montpellier

## Université de Montpellier

## HABILITATION À DIRIGER LES RECHERCHES

## Test and Diagnosis of Integrated Circuits

*Candidate:* Alberto Bosio Jury: Lorena Anghel Daniel Chillet Said Hamdioui Paolo Montuschi Patrick Girard Bruno Rouzeyre

Vendredi 3 Avril 2015

# Contents

| C  | onter | nts    |                                                                | i             |

|----|-------|--------|----------------------------------------------------------------|---------------|

| Li | st of | Figur  | es esta esta esta esta esta esta esta es                       | iii           |

| Li | st of | Tables | 3                                                              | $\mathbf{iv}$ |

| 1  | Sun   | ımary  |                                                                | 1             |

|    | 1.1   | Curric | ulum Vitae                                                     | 1             |

|    |       | 1.1.1  | Personal Information                                           | 1             |

|    |       | 1.1.2  | Cursus                                                         | 1             |

|    |       | 1.1.3  | Research Interests                                             | 2             |

|    |       | 1.1.4  | Summary of the hot points                                      | 2             |

|    | 1.2   | Summ   | ary of scientific activities                                   | 3             |

|    |       | 1.2.1  | Preamble                                                       | 3             |

|    |       | 1.2.2  | Current research activities                                    | 3             |

|    |       |        | 1.2.2.1 Fault Diagnosis                                        | 3             |

|    |       |        | 1.2.2.2 Power-Aware Test                                       | 4             |

|    |       |        | 1.2.2.3 Test of Low-Power Devices                              | 5             |

|    |       | 1.2.3  | Students                                                       | 6             |

|    |       | 1.2.4  | Research Contracts                                             | 6             |

|    |       | 1.2.5  | Teaching activities                                            | 7             |

|    |       | 1.2.6  | Dissemination of knowledge                                     | 9             |

|    |       | 1.2.7  | Publications                                                   | 9             |

| 2  | Det   | ails   |                                                                | 11            |

|    | 2.1   | Resear | ch activities                                                  | 11            |

|    |       | 2.1.1  | Memory Test (Master and Ph. D. Thesis)                         | 13            |

|    |       | 2.1.2  | Microprocessor Test (Ph. D. Thesis and Post-Doc at Politecnico |               |

|    |       |        | di Torino)                                                     | 14            |

|    |       | 2.1.3  | Functional Verification of IEEE std. 1500 Compliance(Ph. D.    |               |

|    |       |        | Thesis and Post-Doc at Politecnico di Torino)                  |               |

|    |       | 2.1.4  | Diagnosis (from the Post-Doc at LIRMM)                         | 16            |

|    |       |        | 2.1.4.1 From Defects To Fault Models                           | 19            |

|    |       |        | 2.1.4.2 Intra-Cell Diagnosis Flow                              | 21            |

|    |       |        | 2.1.4.3 DUT Simulation                                         | 22            |

|    |       |        | 2.1.4.4 Effect-Cause Intra-cell diagnosis algorithm            | 24            |

|    |       |        | 2.1.4.5 Experimental Results                                   | 29            |

|    |       |        | 2.1.4.6 Conclusions                                            | 36            |

|   |      | 2.1.5 P    | ower-A    | ware Test                                              | 36       |

|---|------|------------|-----------|--------------------------------------------------------|----------|

|   |      | 2          | .1.5.1    | The Proposed Methodology                               | 38       |

|   |      | 2          | .1.5.2    | Case Study                                             | 41       |

|   |      | 2          | .1.5.3    | Conclusions                                            | 47       |

|   |      | 2.1.6 T    | Cest of L | ow Power Devices                                       | 48       |

|   |      | 2          | .1.6.1    | Low-Power Sram: Architecture And Functioning           | 49       |

|   |      | 2          | .1.6.2    | Resistive-Open Defects In The Power Mode Control Logic | 54       |

|   |      | 2          | .1.6.3    | Failure Analysis In Presence Of Df6                    | 56       |

|   |      | 2          | .1.6.4    | Test Solution                                          | 63       |

|   |      | 2          | .1.6.5    | Conclusions                                            | 66       |

|   | 2.2  | Students   |           |                                                        | 66       |

|   |      | 2.2.1 N    | laster s  | tudents                                                | 66       |

|   |      | 2          | .2.1.1    | Master 1                                               | 66       |

|   |      | 2          | .2.1.2    | Master 2                                               | 66       |

|   |      | 2.2.2 P    | h.D. sti  | udents                                                 | 67       |

|   | 2.3  | Teaching   | g activit | ies                                                    | 72       |

|   | 2.4  | Research   | n Contra  | nets                                                   | 75       |

|   | ъ    |            |           |                                                        | =0       |

| 3 |      | spectives  |           |                                                        | 79<br>70 |

|   | 3.1  |            |           | pective                                                | 79       |

|   | 3.2  |            |           | erspective                                             |          |

|   | 3.3  | Long-ter   | m Persp   | pectives                                               | 84       |

| 4 | Pub  | olications | 5         |                                                        | 87       |

|   | 4.1  | Books .    |           |                                                        | 87       |

|   | 4.2  | Patents    |           |                                                        | 87       |

|   | 4.3  | Journals   |           |                                                        | 87       |

|   | 4.4  | Invited I  | Papers    |                                                        | 88       |

|   | 4.5  | Conferen   | nces      |                                                        | 89       |

|   | 4.6  |            |           |                                                        | 94       |

| 5 | Sele | ection of  | 5 best    | papers                                                 | 95       |

### Bibliography

154

# List of Figures

| Physical defects modeling 19                                           |

|------------------------------------------------------------------------|

| Overall diagnosis flow                                                 |

| Local test patterns                                                    |

| ocal test patterns taxonomy                                            |

| Intra-cell diagnosis pseudo code                                       |

| Logic values intersection                                              |

| pfa result                                                             |

| Physical failure analysis result                                       |

| Layout view                                                            |

| Layout view                                                            |

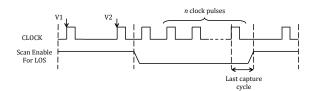

| Functional patterns time window                                        |

| LOS patterns time window 40                                            |

| Pseudo functional patterns time window                                 |

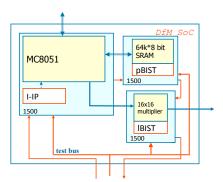

| SoC Architecture                                                       |

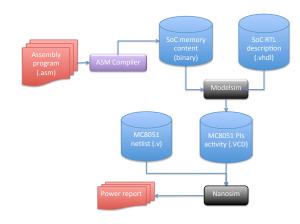

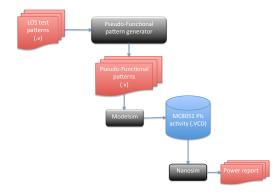

| Functional patterns power estimation flow                              |

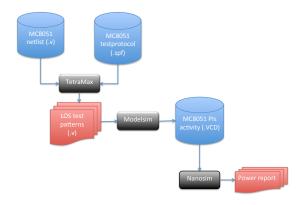

| LOS patterns power estimation flow                                     |

| Pseudo functional patterns power estimation flow                       |

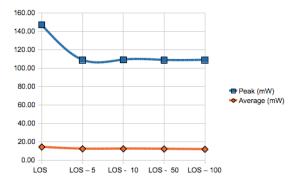

| Behavior of LOS and pseudo-functional patterns                         |

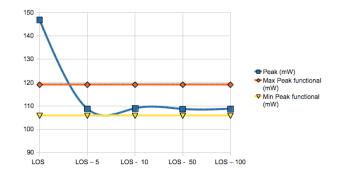

| Behavior of Functional and Pseudo-functional patterns                  |

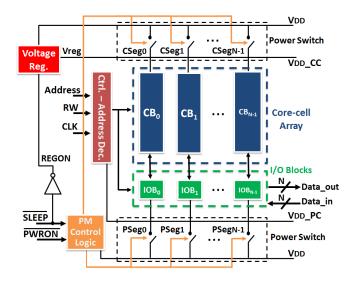

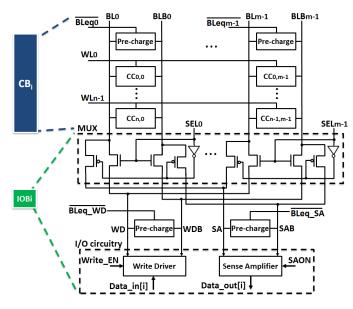

| Low-power SRAM architecture                                            |

| SRAM memory element                                                    |

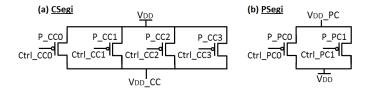

| Segment of power switches                                              |

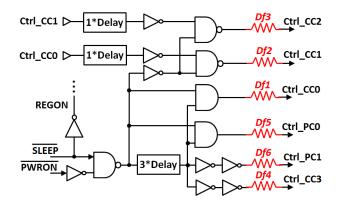

| Power mode control logic                                               |

| Generation of control signals 57                                       |

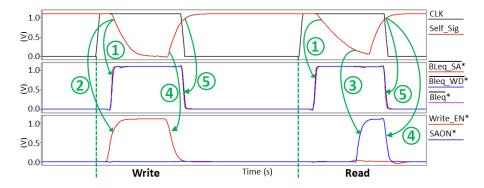

| Experimental Scenario 1                                                |

| Experimental Scenario 2                                                |

| Over and Under Test phenomena                                          |

| Cross sectioning and delayering of dies showing the defect location as |

| identified by the PFA 82                                               |

| Heterogeneous System-on-Chip                                           |

| Proposed Principle of Power Aware Auto-Adaptive Mechanism 86           |

|                                                                        |

# List of Tables

| Students Summary                                         | 6                   |

|----------------------------------------------------------|---------------------|

| Teaching Activities                                      | 8                   |

| Publications Summary                                     | 10                  |

| Circuit Characteristics                                  | 30                  |

| SAF Results                                              | 31                  |

| BF Results                                               | 31                  |

| DF Results                                               | 31                  |

| Experimental Results                                     | 32                  |

| Circuit Characteristics                                  | 32                  |

| Logic diagnosis vs intra-cell diagnosis vs actual defect | 33                  |

| MC8051                                                   | 41                  |

| Functional Patterns Power Estimation                     | 45                  |

| LOS And Pseudo-Functional Patterns Power Estimation      | 45                  |

| Summary of the Ph.D. Students                            | 67                  |

|                                                          | Teaching Activities |

## Chapter 1

## Summary

### 1.1 Curriculum Vitae

#### 1.1.1 Personal Information

- Name: Alberto BOSIO

- **Date and Place of Birth:** 3 March 1977, Fossano (Italy)

- Nationality: Italian

- Personal address: 683, Avenue du Pére Soulas, 34090 Montpellier, France

- Current position: Maître de conférences CNU 61

- Work address: LIRMM, UMR 5506, 161 rue Ada, 34392 Montpellier Cedex 5, France

- **Work phone:** 04 67 41 85 76

- **Fax:** 04 67 41 85 00

- **Email:** alberto.bosio@lirmm.fr

#### 1.1.2 Cursus

- From september 2007: "Maître de conférences" at LIRMM/Université de Montpellier 2

- **2006-2007:** Post-Doc at LIRMM

- **2005-2006:** Post-Doc at Politecnico di Torino, Computer Science Department

- 2003-2005: Ph.D. degree in Computer Engineering from Politecnico di Torino. Title: "Dependable Architectures for Safety-Critical Applications"

- **2003:** National Engineering habilitation exam, Turin, Italy

- 2002: Master degree in Computer Engineering from Politecnico di Torino. Title: "Automatic March Test Generator"

- **1996:** High School degree (Computer Science Technical Institute), Fossano, Italy

#### 1.1.3 Research Interests

- Memory and Microprocessor Testing

- Digital Testing and Design for Testability

- ATPG, Fault Simulation

- Diagnosis

- Power Aware Test

- Test of Low Power Devices

#### 1.1.4 Summary of the hot points

- Co-author of 1 book, 11 international journal papers, more than 50 papers and presentations in international conferences and 2 patents

- Co-supervisor of 8 PhD students and 20 master students

- Participation to overall 7 research contracts

- Web chair of the TTTC, ETS

- Web chair of: BTW'10, BTW'11, BTW'12, BTW'14, ETS'13

- Publication chair of: SIES'08, DTIS'14, DTIS'15, ETS'15, ETS'16

- Member of the program committee of several international conferences and reviewers for several journals

#### **1.2** Summary of scientific activities

#### 1.2.1 Preamble

I have carried out all my studies in Italy. Moreover, after a PhD in Computer Engineering in the domain of the test and verification of digital systems at the Politecnico di Torino (Italy), I pursued 1 year of post-doc research at the same institute still in the same domain. Thanks to cooperations between the Politecnico di Torino and the LIRMM of Montpellier, I had the opportunity to obtain a post-doc position in France. There, in addition to the topics which were already familiar to me, I had the occasion to explore new fields in the test topic: the diagnosis and the power-aware test. My scientific results, students I have supervised, my teaching activities, and in general my research projects directly reflects my career path.

#### 1.2.2 Current research activities

Research activities I carried on after my nomination as Maître de conférences deal with three main axes: the fault diagnosis, the power-aware test and the test of low-power devices. In the next subsections I will introduce each research axe, the details are given in the Chapter 2 Section 2.1.

#### 1.2.2.1 Fault Diagnosis

The ever-increasing growth of the semiconductor market results in an increasing complexity of digital circuits. Smaller, faster, cheaper and low-power consumption are the main challenges in semiconductor industry. The reduction of transistor size and the latest packaging technology (i.e., System-On-a-Chip, System-In-Package, Trough Silicon Via 3D Integrated Circuits) allows the semiconductor industry to satisfy the latest challenges. Although producing such advanced circuits can benefit users, the manufacturing process is becoming finer and denser, making chips more prone to defects. Physical defects like shorts and opens will occur during any single step of the fabrication process. These defects can be randomly caused by contaminations or due to systematic processdesign interaction [1]. In modern deep submicron technologies, systematic defects are becoming more likely to appear than random defects. This is caused by the reduced chip sizes, the use of new complex process technologies, new materials and the increasing number of vias and contacts [2]. Today, systematic defects appear not only in the cell interconnection, but also inside the cell itself (intra-cell defect). The test is one of the most critical tasks in the semiconductor production process. It is not only necessary to seek for fault free devices but it plays a key role in analyzing defects in the manufacturing process as well. The feedbacks derived from the test process are the only way to analyze and isolate many of the defects in today's processes enabling to obtain a fast and efficient yield ramp-up. Fault Diagnosis plays a crucial role in this scenario, since test can only provide information on the system behavior (good/no good). Fault diagnosis starts from the test response with the aim to locate the faulty part of the circuit and then identify which is the source of the observed failures. Unraveling the location and cause of the defect helps to improve both the circuit design and the manufacturing process, thus leading to a lower cost, an improved yield and a shorter time-to-market.

The main contributions of this work focus on the development of efficient diagnosis approach targeting digital circuits.

#### 1.2.2.2 Power-Aware Test

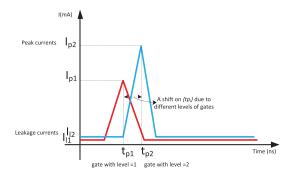

Nowadays, electronic products present various issues that become more important with CMOS technology scaling. High operation speed and high frequency are mandatory requests. On the other hand, power consumption is one of the most significant constraints due to large diffusion of portable devices. These needs influence not only the design of devices, but also the choice of appropriate test schemes that have to deal with production yield, test quality and test cost.

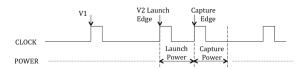

Testing for performance, required to catch timing or delay faults, is therefore mandatory, and it is often implemented through at-speed scan testing for logic circuits. At-speed scan testing consists of using a rated (nominal) system clock period between launch and capture for each delay test pattern, while a longer clock period is normally used for scan shifting (load and unload cycles).

In order to test for transition delay faults, two different schemes are used in practice during at-speed scan testing: Launch-off-Shift (LOS) [12] and Launch-off-Capture (LOC) [13].

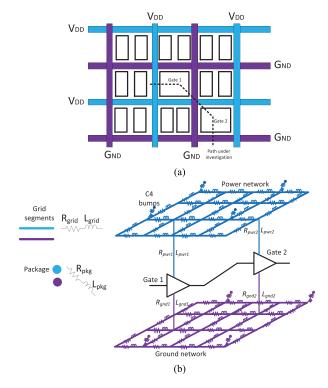

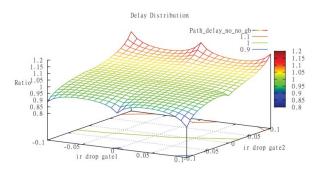

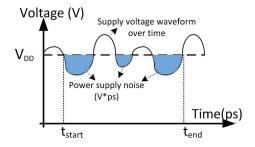

Although at-speed scan testing is mandatory for high- quality delay fault testing, its applicability is severely challenged by test-induced yield loss, which may occur when a good chip is declared as faulty during at-speed scan testing [15]. Both schemes (LOS and LOC) may suffe from this problem, whose the major cause is Power Supply Noise (PSN), i.e., IR- drop and Ldi/dt events, caused by excessive switching activity (leading to excessive power consumption) during the launch- to-capture cycle [16] of delay testing

schemes. In order to deal with this problem, dedicated techniques to reduce the risk of artificial yield loss induced by excessive PSN during at-speed scan testing have been proposed in the literature [17]. These techniques are mainly based on test pattern modification or power-aware Design-for-Testability (DfT).

Despite the fact that reduction of test power is mandatory to minimize the risk of yield loss, some experimental results have proved that too much test power reduction might lead to test escape and reliability problems because of the under-stress of the circuit during test [18]. So, in order to avoid any yield loss and test escape due to power issues during test, test power has to map the power consumed during functional mode. To this purpose, the knowledge of functional power for a given CUT is required and can be exploited as a reference for defining the power consumption (upper and lower) limits during power-aware delay test pattern generation for LOS or LOC.

The main contributions of this work is the development of meaningful test solutions respecting the power-constraints.

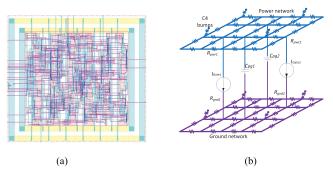

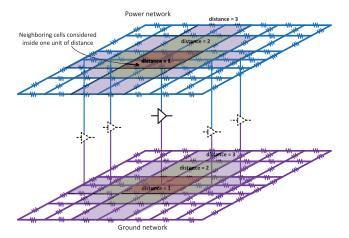

#### 1.2.2.3 Test of Low-Power Devices

System-on-chips (SOCs) have found their application in every latest hand-held consumer devices, such as smart phones, PDAs, digital cameras and other mobile applications. This is because SOCs designed with deep-submicrometer technologies can integrate all components and functions that historically were placed on a printed-circuit board. This trend allows SOCs to embrace a variety of IP cores, such as embedded processors, MPEG encoders/decoders, DSPs, embedded memories, etc.

The need of power efficient electronic devices leads to implement dedicated structures to reduce as much as possible the power consumption. These needs influence not only the design of devices, but also the choice of appropriate test schemes or eventually design the novel DfT structures that have to deal with production yield, test quality and test cost (ITRS).

The overall SoC power consumption has two contributors: (i) dynamic and (ii) static power. While the dynamic power is strictly related to the running application, the static power is only dependent on the leakage currents. As shown in [24], static power consumption is becoming the most important contributor to the overall power consumption especially for the latest technologies (i.e., under 65nm). In order to reduce the static power consumption the so-called power-gating techniques have been proposed so far. The power-gating relies on splitting the SoC into different blocks called power islands. Each power island can be switched on/off independently of the others. Using this technique, if one or more power islands are not used by the running application, they are switched off, in order to reduce the static power consumption.

The main contributions of this work is the analysis of the impact of defects in the power-gating circuitry and in the development of efficient test solutions.

#### 1.2.3 Students

After my Ph.D. I have co-supervised 8 Ph.D. students and 20 master students. Table 1.1 summarizes Ph.D. students in chronological order. Master students are not listed in this table for the sake of simplicity. Section 2.2 of Chapter 2 will describe the work of each student in detail.

TABLE 1.1: Students Summary.

#### 1.2.4 Research Contracts

Starting from my Ph.D., I have cooperated to national- and european-funded research contracts. The following list summarizes each contract. Details are given in Chapter 2 Section 2.4

- 2005-2008: Participation to NanoTEST project (European MEDEA+ 2A702) that has the ambition to create a breakthrough in methods and flows used by the test technologies by considering the test in the whole value chain from Design to Application. A strong consortium composed of European Semiconductor industries, Academics and Small and Medium Enterprises has grouped their competences to successfully address this challenge

- 2007-2009: Participation to the contract with STM Crolle ("Bourse Cifre")

- 2008-2011: Participation to TOETS project (European CATRENE CT302) that is the continuation of the NanoTEST project

- 2011-2013: Participation to the contract with INTEL that focuses on the test of low-power SRAMs

- 2011-2014: Participation to the contract with STE ("Bourse Cifre")

- 2011-2014: Participation to the contract with STE Grenoble ("Bourse Cifre")

- 2013-2016: Participation to LIA LAFISI (CNRS and Université de Montpellier 2 funded international laboratory) that has the following main objectives:

- Synergize research efforts on all aspects of test and fault tolerance of hardwaresoftware integrated systems, from the circuit to system level.

- Promote joint education of students to research careers and set up advanced course programs, summer schools, or research internships.

- Facilitate diffusion of a scientific culture of high quality in the field of hardwaresoftware integrated systems.

- Set up the necessary means for the valorization and technological transfer of research results obtained in the framework of the LIA.

#### 1.2.5 Teaching activities

Starting from my Ph.D. studies, I have performed various teaching activities at Politecnico di Torino, University of Montpellier 2 and the USTH, students of private institutions. Table 1.2 summarizes my pedagogical activities. The column dedicated to the time spent for each subject is classified in 3 set: lectures (i.e., "Cours Magistraux" and "Travaux Dirigés"), and practical work (i.e., "Travaux Pratique").

| (                               |                 |                                         | Ho       | Hours     |                             |

|---------------------------------|-----------------|-----------------------------------------|----------|-----------|-----------------------------|

| Course                          | Subject         | Period                                  | Lectures | Practical | Location                    |

|                                 |                 | 2003/04                                 | 0        | 25        | Dolitomino di Tomino        |

| Computer Science                | o lauguage      | 2004/05                                 | 0        | 25        |                             |

|                                 | C, C+ languages | from $2007/08$ until now                | 108      | 114       | Université de Montpellier 2 |

| Dicital Sustan Tacting          | Memory Test     | 2004/05                                 | 12       | 0         | Politecnico di Torino       |

| Digital Dystelli results        | ATPG, Fault     | from $2009/10$ until now                | 42       | 16        | Polytech' Montpellier       |

|                                 | Simulation      |                                         |          |           |                             |

| Computer Network                | TCP/IP          | from $2007/08$ until now                | 75       | 0         | Université de Montpellier 2 |

| Digital System Design           | Synthesis and   | from 2007/08 until now                  | 30       | 162       | Université de Montpellier 2 |

| )<br>)                          | VHDL language   |                                         |          |           |                             |

|                                 | Synthesis       | from $2011/12$ until now                | 30       | 45        | University of Science and   |

|                                 |                 |                                         |          |           | Technology of Hanoi         |

| Administed MDSoff Analytication | Concurrent Pro- | Concurrent Pro- from 2007/08 until now  | 105      | 42        | Université de Montpellier 2 |

| AUVALUEU IVI DUU ALUIUVEUULE    | gramming        |                                         |          |           |                             |

|                                 | Concurrent Pro- | from $2011/12$ until now                | 30       | 45        | University of Science and   |

|                                 | gramming and    |                                         |          |           | Technology of Hanoi         |

|                                 | Fault Tolerance |                                         |          |           |                             |

|                                 |                 |                                         |          |           |                             |

|                                 | TABL            | TABLE 1.2: Teaching Activities Summary. | ummary.  |           |                             |

| Summary.   |

|------------|

| Activities |

| Teaching   |

| 1.2:       |

| ABLE       |

#### 1.2.6 Dissemination of knowledge

- International Symposium on Industrial Embedded Systems (SIES): Publication Chair (2008)

- Design and Test of Integrated Circuits (DTIS): Publication Chair (2014 and 2015)

- European Test Symposium (ETS): Publication Chair (ETS'15)

- South European Test Seminar (SETS): General Chair (2014)

- "Testing, Reliability, and Fault-Tolerance" Track Chair of ISVLSI'15

- Program Committee: ISQED (from 2009), DDECS (from 2011), ETS (from 2013)

- Web Master of the "Test Technology Technical Council" (tab.computer.org/tttc) of IEEE Computer Society (from 2012)

- Web Master of the "European Test Symposium" general home (http://www.ieeeets.org/) from 2012

- $\blacksquare$  Web Master of ETS'13

- Web Master of BTW'10, BTW'11, BTW'12 and BTW'14

- Reviewer for the following main Journals: IEEE Transaction on VLSI, IEEE Transaction on Computer, Journal of Electronic Testing Theory and Applications, IET Computers & Digital Techniques

- Reviewer for the following main conferences: DAC, ITC, VTS, ETS, ATS

- Paper on IEEE Transaction on Computer, awarded by a movie published at "Computing Now" (http://www.computer.org/portal/web/computingnow/1211/whatsnew/tc)

#### 1.2.7 Publications

Table 1.3 summarizes the number of my publications for each year, classified by patent, book, journal papers (with review process), papers published in official proceedings (coming from conferences or workshops with review process). The complete list of publications is given in Chapter 4.

| Year  | Patent  | Book | Journal |         | Prooceding |          | Total |

|-------|---------|------|---------|---------|------------|----------|-------|

| Tear  | 1 atent | DOOK | Journai | Invited | Conference | Workshop | 100a1 |

| 2005  | 0       | 0    | 0       | 0       | 2          | 0        | 2     |

| 2006  | 0       | 0    | 0       | 1       | 6          | 1        | 8     |

| 2007  | 0       | 0    | 1       | 0       | 4          | 1        | 6     |

| 2008  | 0       | 0    | 2       | 0       | 4          | 1        | 7     |

| 2009  | 0       | 1    | 1       | 0       | 5          | 0        | 7     |

| 2010  | 0       | 0    | 2       | 0       | 5          | 0        | 7     |

| 2011  | 0       | 0    | 0       | 2       | 8          | 0        | 10    |

| 2012  | 0       | 0    | 1       | 1       | 5          | 0        | 6     |

| 2013  | 0       | 0    | 2       | 0       | 4          | 0        | 6     |

| 2014  | 2       | 0    | 2       | 0       | 4          | 1        | 10    |

| Total | 2       | 1    | 11      |         | 55         | •        | 69    |

TABLE 1.3: Publications Summary.

## Chapter 2

## Details

### 2.1 Research activities

This section summarizes the research activities I carried out starting from my master thesis in 2002.

#### Research activities at Politecnico di Torino

Since 2002, I worked in the area of test of digital systems and dependability for safetycritical applications at the Politecnico di Torino (Italy), in cooperation with Prof. Paolo Prinetto's research group. My research activity mainly focused on the definition of new methodologies and the implementation of tools able to improve the development of highly dependable systems, at different levels: for basic digital components, for systems on chip, up to microprocessor-based systems.

My research activity, developed during 1 year of master thesis, plus 3 years of PhD and 1 years of PostDoc focused on test and functional verification of digital systems and . In particular I worked on the following topics:

- Definition of functional fault models for memories RAM and automatic generation of test sequences (Section 2.1.1);

- Definition of functional test generation methodology for RISC microprocessor cores (Section 2.1.2);

- Definition of a design environment to verify the system core-wrapper 1500-Compliance with the purpose to assure that the component can be successfully integrated in a SoC (Section 2.1.3).

#### **Research activities at LIRMM**

Starting from November 2006 I started working at LIRMM with the group of Patrick Girard and Serge Pravossoudovitch still working on the test topic but now focusing on diagnosis, power-aware test and test of low-power devices. In the following I will detail the main contributions.

The diagnosis is the process of isolating possible sources of observed failures in a defective circuit. Today, manufacturing defects appear not only in the cell interconnection, but also inside the cell itself (intra-cell defect). State of the art diagnosis approaches can identify the defect location at gate level (i.e, one or more standard cells and/or interconnections can be provided as possible defect location). Some approaches have been developed to target the intra-cell defects. In this work, we propose an intra-cell diagnosis method based on the "Effect-Cause" paradigm aiming at locating the root cause of the observed failures inside a logic cell. It is based on the Critical Path Tracing (CPT) here applied at transistor level. The main characteristic of our approach is that it exploits the analysis of the faulty behavior induced by the actual defect. In other word, we locate the defect by simply analyzing the effect induced by the defect itself. The advantage is the fact that we are defect independent (i.e., we do not have to explicitly consider the type and the size of the defect). Moreover, since the complexity of a single cell in terms of transistor number is low, the proposed intra-cell diagnosis approach requires a negligible computational time. The efficiency of the proposed approach has been evaluated by means of experimental results carried out on both simulations-based and industrial silicon data case studies. This activity is described in Section 2.1.4.

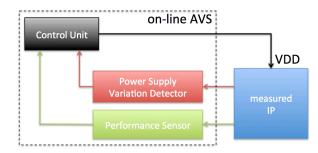

High power consumption during test may lead to yield loss and premature aging. In particular, excessive peak power during at-speed delay fault testing represents an important issue. In the literature, several techniques have been proposed to reduce peak power consumption during at-speed LOC or LOS delay testing. On the other hand, some experiments have proved that too much test power reduction might lead to test escape and reliability problems. So, in order to avoid any yield loss and test escape due to power issues during test, test power has to map the power consumed during functional mode. In literature, some techniques have been proposed to apply test vectors that mimic functional operation from the switching activity point of view. In this work, we propose a novel flow to determine the functional power to be used as test power (upper and lower) limits during at-speed delay testing. This activity is described in Section 2.1.5.

In low-power SRAMs, power gating mechanisms are commonly used to reduce static power consumption. When the SRAM is not accessed for a long period, such mechanisms allow shutting off one or more memory blocks (core-cell array, address decoder, I/O logic, etc), thus reducing leakage currents. In order to guarantee static power reduction in low-power SRAMs, reliable operation of power gating mechanisms must be ensured by adequate test techniques. In this work, we first present a detailed analysis based on electrical simulations to identify faulty behaviors caused by realistic defects that may affect power gating mechanisms embedded in low-power SRAMs. Based on this analysis, we present an efficient test solution targeting detection of observed faulty behaviors. This activity is described in Section 2.1.6.

#### 2.1.1 Memory Test (Master and Ph. D. Thesis)

Embedded memories are the densest components within a System on Chip (SoC), accounting for up to 90% of its real size. Today's technologies allow the design and manufacturing of memory cores with many I/O ports, and multi-port RAM core generators are commonly available in many ASIC vendors library. To have an idea of today's SoC complexity, it is enough to consider that typically more than 30 embedded memories are placed on a single chip, they are scattered around the device rather than concentrated in one location, they all have different types, sizes, and access protocols and timing, and they can even be doubly embedded inside embedded cores. Many activities have been devoted to Built-In Self-Test of embedded memories. In this context, the research activity focused then on the definition of test algorithms for memories. Among the different types of algorithms proposed to test random access memories (RAM), March Tests have proven to be faster, simpler, regularly structured and linear in complexity. A March Test consists of a sequence of March Elements, each composed by a sequence of basic read/write operations to be performed on each cell of the memory, in either ascending or descending order, before proceeding to the next memory cell. The majority of the published March Tests has been manually generated; unfortunately, the continuous evolution of the memory technology requires the constant introduction of new classes of faults, such as dynamic and linked faults, and makes the task of hand-writing test algorithms harder and not always leading to optimal results. Although some researchers published hand-made March Tests able to deal with new fault models, the problem of a comprehensive methodology to automatically generate March Tests for SRAMs, addressing both classic and new fault models, is still an open issue. This work proposed a new approach to the automatic generation of March Tests. The formal model adopted to represent memory faulty behaviors allows the definition of a general methodology to deal with both the most important classes of memory faults (Dynamic, Static, and also linked faults), and even new user-defined fault models. Experimental results show that the new automatically generated March Tests can reduce the test complexity, and

therefore the test time, compared to the well-known state of the art in memory testing of about 15%.

This work and its extension are published in [W1, C1, C2, C4, C5, C6, C8, C15, C26, C28, J1, J2, J3] referenced in the Publication list of chapter 4.

### 2.1.2 Microprocessor Test (Ph. D. Thesis and Post-Doc at Politecnico di Torino)

In order to guarantee very high performance, a large number of SoC designs are built around embedded RISC microprocessor or digital signal processor (DSP) cores. Nevertheless, due to the high complexity and the limited accessibility of their internal logic, embedded microprocessor cores often introduce testability issues. As an example, Scan Chains insertion is often avoided not to impact the processor performance and therefore structural testing of a microprocessor core is usually unfeasible. Several alternative approaches have been developed in the last years. The most successful are called Software-Based Self-Test (SBST) and are based on the idea of testing the microprocessor by having it executing a given and predetermined list of instructions. The list of executed instructions constitutes the test program. Test programs are usually stored either in a dedicated ROM or loaded into a RAM by an external system (i.e. ATE or the Operating System). The main advantages are that no extra area is required and the test is executed by the microprocessor itself (at-speed test). Several methodologies have been proposed to generate the test programs. The empirical approach requires neither a microprocessor nor a fault model. This approach is fairly easy to apply but lacks of a formal way to compute the fault coverage or the quality of the test program. Other researchers propose the use of pseudo-random sequences of instructions, where both operands and/or instructions could be randomized, and or deterministic sequences of instructions. The deterministic approach demonstrated to be better than the pseudorandom one both in the final coverage of functional faults and the overall test time (and therefore number of instructions in the program). Despite their efficiency, many of the suggested approaches lack of focus on the more complex functional blocks, like the pipelining interlock mechanism or the cache hierarchy. In the test of a microprocessor core used in critical applications none of these blocks can be ignored. This research activities led to a test generation methodology designed to build a non-concurrent online test of a RISC microprocessor core; the proposed solution allows to generate very complex test programs based on a deterministic SBST approach and to execute them under very tight timing constraints. The presented case study is a Motorola PowerPC 603 Microprocessor core for which, to our knowledge, no SBST solution has ever been published.

The proposed methodology is defined in four steps:

- Identification of all the functional components of the target microprocessor;

- Identification of the fault models for each component;

- Collection of the state of the art about the test strategies available for each component;

- Development of the test programs.

This work and its extension are published in [C3, I1, J7] referenced in the Publication list of chapter 4.

# 2.1.3 Functional Verification of IEEE std. 1500 Compliance(Ph. D. Thesis and Post-Doc at Politecnico di Torino)

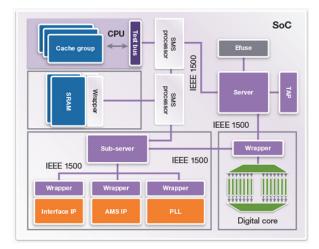

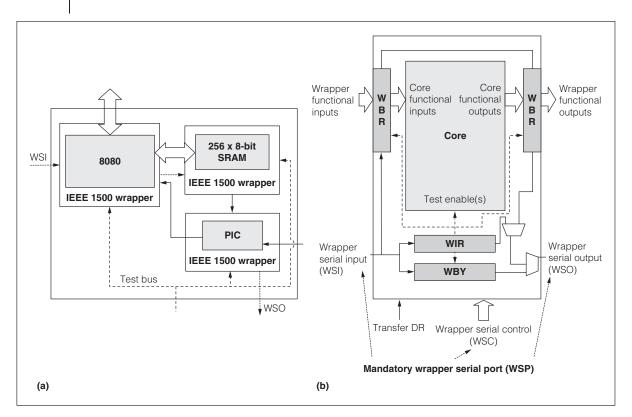

The race to market high-volume quality products demands a shorter design-to-manufacturing cycle, forcing System-on- Chip (SoC) designers to strongly rely on Intellectual Property (IP) cores from multiple sources. The shorter time-to-volume requires faster silicon bring-up with a high degree of diagnosability. This means being able to isolate each embedded core during test and debug activities. The adoption of adequate test and diagnosis strategies is therefore a major challenge in modern SoCs production. The IEEE Standard Testability Method for Embedded Core-Based Integrated Circuits (IEEE std. 1500) addresses the specific challenges that come with testing deeply embedded reusable cores supplied by different providers, who often use different hardware description levels and mixed technologies. It defines a comprehensive set of guidelines for building the core test infrastructure. It includes:

- A Core Test Wrapper: a wrapper placed around the boundaries of the core that allows accessing its testing functionalities using a standard interface and protocol. The wrapper is completely transparent when the core is not in test mode;

- An Information Model: a formal description of the IEEE std. 1500 functionalities implemented by the Core Test Wrapper. The standard supports many functionalities, some mandatory and some optional. The Information Model is the bridge between core providers and core users and facilitates the automation of test data transfer and reuse between these two entities. The Information Model is described using the IEEE std. 1450.6 Core Test Language (CTL) and includes:

- The set of wrapper's signals;

- The wrapper communication protocol;

- Information about test patterns.

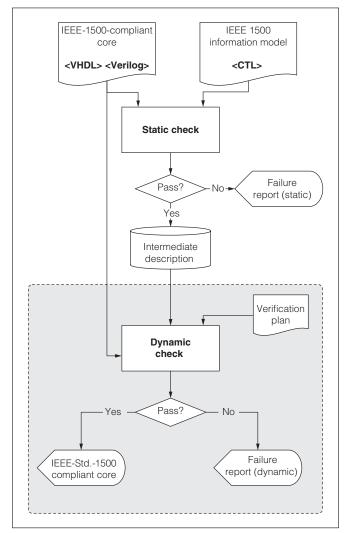

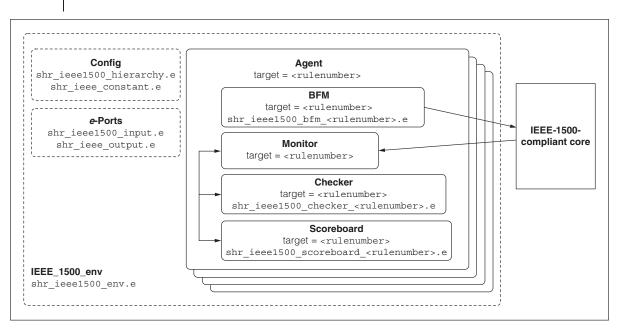

Some literature presents solutions to build SoCs with IEEE std. 1500 testability features; nevertheless, by analyzing the standard, it is clear that implementing a fully compliant core is not a trivial task. The need to support as wide a range of embedded core test applications as possible has led to a very flexible solution. The IEEE std. 1500 specifies a mandatory minimal set of hardware support. However, a designer can extend the test infrastructure by creating virtually unlimited sets of registers and instruction extensions. An IEEE std. 1500 compliant design is therefore exposed to a range of possible design errors that require to be early identified and fixed. A comprehensive approach to thoroughly verify the functionality of IEEE std. 1500 wrappers and wrapped cores in a SoC environment is therefore mandatory. The problem of verifying the compliance of an IP core to the IEEE std. 1500 has been poorly addressed in literature. The main drawbacks of the existing solutions are that, for each core, the verification module must be configured by hand and that the verification strategy, i.e. the order used to verify each aspect (rule) of the standard, is fixed. Moreover, the authors verify the SoC and wrapper functionalities without systematically addressing every single aspect (rule) of the standard. To overcome these problems, we present a verification framework based on the use of the UML language, designed to systematically address the verification of the standard. Besides providing the actual implementation of the framework, this work focuses on the definition of an abstract model of the standard enabling core providers andor integrators to build their custom verification environments. Starting from the abstract model proposed in, it is possible to build a verification environment for the IEEE std. 1500. In particular we will show how the functionalities provided by Specman EliteTM(Cadence), a commercial functional verification EDA can be used to implement such a verification environment.

This work and its extension are published in [C9, W2, J4] referenced in the Publication list of chapter 4.

#### 2.1.4 Diagnosis (from the Post-Doc at LIRMM)

The ever-increasing growth of the semiconductor market results in an increasing complexity of digital circuits. Smaller, faster, cheaper and low-power consumption are the main challenges in semiconductor industry. The reduction of transistor size and the latest packaging technology (i.e., System-On-a-Chip, System-In-Package, Trough Silicon Via 3D Integrated Circuits) allows the semiconductor industry to satisfy the latest challenges. Although producing such advanced circuits can benefit users, the manufacturing process is becoming finer and denser, making chips more and more prone to defects.

Physical defects like shorts and opens will occur during each step of the fabrication process. These defects can be randomly caused by contaminations or due to systematic process-design interaction [1]. In modern deep submicron technologies, systematic defects are becoming more likely to appear than random defects. This is caused by the reduced chip sizes, the use of new complex process technologies, new materials and the increasing number of vias and contacts [2]. Today, systematic defects appear not only in the cell interconnection, but also inside the cell itself (intra-cell defect). In the literature, existing works prove that these defects can escape classical test solutions.

The test is one of the most critical tasks in the semiconductor production process. It is not only necessary to seek for fault free devices but it plays a key role in analyzing defects in the manufacturing process as well. The feedbacks derived from the test process are the only way to analyze and isolate many of the defects in today's processes enabling to obtain a fast and efficient yield ramp-up.

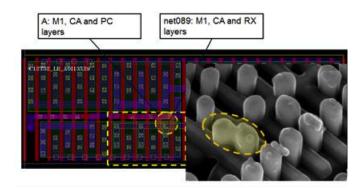

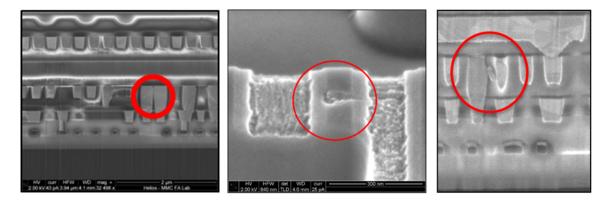

Fault Diagnosis plays a crucial role in this scenario, since test can only provide information on the system behavior (good/no good). Fault diagnosis starts from the test response with the aim to locate the faulty part of the circuit and then identify which is the source of the observed failures. Unraveling the location and cause of the defect helps to improve both the circuit design and the manufacturing process, thus leading to a lower cost, an improved yield and a shorter time-to-market. State of the art fault diagnosis approaches can identify the defect location at gate level (i.e, one or more standard cells and/or inter-connections can be provided as possible defect location) [30]. The fault diagnosis results (i.e., possible defect locations) are then further used in defect analysis, where the circuit is physically examined to determine the mechanism of the failure. Physical Failure Analysis (PFA) is physical analysis that corresponds to the physical identification of the defect. It mainly consists in selective de-layering and crosssectioning of a die. PFA is not only crucial and time-consuming but also destructive and irreversible. Therefore, a preliminary diagnosis procedure is mandatory to correctly guide the PFA to eventually save time and increase success rate.

As previously discussed, state of the art fault diagnosis approaches are able to locate the possible defect at gate level (i.e., inter-cell). Therefore, in the case of circuit affected by intra-cell defects, results of inter-cell fault diagnosis may cause problems and impact the efficient of the PFA. So that, PFA may take more time to identify the actual defects. Moreover, in the worst case, PFA may fail (i.e., it does not identify the root cause of the observed error) and it can destroy the circuit. The solution is to develop an efficient diagnosis approach able to target intra-cell defects.

To the best of our knowledge, commercial tools only target inter-cell fault diagnosis, while in the literature some research works already addressed the intra-cell fault diagnosis problem [10, 11, 31]. The approach of [11] is based on the use of a defect dictionary. The dictionary is created by means of defect injection campaign at transistor level. During diagnosis, the observed failures are used to search in to the defect dictionary the most suitable defect location and type. However, the need of pre-computed defect dictionary for each cell and defect type makes this approach highly complex. Moreover, if the injected defect is not accurate enough it can lead to erroneous results during diagnosis.

The approach of [31] is based on the use of a fault dictionary. The main difference w.r.t. [11] is that the dictionary is created exploiting a switch-level simulation (i.e., the transistors are considered as switches). Thus, instead of injecting defects, only fault models are injected. The advantage is the reduced simulation time compared to [11]. Two types of fault are considered, the stuck-at and dominant bridging fault. These faults are modeled at switch-level in order to be simulated and to create the related fault dictionary. However, defects leading to delay faults are not targeted. Moreover, to include delay faults or other types of faults a switch-level model of them has to be defined.

The approach of [10] proposes to convert transistor level netlist into an equivalent gate level netlist. Then classical inter-cell fault diagnosis tools can be applied. The main drawback of this approach is that the set of transformation rules depends on targeted defect types.

Due to the drawbacks and limitations of previous works on intra-cell diagnosis, it is necessary to develop an efficient and accurate intra-cell diagnosis solution to ensure the PFA success rate. In this work we propose a new intra-cell diagnosis approach able to provide accurate defect localization in order to improve the efficiency of PFA and to eventually save cost and time. The main characteristic of our approach is that it exploits the analysis of the faulty behavior induced by the actual defect. In other word, we locate the defect by simply analyzing the effect induced by the defect itself. Thus, conversely to previous work on intra-cell diagnosis [11], there is no need to characterize the library to create a defect dictionary. The faulty behavior analysis is performed by applying the Critical Path Tracing (CPT) at transistor level. Compared to [10, 31] there is no need to pre-compute any fault dictionary and to convert the netlist.

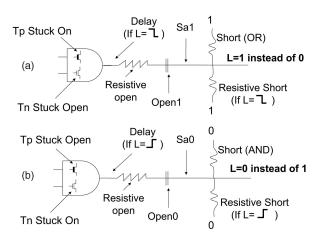

#### 2.1.4.1 From Defects To Fault Models

In this section, we present the main causes of physical defects and how these defects are usually modeled at transistor-level domain. Then, we discuss about the faulty behavior induced by defects and how the fault models represent them. This analysis is important in order to give the basics on how the proposed approach is defect independent while targeting transistor-level circuit descriptions. A physical defect can be caused by several phenomena such as metal line broken/deformed, contact or via broken/deformed. These phenomena will lead to either an unexpected connection between two or more nets (short) or a missing connection on one net (open). A net, at transistor-level domain, correspond to different elements: polysilicon (the transistor gate terminal), active (the transistor drain and source terminals), metal line (interconnections between transistors), contact (connection trough active and metal level 1) or via (connections trough metal levels). Usually, these defects are modeled at transistor-level domain as: (i) an unexpected connection between two nets associated to a specific resistance value (resistive-short), (ii) an unexpected resistance value on a given net (resistive-open). Depending on the considered resistance value, the effect induced by the defect can vary. Thus, the choice of meaningful resistance values is crucial to have an accurate model of physical defects. Existing works on intra-cell diagnosis rely on this way to model defects to create the defect dictionary.

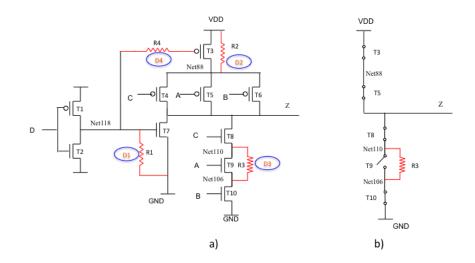

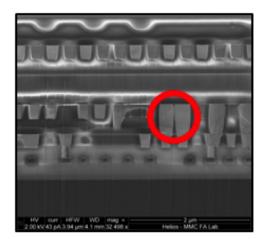

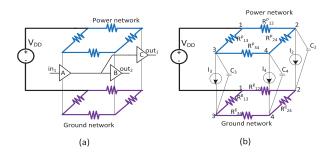

FIGURE 2.1: Physical defects modeling at transistor-level domain b) Equivalent circuit when the stimuli "0111" are applied.

Figure 2.1.a) shows an example of physical defects and the related model at transistorlevel domain for a complex gate composed of four primary inputs (A, B, C and D) and one primary output (Z). In the transistor-level netlist four defects are highlighted in red. Please note that the four defects are only an example, the proposed approach can target any possible defects.

Defect D1 models an unexpected connection between net118 and ground. The behavior of this defect depends on the resistance value R1. If R1 is lower than a threshold value RT, then the Vgs (voltage level between gate and source terminal of transistor T7) is always lower than Vth of T1. Thus T1 remains switched off (faulty behavior). If R1 is grater than RT, then Vgs depends on the voltage level of Net118 (correct behavior). From a logical point of view the first case (when R1 <RT) is equivalent to have Net118 stuck at logic value '0'. A similar consideration can be done for defect D2. Depending on R2 value, it impacts the voltage level of net88. From a logical point of view it is equivalent to have net88 stuck at logic value '1'.

Defect D3 models an unexpected connection between net110 and net106. The behavior of this defect depends on the resistance value R3 and also on the applied stimuli (i.e., it can activated or not). For example Figure 2.1.b) gives the circuit when the stimuli "0111" are applied to inputs ABCD respectively. Transistors T8 and T10 are switchedon while T9 is switched-off and output Z is set to logic '1'. However, due to the presence of this defect, the output is now connected to the ground through R3. Thus the defect is activated. Once the defect is activated we analyze the R3 value to determine its behavior. If R3 is lower than Rmin then, the output will be set to logic value '0'. In this case, from a logic point of view the Net106 force its logic value '0' to the Net110 and then the output is changed. On the other hand, if R3 is greater than Rmin but lower than Rmax (Rmin <R3 <Rmax) then, output Z will be affected by an undesired transition (from logic '1' to '0') due to the long discharge time. Finally, if R3 is grater than Rmax then output Z will take the correct logic value and the circuit behavior is faulty free. Note that the value of Rmin and Rmax depends on the circuit technology.

Finally, defect D4 affects the net Net118. For certain values of R4 the signal propagation trough gate of transistor T4 is delayed. To summarize, the analyzed faulty behavior induced by the four defects of Figure 2.1.a) are:

- D1, D2: the faulty behavior results in a net always set to a given logic value (either '1' or '0');

- D3: the faulty behavior results in a net set to a given logic value (in the example logic '0') depending on the input configuration or in a signal propagation delay affecting primary output Z;

- D4: the faulty behavior results in net where the signal propagation is affected by a given delay.

Even if we target the transistor-level domain, we exploit the knowledge of the analyzed faulty behavior to be defect independent. Thus, we can avoid to explicitly considering the resistance value. We will show in the next section that the proposed intra-cell approach identifies the possible locations of a defect. Usually faulty behaviors induce by defects are represented by means of fault models. From above the example we can list the exploited fault models:

- Stuck-at fault model [28]: the logic value of a given net appears to be stuck at a constant logic value ('0' or '1'), referred as stuck-at-0 or stuck-at-1 respectively (e.g., defects D1 and D2 in Figure 2.1).

- Dominant Bridging fault model [28]: this fault involves two nets called aggressor and victim. The logic value of the victim is set to the logic value of the aggressor (e.g., defect D3 in Figure 2.1).

- Delay fault model [28]: the transition from a given logic value V to the opposite logic value !V is delayed. Two types of delay faults are defined: slow-to-rise transition fault model (slow transition from logic '0' to logic '1') and slow-to-fall transition fault model (slow transition from logic '1' to logic '0').

Since the proposed diagnosis approach provides possible defect locations, for each of them we will associate one or more fault models according to the observed faulty behavior.

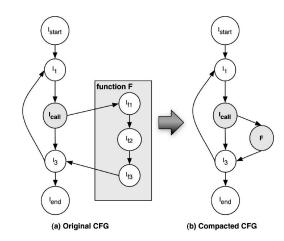

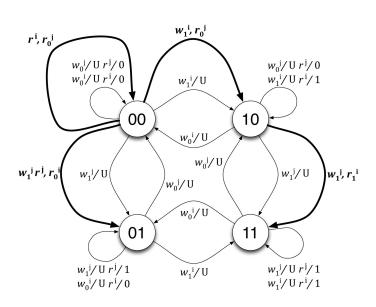

#### 2.1.4.2 Intra-Cell Diagnosis Flow

In this section, we present the whole intra-cell logic diagnosis approach. It is able to locate the root cause of observed failures inside a logic cell. Since the proposed approach works at transistor-level, it cannot be applied to the whole circuit due to its complexity (i.e., billions of transistors). However, it can be easily applied to a single target logic cell (i.e., up to fifty transistors) identified by a logic-level diagnosis tool.

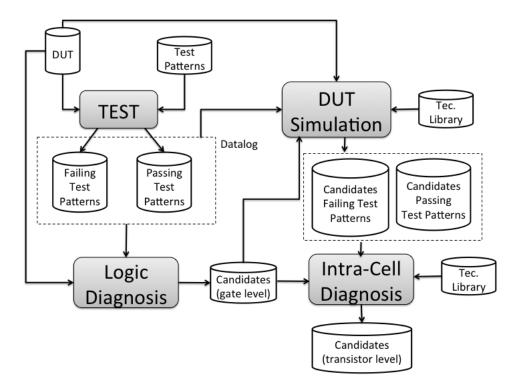

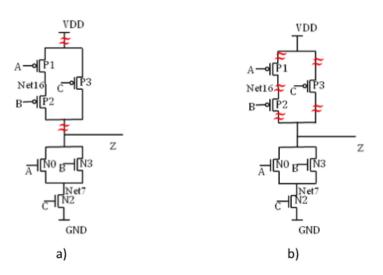

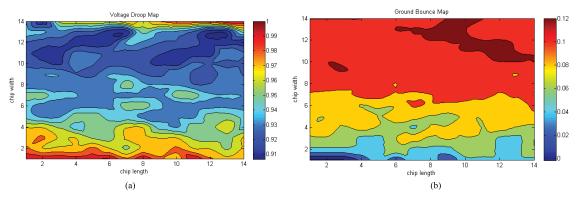

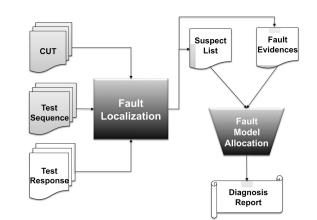

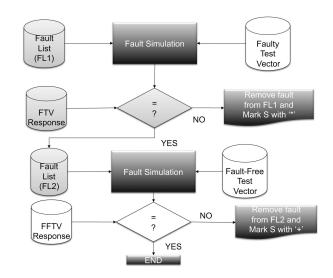

Figure 2.2 sketches the overall diagnosis flow. First of all, the **test** applies test patterns to the DUT (Device Under Test) to distinguish between the correct circuit behavior and the faulty circuit behavior caused by defects. These defects induce failing output responses for one or more input test patterns. Input test patterns leading to observed faulty behavior are called failing test patterns and stored in to a file called datalog. Input patterns for which no faulty behavior is observed are called passing test patterns. Then, the **inter-cell fault diagnosis** exploits datalog information to determine a list of suspected logic cells (i.e., candidates). Any available commercial diagnosis tool can

FIGURE 2.2: Overall diagnosis flow.

be adopted. For each suspected cell, we have to know logical values applied to it when failing and passing test patterns are applied to the DUT (i.e., DUT simulation). **DUT simulation** aims at determining the local set of failing/passing patterns for each suspected logic cell reported by inter-cell diagnosis. Finally, the **intra-cell diagnosis** is executed for each Suspected Gate (SG) and the pre-determined local failing/passing test patterns set (*lfp* and *lpp*). The intra-cell diagnosis result is a list of candidates at transistor level. For each suspected net a set of fault models able to explain observed failures is associated.

#### 2.1.4.3 DUT Simulation

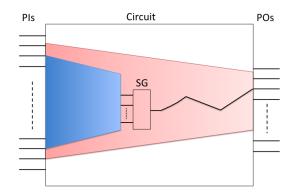

The intra-cell diagnosis is applied on a single candidate identified as the Suspected Gate (SG). The preliminary step of the proposed intra-cell diagnosis approach aims at determining the local failing/passing patterns defined as *lfp* and *lpp* respectively.

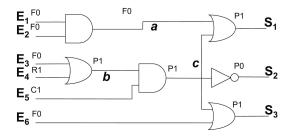

Figure 2.3 shows the SG located in the circuit. When a failing test pattern fp is applied to the circuit PIs, the fault affecting the SG is sensitized and its effect is then propagated to at least one circuit PO. This is guaranteed by the fact that during the test a failure is observed when the fp is applied to the circuit. Since the intra-cell diagnosis is applied to the SG only, we have to known the logical values of the SG inputs (called local patterns) when the fp is applied to circuit PIs. Thus, a logic simulation of the fp is required to get

FIGURE 2.3: Local Failing/Passing test patterns.

those values. This simulation has to be performed for each given failing test pattern. In a similar way, we have to know which are the logical values applied to the SG in the case of passing test patterns. A test pattern does not detect any fault for two reasons: (i) the fault is not sensitized (ii) the fault is sensitized but is effect is not observed because the fault effect cannot be propagated to reach the primary outputs. For the passing test pattern, we have to discriminate the reason why the fault located in the SG has not been detected (i.e., discriminate between (i) and (ii)). Thus, we have to verify if the fault effect can be propagated or not. If yes, then the pattern could be considered as a local passing test pattern because any failures should be observed during the test.

However, one more consideration must be done. In section 2.1.4.1 we described the faulty behavior considered in this work. Some of them depend only on the local gate input values (i.e., stuck-at and bridging faults). Some others depend not only on the local gate input values but also on the previous local values (i.e., delay faults). Taking in to account this consideration, we can now classify a given lpp as follows:

- If we assume that the defect affecting the suspected gate SG leads to a static faulty behavior (i.e., stuck-at, bridging) then, lpp is classified as local passing pattern;

- If we assume that the defect affecting the suspected gate SG leads to a dynamic faulty behavior (i.e., delay) then, lpp can not be classified as local passing test pattern, because we do not consider the previous pattern.

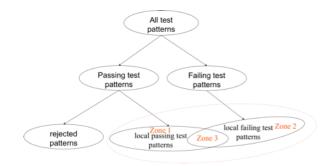

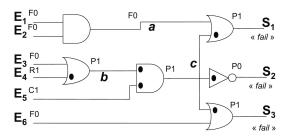

At this stage of the diagnosis flow, we must consider as valid both the above assumption. Therefore, we will store the lfp and lpp in to different data structure associated to the static faulty behavior and to the dynamic faulty behavior respectively. Finally, for the case of defects leading to a dynamic faulty behavior, a sequence of test patterns has to be applied to detect the defects. It may be possible that the same local pattern could be declared falling and passing. For this case, we knew that the defect affecting the circuit is a dynamic type so that only delay fault will be targeted thus discarding both stuck-at and bridging faults. The analysis performed to determine local failing and passing test patterns leads to the taxonomy shown in Figure 2.4.

FIGURE 2.4: failing and passing local test patterns taxonomy.

After the test, patterns can be classified into two categories: failing and passing test patterns.

- Definition 1: Failing test patterns are used to determine local failing test patterns.

Zone 2 in Figure 2.4 shows this type of test patterns.

- **Definition 2**: Passing test patterns are used to determine local passing test patterns. The passing test patterns illustrated in zone 1 of Figure 2.4.

- **Definition 3**: When at least one local test pattern is declared at the same time failing and passing  $(\text{lfp} \cap \text{lpp} \neq \emptyset)$  as shown in the zone 3 of Figure 2.4, it means that the defect affecting the circuit leads to a dynamic faulty behavior. In this case, we can discard the static faulty behavior (i.e., static and bridging) to be the root cause of observed failures.

- Definition 4: If lfp ∩ lpp = Ø, then defect affecting the circuit can lead either to a dynamic or static faulty behavior. In this case, we must consider both static and dynamic faulty behavior can be to be the root cause of observed failures.

In the next section we will describe in detail the applied intra-cell diagnosis approach and how the information extracted during DUT simulation are exploited.

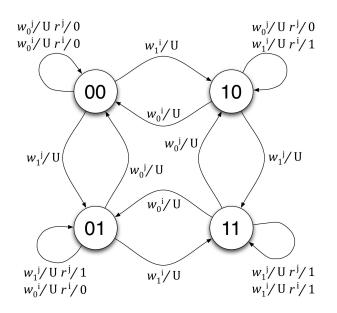

#### 2.1.4.4 Effect-Cause Intra-cell diagnosis algorithm

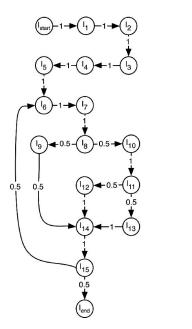

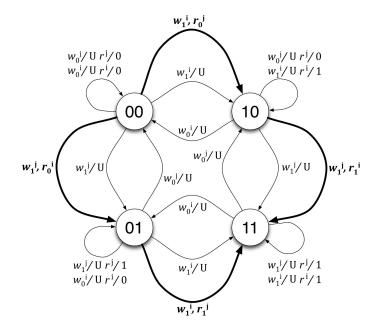

In this section we present the proposed intra-cell diagnosis approach. It is based on the "Effect-Cause" paradigm and it exploits the Critical Path Tracing (CPT) algorithm here applied at transistor level. The proposed intra-cell diagnosis approach requires two main inputs: the SG description at transistor level and the local set of failing/passing test patterns. Figure 2.5 gives the pseudo code of the intra-cell diagnosis procedure.

```

INTRA-CELL DIAGNOSIS(SG, lfp, lpp)

```

| 1              | GSL = GDSL = all $SG$ nets and transistor terminals |

|----------------|-----------------------------------------------------|

| 2              | GBSL = all SG couple of nets                        |

| 3              | for each $lfp$                                      |

| 4              | do                                                  |

| 5              | Fault-free-simulation $(SG, lfp)$                   |

| 6              | CPT(SG, lfp, CSL, BSL, DSL)                         |

| $\overline{7}$ | $GSL = GSL \cap CSL$                                |

| 8              | $GBSL = GBSL \cap CBSL$                             |

| 9              | $GDSL = GDSL \cap CDSL$                             |

| 10             |                                                     |

| 11             | for each $lpp$                                      |

| 12             | do                                                  |

| 13             | Fault-free-simulation $(SG, lpp)$                   |

| 14             | CPT(SG, lpp, CVL, CBVL)                             |

| 15             | GSL = GSL - CVL                                     |

| 16             | GBSL = GBSL - CVSL                                  |

| 17             |                                                     |

| 18             | FAULT-ALLOCATION $(GSL, GBSL, GDSL)$                |

|                |                                                     |

FIGURE 2.5: Intra-cell diagnosis pseudo code.

The procedure is divided in two blocks identified by the two "for loop" statements. The first one targets the lfp. For each lfp, a fault-free simulation is performed by using a switch-level simulation. In the switch-level simulation, the transistors (i.e., nMOS and pMOS) behave as on-off switches.

Since the simulated netlist is composed of few transistors the required simulation time is negligible. The fault-free simulation is mandatory to determine the logic value of each net. Then, Critical Patch Tracing (CPT) is executed starting from the SG output. It traces back internal nets to reach the SG inputs. Each traced net is set as critical. A net is critical if the inversion of its logical value causes the inversion of the output value. Each critical net is marked as a suspect. A suspect can be the root cause of observed errors or simply a net that propagate the fault effect. Each suspect is stored in a list with its logic value. The logic value is kept in the list because it will be used during the fault model allocation. The result of the CPT is the Suspect List (SL). The SL is defined as follows:

$$SL = \{ (net_0, LV_0), (net_1, LV_1), \dots, (net_n - 1, LV_n - 1) \}$$

$$(2.1)$$

where:

- net<sub>i</sub>: is the critical net (transistor-level interconnection nets and transistor terminals).

- $LV_i = \{0, 1, U\}$ : is the logic value of the critical net. U is the unknown value.

As stated before, a given suspect can simply propagate the fault effect (i.e., it is not the root cause of observed errors). This case can happen for two reasons:

- 1. The suspect net belongs to the propagation path of the actual faulty net. In this case, the suspect is logically equivalent to the actual faulty net.

- 2. The suspect net is indeed the victim of a bridging fault. In this case, another net (i.e. the aggressor) "forces" a faulty value on the victim.

The second case is more complex than the first one from the diagnosis point of view. Here, we have to verify if a bridging fault is possible. For this reason, after the CPT a second list of suspects is created. The so-called Bridging Suspect List (BSL) contains all the possible couples "Victim/Aggressor" that can be involved in a bridging fault. The victim belongs to the actual SL, while the aggressor can be any net having an inverted logic value w.r.t. the logic value of the victim. The BSL is defined as follows:

$$BSL = \{ (V_0/A_0), (V_1/A_1), \dots, (V_m - 1/A_m - 1) \}$$

$$(2.2)$$

where:

- $V_i \in SL$ : is the victim.

- $A_i = (Net_j, LV_j)$ : is the aggressor. It can be any net of the gate having a logic value opposite to the logic value of the victim. Thus  $LV_j = !LV_i$ .

So far (equations 2.1 and 2.2), we defined as critical nets for which the inversion of their logical value causes the inversion of the output. With these two lists, we are able to identify any static faults (see Section 2.1.4.1). To complete our analysis, we have also to consider the case of dynamic faults affecting the analyzed gate and thus the circuit (see Section 2.1.4.1). As for the equation 2.1 we look for critical nets, where a critical net can be either a transistor terminal or an interconnection net. We define those nets as critical delay nets. Critical delay nets are added in a list called Delay Suspect List (DSL) defined as follows:

$$DSL = (Net_0, Net_1, ... Net_n - 1)$$

(2.3)

where:

• *Net<sub>i</sub>* is the critical net (transistor-level interconnection nets and transistor terminals).

Please note that in this case, the logical value of a critical delay net is not stored in the list because it is not used during the fault model allocation. Basically we do not distinguish between a slow-to-rise/slow-to-fall delay fault. The three lists are stored in a so-called **Current Suspect List** (CSL), the **Current Bridging Suspect List** (CBSL) and the **Current Delay Suspect List** (CDSL). The assumption of this work is the presence of only one defect on a given circuit. Thus, the root cause of observed errors has to be present in all lists provided by the CPT application. For this reason, we update the global suspect lists by performing an intersection (line 7, 8 and 9 in Figure 2.5). The intersection between two suspects lists  $SL_a$  and  $SL_b$  is defined as follows:

$$SN = (net_i, LV_i) \in SL_a \cap SL_b if(SN \in SL_a) and(S_N \in SL_b)$$

$$(2.4)$$

This definition removes a net from the suspect list if the net is traced with different logic values (e.g., once with '0' and another with '1'). This is coherent with the stuck-at fault model. If a net is affected by a stuck-at fault, its value must be always the same during the failing test patterns application. Otherwise, the net cannot be affected by a stuck-at fault. Thus it is removed from the suspect list.

The intersection between two bridging suspect lists elements  $BSLE_a$  and  $BSLE_b$  is defined as follows:

$$BSLE_a \cap BSLE_b = (net_i, LV_i \cap LV_m) / (net_j, LV_j \cap LV_n) if (net_i = net_m) and (net_j = net_n)$$

(2.5)

The intersection between logic values is defined in the Figure 2.6

The above leads to keep a couple Victim/Aggressor (V/A) even if it appears in two lists with different logic values. Conversely to the case of a stuck-at fault, this case can occur if a strong dominant bridging fault is the root cause of observed failures.

The intersection between two delay suspects lists is similar to the one for SL (suspects lists). The difference is that there is no logic value associated to the delay candidates. The intersection between two delay suspects  $DSL_a$  and  $DSL_b$  is defined as follows:

|   | 0  | 1  |

|---|----|----|

| 0 | 0  | 01 |

| 1 | 01 | 1  |

FIGURE 2.6: Logic values intersection.

$$DSN = (net_i) \in DSL_a \cap DSL_b if(DSN \in DSL_a) and(DSN \in DSL_b)$$

(2.6)

The DSN is kept if and only if it belongs to all DSLs. Please note that the logic value is not stored in the DSL (equation 2.6), thus, we don't need to consider the logic value of candidates during the DSLs intersection.

The result of the intersection is stored in the so-called **Global Suspect List**) (GSL), the **Global Bridging Suspect List** (GBSL) and the **Global Delay Suspect List** (GDSL).

The second block of the intra-cell diagnosis procedure aims at applying the CPT for each lpp to vindicate the suspected elements. The main concept behind this block has been already exploited for the inter-cell diagnosis. This step is applied for the GSL and GBSL list but not for the GDSL. This is because we can determine local passing pattern only for the case of static fault, thus we can vindicate only for GSL and GBSL. As for the first block, we create two suspect lists. The first one contains critical nets called Vindicate List (VL). In this case each critical net is vindicated to be the root cause of the observed failure. The second list contains all possible couple V/A that can be vindicated to be involved in a bridging fault called Bridging Vindicate List (BVL). The victim belongs to the actual VL, while the aggressor can be any net having an opposite logic value w.r.t. to the logic value of the victim.

We compute the difference between the vindicate lists and the suspect lists (lines 15 and 16 of Figure 2.5). Owing to the knowledge of the actual passing test patterns it is possible to narrow down the actual list of suspects.

The difference between a suspect list SL and a vindicate list VL is defined as follows:

$$SN = (net_i, LV_i) \in (SL - VL)if(SN \in SL)and(SN \ni VL)$$

$$(2.7)$$

In the same way the difference between a bridging suspect list BSL and a bridging vindicate list BVL is defined as follows:

$$SBN = (net_i, LV_i)/(net_j n LV_j) \in (BSL - BVL)if(SN \in SL)and(SN \ni VL)$$

(2.8)

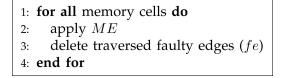

Finally, the last step of the intra-cell diagnosis is the fault model allocation. Basically for each suspect we exploit the stored logic value to associate a fault model. Once again, three types of fault models are considered: (i) the stuck-at fault, (ii) the dominant bridging fault and (iii) the delay fault. During the fault model allocation, it could be happen that one or several suspected lists are empty. This means that the root cause of observed errors cannot be the fault model corresponding to the empty suspected list. For example, when  $lfp \cap lpp \neq$  only dynamic faults are possible. So that, after suspected lists construction for lfp and lpp, GSL and GBSL will be empty and we consider only faults in the GDSL.

#### 2.1.4.5 Experimental Results

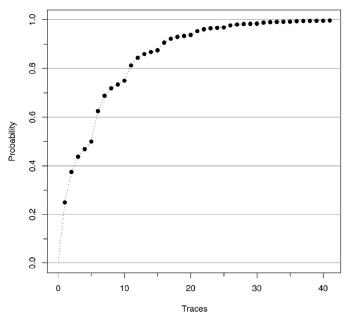

The proposed intra-cell diagnosis procedure has been implemented in C++. It has been validated by means of simulations and actual silicon data. The simulation-based validation exploits a defect injection campaign. Physical defects can take forms of missing or extra materials and they are often modeled by open- and short-circuits as presented in. Defects are thus injected into the transistor-level netlist of a given gate of a DUT. Then, by using a spice simulator, the faulty gate is simulated in order to determine its truth table. The truth table is then used as library model, so that the whole faulty circuit is simulated at gate level to emulate the test phase. Observed failures are stored in the failure file (i.e., datalog). Injected defects lead to stuck-at, bridging and delay faults. The silicon-based validation has been carried out on STM circuits declared faulty during the production test.

#### $Simulation\mbox{-}based\ validation$

We used two circuits named A and B to perform the simulation-based validation. The circuits correspond to actual STM products and have been synthesized with a STM 90nm technology. Table 2.1 shows the characteristics of the circuits in terms of gates, FFs and scan chains.

For each logic cell in the targeted technology library, we randomly injected one defect at time and we perform spice simulation to characterize the behavior of the faulty logic

| Circuit | #Gate       | #FlipFlop  | #ScanChain |

|---------|-------------|------------|------------|

| A       | 258         | 30         | 1          |

| В       | $69,\!8804$ | $56,\!373$ | 25         |

TABLE 2.1: Circuit Characteristics.

cell. Injected defects lead to have 3 types of faulty behaviors. The 30% of them lead to stuck-at faults, the 30% lead to bridging faults and the remaining 40% lead to delay faults.

Then, we randomly select one gate in the target circuit and we replace it by the faulty gate. We perform the simulation and we store observed failures, if any, in the datalog. For each datalog we then run a commercial logic diagnosis tool to identify our suspected gate.

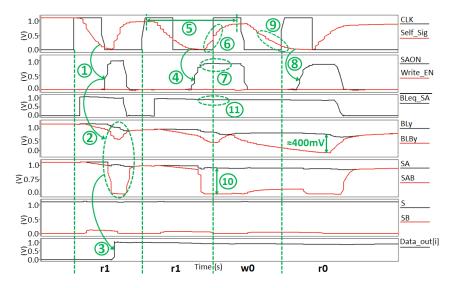

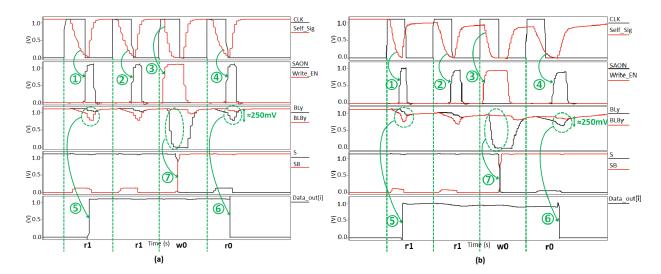

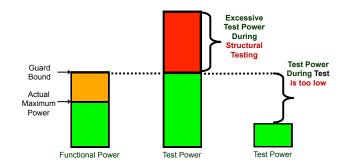

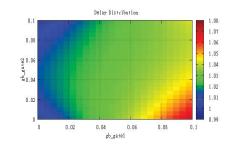

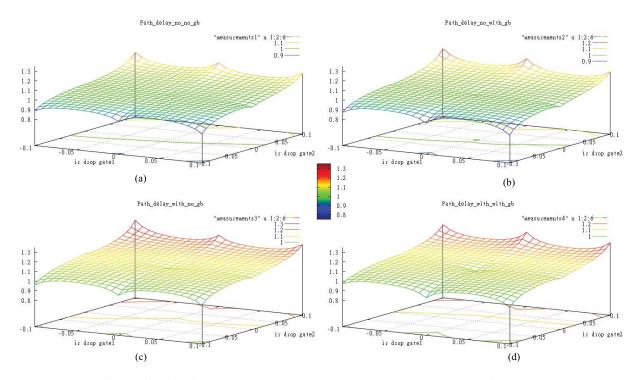

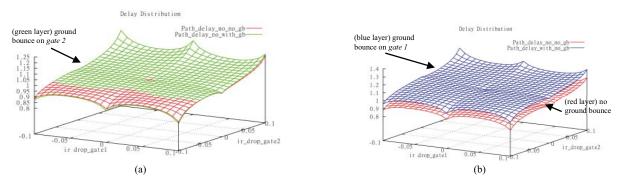

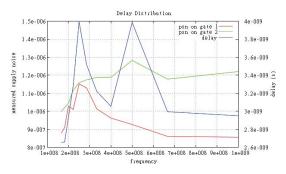

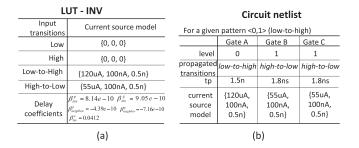

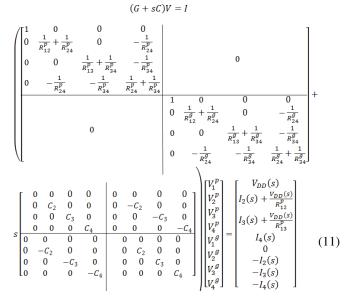

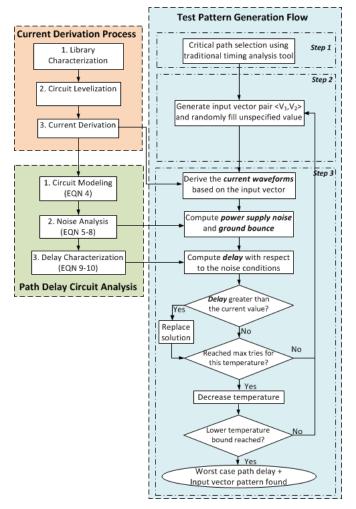

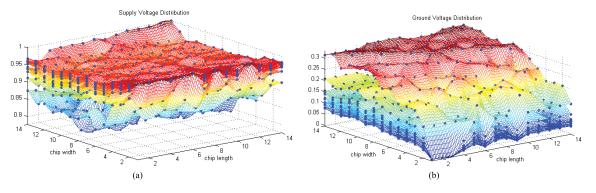

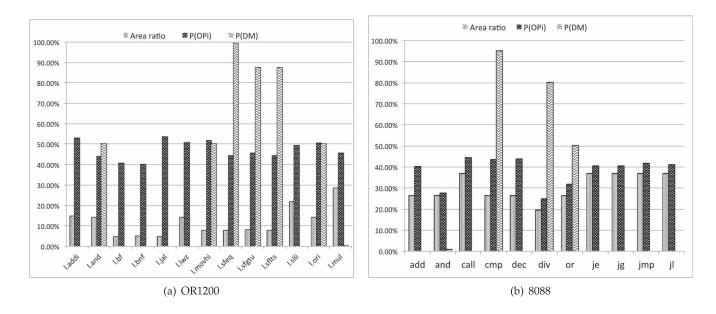

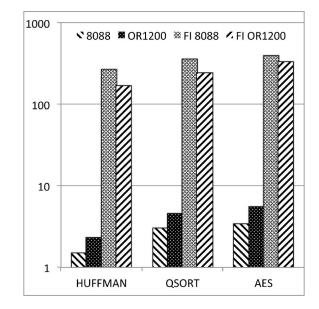

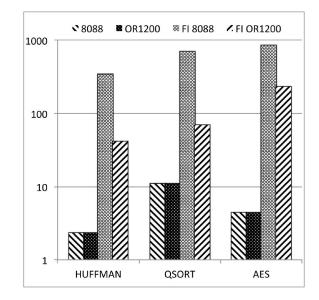

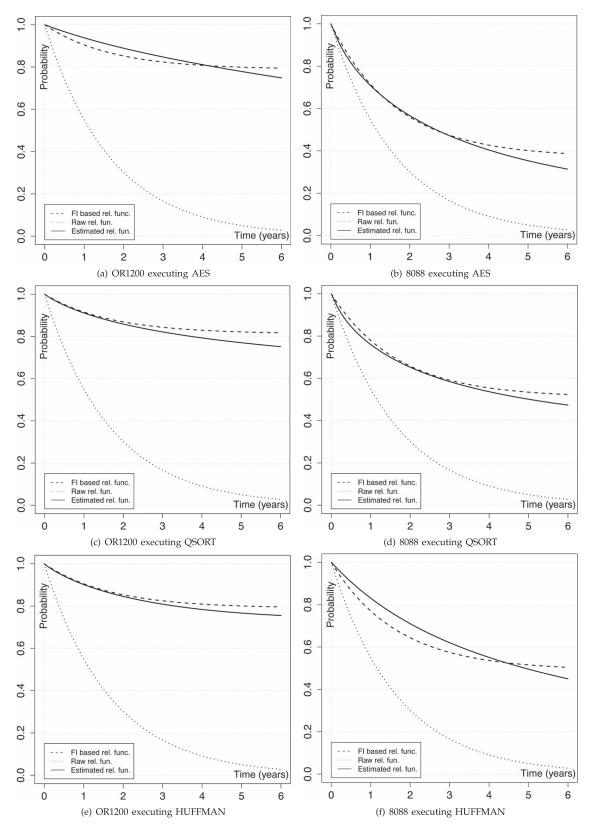

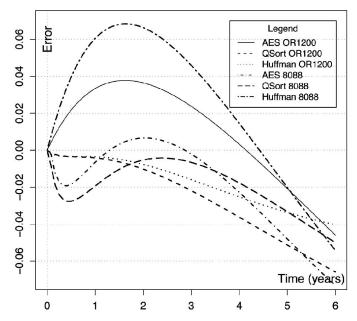

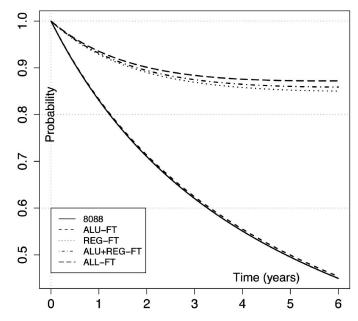

The test patterns applied for the experiments have been generated exploiting a commercial ATPG tool. The test sets target transition fault models and the test length is 25 and 500 patterns for circuit A and B respectively. After the DUT simulation step, we got in average 3 local failing patterns and 6 local passing patterns.