# Fast Cycle-approximate Simulation Techniques for Manycore Architecture Exploration

Anastasiia Butko

#### ▶ To cite this version:

Anastasiia Butko. Fast Cycle-approximate Simulation Techniques for Manycore Architecture Exploration. Optics / Photonic. Université Montpellier, 2015. English. NNT: 2015MONTS144. tel-01959029v2

#### HAL Id: tel-01959029 https://hal-lirmm.ccsd.cnrs.fr/tel-01959029v2

Submitted on 25 Jun 2019

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE Pour obtenir le grade de Docteur

Délivré par Université Montpellier

Préparée au sein de l'école doctorale **Information**, **Structures**, **Systèmes** (I2S)

Et de l'unité de recherche Laboratoire d'Informatique, de Robotique et de Microélectronique de Montpellier (LIRMM)

Spécialité : Microélectronique

Présentée par BUTKO Anastasiia

# Fast Cycle-approximate Simulation Techniques for Manycore Architecture Exploration

Soutenue le 11 decembre 2015 devant le jury composé de

M. Leandro SOARES INDRUSIAK, Senior Lecturer, Rapporteur University of York, UK M. Jean-François MEHAUT, Professeur, Laboratoire Rapporteur d'Informatique de Grenoble, FRANCE M. Chris ADENIYI-JONES, Principal Engineer, Examinateur ARM Ltd., Cambridge, UK M. Michel ROBERT, Professeur, Université de Président du jury Montpellier, FRANCE M. Gilles SASSATELLI, Directeur de Recherche au Directeur de Thèse CNRS, LIRMM/Université de Montpellier, FRANCE M. Abdoulaye GAMATIE, Directeur de Recherche au Co-encadrant CNRS, LIRMM/Université de Montpellier, FRANCE Co-encadrant M. Luciano OST, Lecturer, University of Leicester, UK

"Праця людини – окраса і слава, праця людини – безсмертя її. " <sup>1</sup> Симоненко Василь Андрійович

<sup>&</sup>lt;sup>1</sup> "Human labor - glory and fame, human labor - immortality." Vasyl Symonenko.

#### Abstract

Since the computational needs precipitously grow each year, HPC technology becomes a driving force for numerous scientific and consumer areas. The most powerful supercomputer has been progressing from TFLOPS to PFLOPS throughout the last ten years. However, the extremely high power consumption and therefore the high cost pushed researchers to explore more energy-efficient technologies, such as the use of low-power embedded SoCs.

The evolution of emerging manycore systems, forecasted to feature hundreds of cores by the end of the decade calls for efficient solutions for the design space exploration and debugging. Available industrial and academic simulators differ in terms of simulation speed/accuracy trade-offs. Cycle-approximate simulators are popular and attractive for architectural exploration. Even though enabling flexible and detailed architecture evaluation, cycle-approximate simulators entail slow simulation speeds, thereby limiting their scope of applicability for systems with hundreds of cores. This calls for alternative approaches capable of providing high simulation speed while preserving accuracy that is crucial to architectural exploration.

In this thesis, we evaluate cycle-approximate simulation techniques for fast and accurate exploration of multi- and manycore architectures. Expecting to significantly reduce simulation time still preserving the accuracy at the cycle-approximate level, we propose a hybrid trace-oriented approach to enable flexible manycore architecture simulation. We design a set of simulation techniques to overcome the main weaknesses of the trace-oriented approach. The trace synchronization technique aims to manage control and data dependencies arising from the abstraction of processor cores. The trace replication technique is proposed to simulate manycore architectures using a finite set of pre-collected traces. The computation phase scaling technique is designed to enable flexible switching between multiple processor models without considering microarchitectural difference but taking into account the computation speed ratio.

Based on the proposed simulation environment, we explore several manycore architectures in terms of performance and energy-efficiency trade-offs.

**Keywords:** High-performance computing, energy-efficiency, manycore, heterogeneous, big.LITTLE, modeling, gem5, trace-driven.

#### Résumé

Le calcul intensif joue un rôle moteur de premier plan pour de nombreux domaines scientifiques. La croissance en puissance crête des supercalculateurs a évolué du téraflops au pétaflops en l'espace d'une décennie. Toutefois, la consommation d'énergie associée extrêmement élevée ainsi le coût associé ont motivé des recherches vers des technologies plus efficaces énergétiquement comme l'utilisation de processeurs issus du domaine des systèmes embarqués à faible puissance. Selon les prévisions, les systèmes multicoeurs émergents seront constitués de centaines de coeurs d'ici la fin de la décennie. Cette évolution nécessite des solutions efficaces pour l'exploration de l'espace de conception et le débogage. Les simulateurs industriels et académiques disponibles à ce jour diffèrent en termes de compromis entre vitesse de simulation et précision. Les simulateurs quasi cycle-précis sont populaires et attrayants pour l'exploration architecturale. En outre, bien que permettant une évaluation flexible et détaillée de l'architecture, les simulateurs quasi cycle-précis entraînent des vitesses de simulation lentes ce qui limite leur champ d'application pour des systèmes avec des centaines de cœurs. Cela exige des approches alternatives capables de fournir des simulations rapides tout en préservant une précision élevée ce qui est cruciale pour l'exploration architecturale.

Dans cette thèse, des modèles d'architectures multicœurs complexes ont été développés et évalués en utilisant des systèmes de simulation quasi cycle-précis pour l'exploration de la performance et de la puissance. Sur cette base, une approche hybride orientée traces d'exécution a été proposée pour permettre une exploration rapide, flexible et précise des architectures multicoeurs à grande échelle. Sur la base de l'environnement de simulation proposé, plusieurs configurations de systèmes manycoeurs ont été construites et estimées en évaluant le passage à l'échelle des performances. Enfin, des configurations alternatives d'architectures multicoeurs hétérogènes ont été proposées et ont montré des améliorations significatives en termes d'efficacité énergétique.

Mots-clés: calcul à haute performance, efficacité énergétique, multicoeurs, hétérogène, big.LITTLE, modélisation, gem5, simulation orientée trace.

# Acknowledgements

I would like to express my special appreciation and thanks to my advisor Gilles Sassatelli, co-advisors Abdoulaye Gamatié and Luciano Ost. I would like to thank you for encouraging my research and for allowing me to grow as a research scientist. Your advices on both research as well as on my career have been priceless. I would also like to thank my committee members, Leandro Soares Indrusiak, Jean-François Méhaut, Chris Adeniyi-Jones and Michel Robert for serving as my committee members even at hardship. I also want to thank you for letting my defense be an enjoyable moment, and for your brilliant comments and suggestions.

I also want to thank the funding body that supported this work. The research leading to this thesis has received funding from the European Community Seventh Framework Programme (FP7/2007-2016) under the Mont-Blanc 1 and Mont-Blanc 2 Projects: http://www.montblanc-project.eu, grant agreement no 288777 and no 610402.

I also want to thank my colleagues, in particular the brazilian community, for their heartful support, friendship and unforgettable moments at work (and out of work).

A special thanks to my family. Words cannot express how grateful I am to my mother, my father and my sister for all of the sacrifices that you've made on my behalf. I would also like to thank all of my friends, especially Iuliia Tkachenko, Vasiliy Muravyev, Irina Gavrilovich, Andrey Khorev, who supported me in writing, and incented me to strive towards my goal.

At the end I would like express appreciation to my beloved husband Artem who spent sleepless nights with and was always my support in the moments when there was no one to answer my queries.

# Contents

| $\mathbf{A}$  | bstra                     | ct                                                                                                                  | ii               |

|---------------|---------------------------|---------------------------------------------------------------------------------------------------------------------|------------------|

| R             | ésum                      | é                                                                                                                   | iii              |

| A             | ckno                      | m wledgements                                                                                                       | iv               |

| C             | onter                     | nts                                                                                                                 | iv               |

| $\mathbf{Li}$ | st of                     | Figures                                                                                                             | viii             |

| $\mathbf{Li}$ | st of                     | Tables                                                                                                              | Х                |

| $\mathbf{A}$  | bbre <sup>,</sup>         | viations                                                                                                            | xi               |

| 1             | Intr<br>1.1<br>1.2<br>1.3 | Context and Motivation                                                                                              | 1<br>1<br>5<br>7 |

| 2             | Sta                       | te-of-the-art                                                                                                       | 8                |

|               | 2.1<br>2.2<br>2.3<br>2.4  | Computer architecture simulation                                                                                    | 14               |

| 3             | Eva                       | luation of multicore architecture models in cycle-approximate sim-                                                  |                  |

|               | ulat                      | ion frameworks                                                                                                      | <b>2</b> 3       |

|               | 3.1                       | Introduction                                                                                                        | 23               |

|               | 3.2                       | Background                                                                                                          | 24               |

|               | 3.3                       | Methodology                                                                                                         | 27<br>27<br>29   |

|               | 3.4                       | Accuracy assessments of gem5 and McPAT versus real platforms 3.4.1 Performance modeling: Dual-core SMP architecture | 30<br>30<br>30   |

*Contents* vi

|   |     |         | 3.4.1.2 Accuracy assessments                               | . 33  |

|---|-----|---------|------------------------------------------------------------|-------|

|   |     | 3.4.2   | Performance modeling: Heterogeneous multicore architecture | . 37  |

|   |     |         | 3.4.2.1 Experimental setup                                 | . 39  |

|   |     |         | 3.4.2.2 Accuracy assessments                               | . 43  |

|   |     | 3.4.3   | Power modeling: Heterogeneous multicore architecture       |       |

|   |     |         | 3.4.3.1 Experimental setup                                 |       |

|   |     |         | 3.4.3.2 Accuracy assessments                               |       |

|   | 3.5 | Discus  | ssion                                                      |       |

| 4 | Hvl | orid tr | race-oriented approach for fast and accurate simulation (  | of    |

| _ | -   |         | architectures                                              | 54    |

|   | 4.1 | Introd  | luction                                                    | . 54  |

|   | 4.2 | Backg   | round                                                      | . 56  |

|   |     | 4.2.1   | Abstraction levels of computer architecture exploration    |       |

|   |     | 4.2.2   | From in-order to out-of-order processor                    |       |

|   |     | 4.2.3   | From single-core to multicores processors                  |       |

|   | 4.3 | Metho   | odology                                                    |       |

|   |     | 4.3.1   | From collection to simulation                              |       |

|   |     |         | 4.3.1.1 Synchronization traces                             |       |

|   |     |         | 4.3.1.2 Trace replication                                  |       |

|   |     |         | 4.3.1.3 Computation phase scaling                          |       |

|   |     | 4.3.2   | Case studies                                               |       |

|   |     | 4.3.3   | Evaluation metrics                                         |       |

|   | 4.4 |         | driven implementation in gem5                              |       |

|   | 1.1 | 4.4.1   | Trace collection and reduction                             |       |

|   |     | 4.4.2   | Trace simulation                                           |       |

|   | 4.5 |         | ation                                                      |       |

|   | 1.0 | 4.5.1   | Experimental setup                                         |       |

|   |     | 4.5.2   | Simulation accuracy                                        |       |

|   |     | 4.5.3   | Simulation speedup                                         |       |

|   |     | 4.5.4   | Simulation cost                                            |       |

|   | 4.6 |         | cation to compute accelerators exploration                 |       |

|   | 4.7 |         | ssion                                                      |       |

| J | a.  | 1 TG    |                                                            |       |

| 5 | •   | _       | A heterogeneous architecture exploration                   | 91    |

|   | 5.1 |         | luction                                                    |       |

|   | 5.2 | _       | ground                                                     |       |

|   |     | 5.2.1   | Single-ISA Heterogeneous multicore architecture            |       |

|   |     | 5.2.2   | OpenMP programming model                                   |       |

|   |     | 5.2.3   | ARM big.LITTLE technology                                  |       |

|   |     |         | 5.2.3.1 Hardware support                                   |       |

|   |     |         | 5.2.3.2 Software support                                   |       |

|   | 5.3 |         | ation of the Exynos 5 Octa SoC                             |       |

|   |     | 5.3.1   | Experimental setup                                         |       |

|   |     | 5.3.2   | Performance analysis                                       |       |

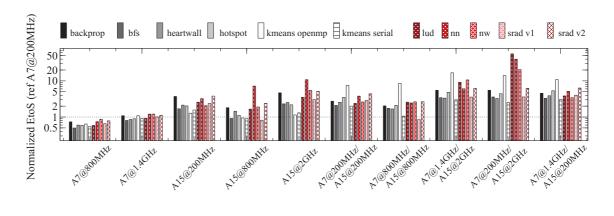

|   |     | 5.3.3   | Energy-to-solution analysis                                |       |

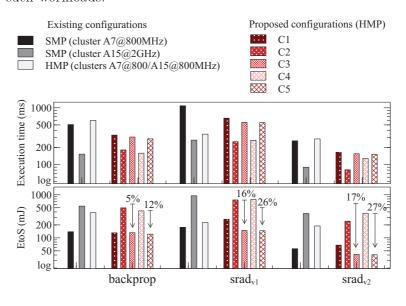

|   | 5.4 | Altern  | native big.LITTLE architectures exploration                | . 102 |

*Contents* vii

|    |       | 5.4.1 Experimental setup                                    | 102 |

|----|-------|-------------------------------------------------------------|-----|

|    |       | 5.4.2 Exploration results                                   |     |

|    | 5.5   | big.LITTLE architecture scaling via trace-driven simulation |     |

|    |       | 5.5.1 Experimental setup                                    | 105 |

|    |       | 5.5.2 Exploration results                                   |     |

|    | 5.6   | Single-ISA heterogeneous multicore granularity evaluation   | 108 |

|    |       | 5.6.1 Cycle-approximate model                               |     |

|    | 5.7   | Discussion                                                  | 116 |

| 6  | Con   | nclusions                                                   | 117 |

|    | 6.1   | Contributions                                               | 118 |

|    | 6.2   | Future work                                                 | 121 |

|    | 6.3   | Publications                                                | 123 |

|    |       |                                                             |     |

| A  | Per   | formance accuracy evaluation results                        | 125 |

| В  | Pow   | ver accuracy evaluation results                             | 127 |

|    |       |                                                             |     |

| Bi | bliog | graphy                                                      | 129 |

# List of Figures

| 1.1<br>1.2           | Performance development in the TOP500 list                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2                                                                                |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 2.1<br>2.2           | Model confidence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 15<br>16                                                                         |

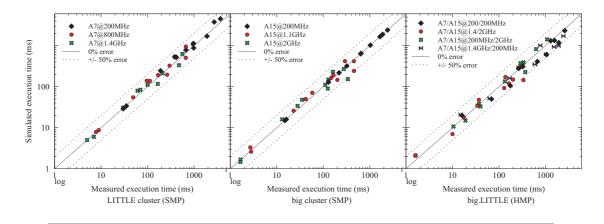

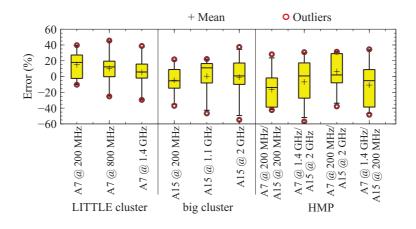

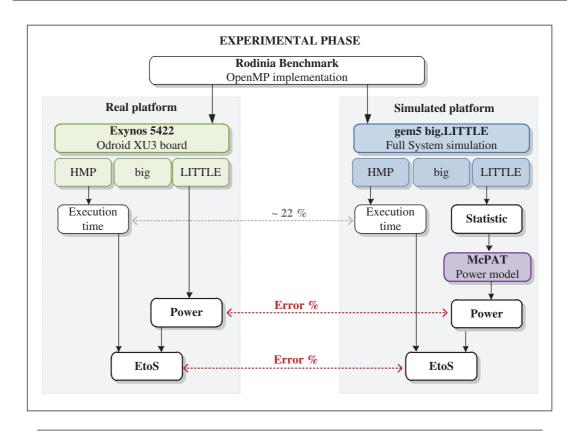

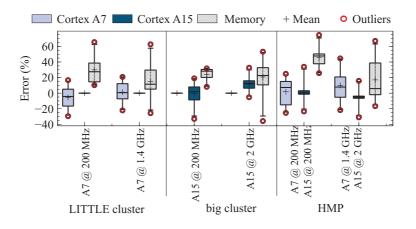

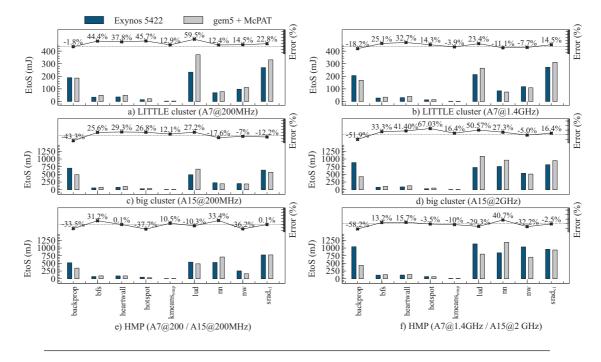

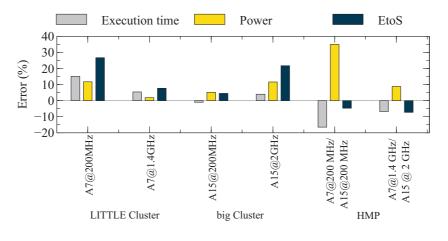

| 3.11<br>3.12<br>3.13 | Validation and accuracy assessments flow Accuracy assessments flow for ARM Dual-core architecture ARM Cortex-A9 Dual-core block diagram Benchmarks execution time comparison Analysis of the LU factorization execution Analysis of the Radix sort kernel execution Accuracy assessments flow for ARM big.LITTLE architecture ARM big.LITTLE architecture Execution time comparison for LITTLE Cortex-A7 cluster Execution time comparison for big.LITTLE performance model Execution time error distribution of simulated Rodinia benchmark Accuracy assessments flow for ARM big.LITTLE power model Power consumption error percentage summary Energy-to-solution comparison for ARM big.LITTLE architecture model | 288<br>311<br>344<br>355<br>366<br>399<br>400<br>444<br>466<br>486<br>500<br>500 |

|                      | Error percentage summary for performance, power and energy-to-solution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 51                                                                               |

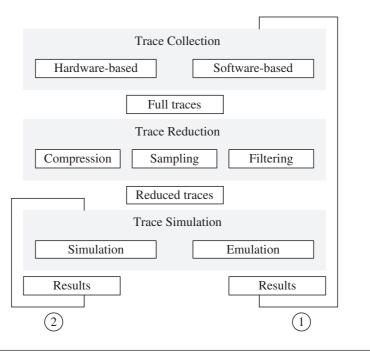

| 4.1<br>4.2<br>4.3    | Trace-driven exploration flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 57<br>58<br>60                                                                   |

| 4.4<br>4.5<br>4.6    | Memory organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 61<br>64<br>65                                                                   |

| 4.7<br>4.8<br>4.9    | Distributed memory programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 66<br>67<br>67                                                                   |

| 4.11                 | Trace-driven simulation case studies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 68<br>69<br>71                                                                   |

| 4.13<br>4.14         | An example of collected trace file extract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 73<br>74<br>75                                                                   |

| 4 1 (1)              | LIACE ALDILEI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 121                                                                              |

List of Figures ix

| 4.16 | Trace injector block diagram                                                         | 75  |

|------|--------------------------------------------------------------------------------------|-----|

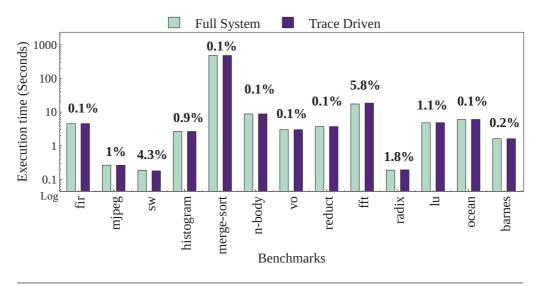

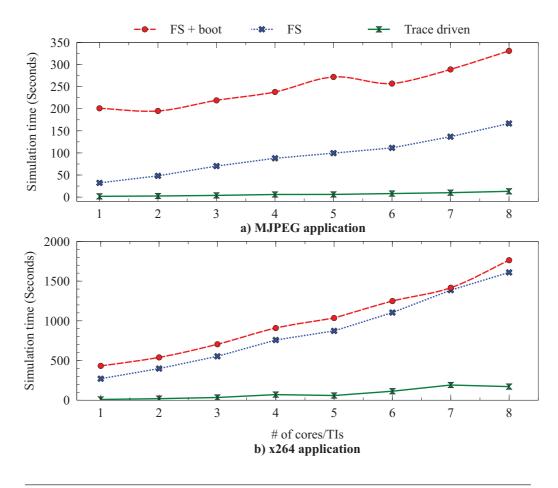

| 4.17 | Execution time comparison between full system and trace-driven modes .               | 79  |

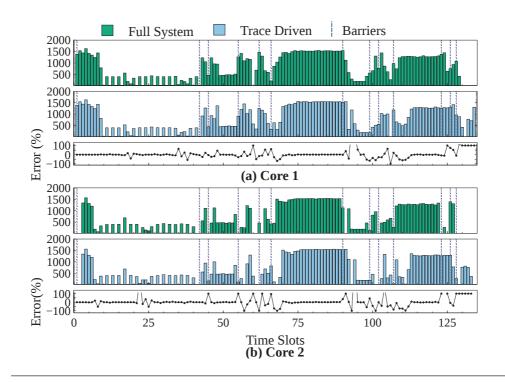

| 4.18 | Cache miss pattern comparison between full system and trace-driven ex-               | 0.0 |

| 4.10 | ecution for Radix kernel                                                             | 80  |

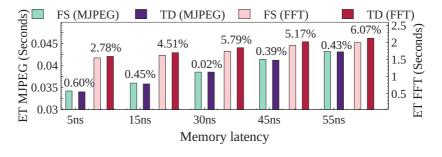

|      | Execution time comparison by varying the internal architectural parameters           |     |

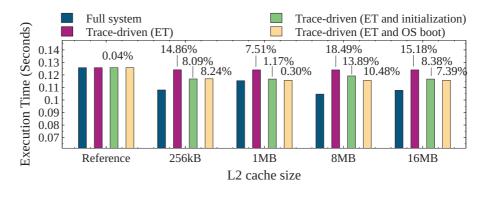

|      | Execution time comparison by including L2 cache memory                               | 81  |

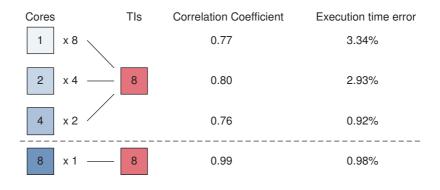

| 4.21 | Replication technique: correlation coefficient and execution time error analysis     | 82  |

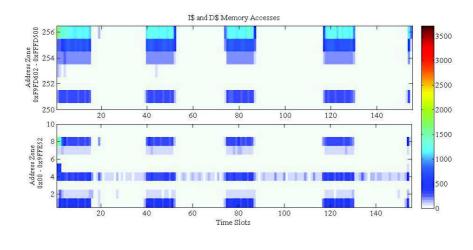

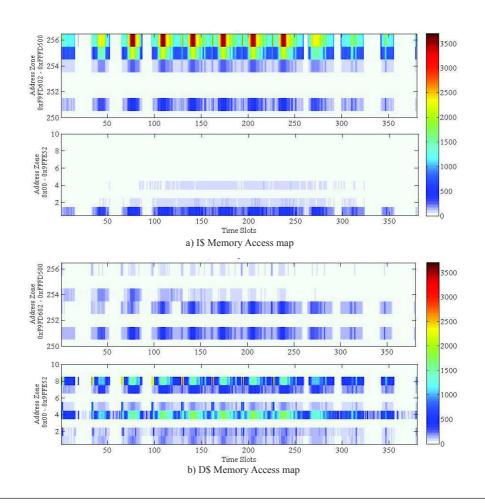

| 4 22 | Replication technique: address map of MJPEG 1 core 1 thread                          | 83  |

|      | Replication technique: address map of MJPEG 8 cores replication                      | 84  |

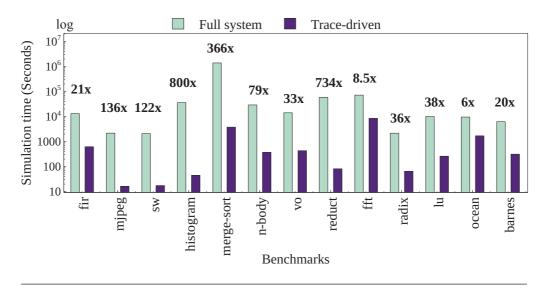

|      | Simulation time comparison between full system and trace-driven modes .              | 84  |

|      | Simulation time comparison between full system and trace-driven                      | 01  |

| 1.20 | modes                                                                                | 85  |

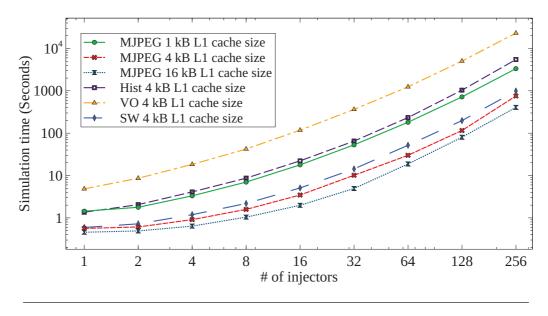

| 4.26 | Simulation time scaling up to 256 trace injectors system                             | 86  |

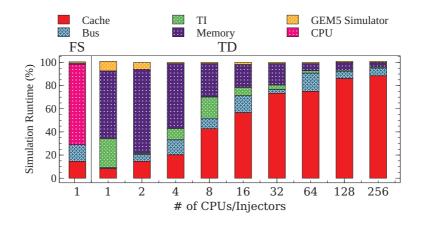

|      | Simulation time distribution for trace-driven simulation                             | 87  |

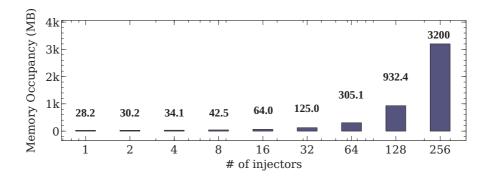

|      | Memory consumption variation for trace-driven simulation                             | 87  |

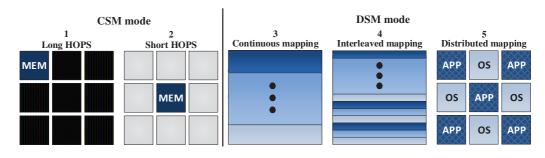

|      | Different evaluated memory mappings                                                  | 88  |

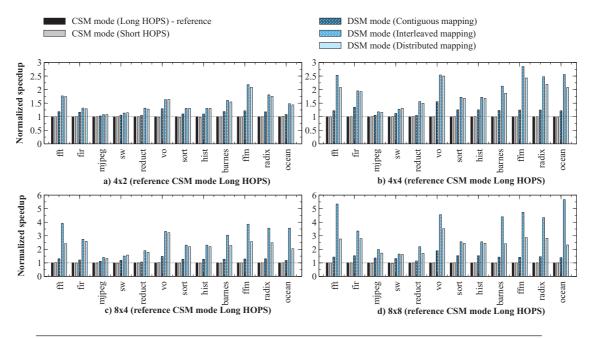

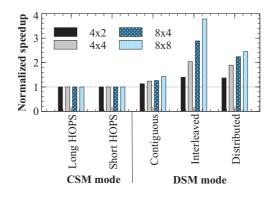

|      | Execution time for different memory mappings and vSMP cluster sizes                  | 89  |

|      | Normalized execution time averaged for all benchmarks                                | 89  |

|      |                                                                                      |     |

| 5.1  | ARM big.LITTLE technology                                                            |     |

| 5.2  | ARM big.LITTLE Cache Coherent Interconnect                                           |     |

| 5.3  | Software execution models for ARM big.LITTLE architecture                            |     |

| 5.4  | ARM big.LITTLE exploration flow                                                      |     |

| 5.5  | Normalized measured speedup                                                          | 98  |

| 5.6  | Runtime breakdown for the Rodinia benchmark                                          |     |

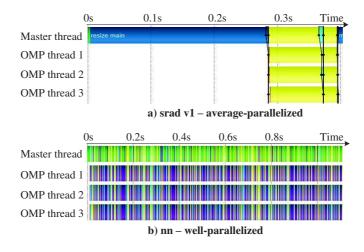

| 5.7  | Runtime behavior analysis for $srad\ v1$ and $nn$                                    | 100 |

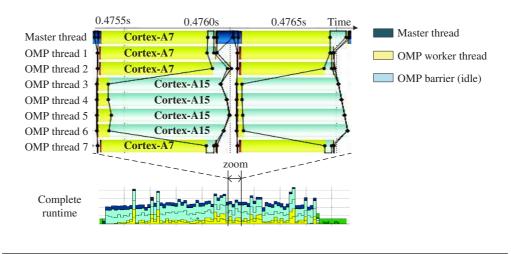

| 5.8  | Runtime behavior: <i>lud</i> executed on HMP big.LITTLE Cortex-A7/A15                |     |

|      | running at 200MHz/2GHz                                                               |     |

| 5.9  | Normalized measured energy-to-solution                                               | 102 |

| 5.10 | Execution time and energy-to-solution comparison between existing and                | 100 |

| F 11 | proposed configurations                                                              |     |

|      | Hotspot parallel region runtime behavior running on the Odroid XU3 board             |     |

|      | Hotspot parallel region trace pattern                                                |     |

|      | Execution time and speedup evaluation using trace-driven simulation                  |     |

|      | Alternative big.LITTLE-based network-on-chip manycore architecture                   |     |

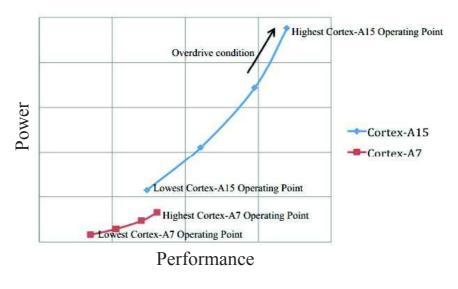

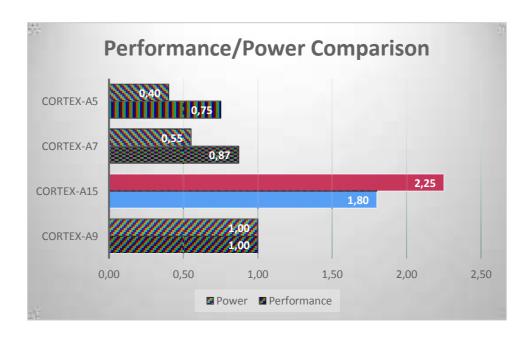

|      | ARM Cortex-A series performance/power ratios                                         |     |

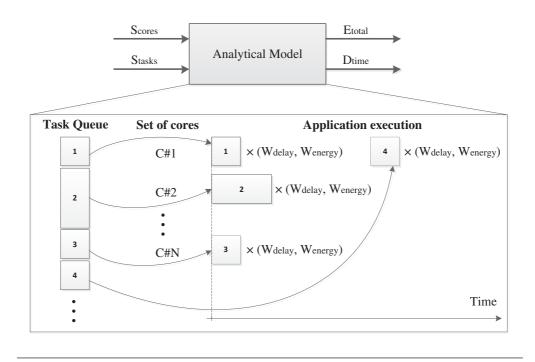

|      | Analytical model functioning                                                         |     |

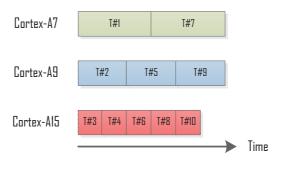

|      | Example of abstract application execution with 10 tasks distribution                 | 111 |

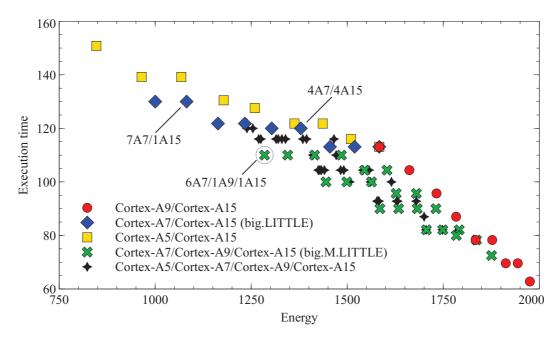

| 5.18 | Heterogeneous architectures energy/delay comparison for equivalent tasks application | 112 |

| 5 19 | Heterogeneous architectures energy/delay comparison for random tasks                 |     |

| 5110 | application                                                                          | 113 |

| 5.20 | Execution behavior of two Rodinia applications                                       |     |

|      |                                                                                      | 115 |

# List of Tables

| 2.1 | Simulation frameworks comparison                                   | 12  |

|-----|--------------------------------------------------------------------|-----|

| 2.2 | Comparison of trace-driven implementations                         | 22  |

| 3.1 | Benchmark set description                                          | 33  |

| 3.2 | Analysis of the $LU$ factorization execution                       | 35  |

| 3.3 | Analysis of the <i>Radix</i> sort kernel execution                 | 36  |

| 3.4 | Memory bandwidth when executing STREAM benchmark                   | 37  |

| 3.5 | Exynos Octa 5422 chip specification                                | 39  |

| 3.6 | Rodinia benchmark description                                      | 43  |

| 3.7 | Cortex-A7 in-order model execution time error summary              | 44  |

| 3.8 | Application different stage comparison                             | 47  |

| 3.9 | big.LITTLE McPAT parameters                                        | 49  |

| 4.1 | Applications description                                           | 78  |

| 4.2 | Application problem size impact on correlation coefficients        | 82  |

| 5.1 | ARM big.LITTLE execution model comparison                          | 96  |

| 5.2 | big.LITTLE proposed configurations                                 | 103 |

| 5.3 | Architecture Configuration                                         | 108 |

| A.1 | Execution time comparison (gem5 versus Exynos Octa 5422)           | 125 |

| B.1 | Power consumption comparison (gem5/McPAT versus Exvnos Octa 5422). | 127 |

# Abbreviations

ALU Arithmetic Logic Unit

API Application Programming Interface

ASV Adaptive Supply Voltage

BSD Berkeley Software Distribution license

CCI Cache Coherence Interface

CMP Chip MultiProcessor

CPU Central Processing Unit

CSM Centralized Shared Memory

Double Data Rate memory

**DES** Discrete-Event Simulation

**DSM** Distributed Shared Memory

DVFS Dynamic Voltage and Frequency Scaling

EtoS Energy-to-Solution

FFT Fast Fourier Transform

FPU Floating-Point Unit

FS Full System

GPU Graphics Processing Unit

GTS Global Task Scheduling

HMP Heterogeneous MultiProcessing

HPC High-Performance Computing

HPL High-Performance Linpack

ILP Instruction Level Parallelism

IPC Instructions Per Cycle

IPS Instructions Per Second

ISA Instruction Set Architecture

Abbreviations xii

ISS Instruction Set Simulator

JIT Just-In-Time

LPDDR Low Power Double Data Rate memory

MESI Modified Exclusive Shared Invalid protocol

MJPEG Motion Joint Photographic Experts Group

MPI Message Passing Interface

MPSoC MultiProcessor System-on-Chip

NA Not Available

NoC Network-on-Chip

OpenMP Open Multi-Processing

OS Operating System

PE Processing Element

PGAS Partitioned Global Address Space

PoP Package on Package

Pthread POSIX thread

RAM Random Access Memory

RTL Register-Transfer Level

SCU Snoop Control Unit

SMP Symmetric MultiProcessor

SMT Simultaneous MultiThreading

SoC System-on-Chip

SPLASH-2 Stanford ParalleL Applications of SHared memory

SPM ScratchPad Memory

TA Trace Arbiter

TBS Time-Based Sampling

TCI Trace Collection Interface

TD Trace-Driven

TI Trace Injector

TLB Translation Look aside Buffers

TLM Transaction-Level Modeling

VHDL VHSIC Hardware Description Language

XML eXtensible Markup Language

# Chapter 1

# Introduction

#### 1.1 Context and Motivation

High-performance computing is a field of computational science intended to perform particularly difficult tasks in the shortest time. Supercomputer is the principal component of an high-performance computing system and has been designed to solve complex high-level computational issues in various scientific domains, e.g. climate research, quantum mechanics, chemical and biological modeling, airplane and spacecraft dynamics simulations, etc. Since the computational needs quickly grow each year, HPC technology becomes a driving force for numerous scientific and consumer areas.

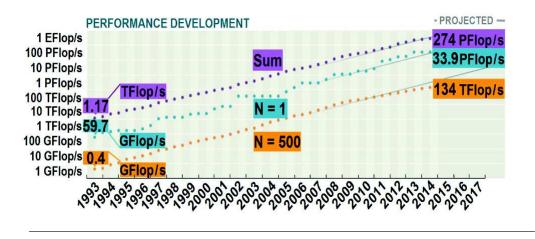

The first supercomputer was built in 1960s by Seymour Cray and since then it undergone a lot of changes and improvements. While at the beginning, supercomputers contained only a few specific purpose processors, current massively parallel samples consist of tens of thousands processors. The TOP500 is a list which ranks the most powerful supercomputers in the world since 1993 [1]. Figure 1.1 illustrates performance development reported by the TOP500 list [2]. The most powerful supercomputer, characterized by the dotted-curve labeled "N = 1", has been progressing from GFLOPS to PFLOPS throughout last twenty years. The current leader of the list is the Tianhe-2 with 54.9 PFLOPS peak performance.

The next frontier in high-performance computing refers to computing systems performing at least one exaFLOPS, i.e. a quintillion floating point operations per second. According to projections, such a system is expected by 2018 with a 20MW power budget [3].

FIGURE 1.1: Performance development in the TOP500 list [2].

Future exascale computing systems face a number of challenges, such as system reliability, energy-efficiency, scalability of software, etc. Energy consumption of HPC systems is an important research field that calls for intense exploration of alternative 'green' technologies.

The Green500 list contains the most energy-efficient supercomputers [4]. Unlike the TOP500 list, it shows the computation rate delivered by a supercomputer per watt. Figure 1.2 shows the list of supercomputers ranked from 1 to 5 in June 2015 [4]. The current leader of the list is the Shoubu supercomputer located at the RIKEN Advanced Institute for Computational Science in Japan. This supercomputer as well as other top representatives is based on the Intel Xeon E5 processor and the InfinityBand communication technology.

| Green500<br>Rank | MFLOPS/W | Site*                                                 | Computer*                                                                                                   | Total<br>Power<br>(kW) |

|------------------|----------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------|

| 41               | 7,031.58 | RIKEN                                                 | Shoubu - ExaScaler-1.4 80Brick, Xeon E5-2618Lv3 8C 2.3GHz, Infiniband FDR, PEZY-SC                          | 50.32                  |

| 2                | 6,842.31 | High Energy Accelerator<br>Research Organization /KEK | Suiren Blue - ExaScaler-1.4 16Brick, Xeon E5-2618Lv3 8C 2.3GHz, Infiniband, PEZY-SC                         | 28.25                  |

| 3                | 6,217.04 | High Energy Accelerator<br>Research Organization /KEK | Suiren - ExaScaler 32U256SC Cluster, Intel Xeon E5-2660v2 10C 2.2GHz, Infiniband FDR, PEZY-SC               | 32.59                  |

| 4                | 5,271.81 | GSI Helmholtz Center                                  | ASUS ESC4000 FDR/G2S, Intel Xeon E5-2690v2 10C 3GHz, Infiniband FDR, AMD FirePro S9150                      | 57.15                  |

| 5                | 4,257.88 | GSIC Center, Tokyo Institute of Technology            | TSUBAME-KFC - LX 1U-4GPU/104Re-1G Cluster, Intel Xeon<br>E5-2620v2 6C 2.100GHz, Infiniband FDR, NVIDIA K20x | 39.83                  |

Figure 1.2: The Green500's energy-efficient supercomputers ranked from 1 to 5 in June 2015 [4].

Nevertheless, to achieve the expected one ExaFLOPS per 20MW a future green supercomputer must provide the 50 GFLOPS/W performance rate. That is seven times

higher than the current most energy-efficient supercomputer is able to produce. Considering the magnitude of the task, researchers have turned to explore low-power embedded system-on-chips as an attractive solution to apply for energy-efficient supercomputing [5].

Being designed to minimize the power consumption, embedded processors feature poor performance versus supercomputer's nodes. The idea to combine multiple SoCs in a large-scale clustered system looks unrealistic due to the potentially vast interconnect traffic. Therefore, embedded processor performance is a key factor to make a substantial progress in that direction.

Looking for ways to improve the performance, embedded systems switched from the operating frequency scaling towards the increasing of on-chip parallelism. The amount of parallelism on a single processor is forecasted to reach hundreds of cores by the end of the decade. Moreover, several alternative architecture configurations arouse the researcher interest revealing a number of budding opportunities. Among them, single-ISA heterogeneous multicore technology [6], which allows operating system to explicitly manage processor load balancing for fine control over performance and power consumption. In the mobile market, several SoC platforms operating on that principle already exist, such as Nvidia Tegra 3/4 SoC [7] and Samsung Exynos 5/7 Octa SoC [8] based on ARM big.LITTLE technology. Despite some important contributions to heterogeneous multiprocessing [6] [9] [10] [11] [12], an adequate solution has not been proposed yet and remains a wide area for further exploration.

Exploration of computer architectures is mainly carried out by means of simulation. Architectural simulators are widely used in academic and industry research. They allow avoiding costly prototyping of real hardware and provide usable environment for design trade-off evaluation. There are three key aspects, which define a computer architecture simulator: accuracy, speed and flexibility.

The accuracy level is determined by the error that the given simulation model produces compared to the reference system. The validation process aims to identify the error value and is a substantiation that the model within its domain of applicability generates results with a satisfactory level of veracity [13]. As high simulation error may lead to wrong conclusions, exploration model validation is strongly required [14].

The simulation speed depends on the abstraction level, which extends between particularly slow cycle-accurate models and imprecise analytical models with simulation time close to real execution. Simulation time remains the major obstacle for efficient architecture exploration forcing researchers to raise the level of abstraction.

In recent years, the computer architecture complexity has grown rapidly, caused by the increasing number of cores, advanced interconnect and memory hierarchy. The desired architectural simulator is expected to provide the environment flexible enough to explore a complete set of design configurations. Debugging capabilities also plays an important role in architecture simulator usability.

Among the existing architecture simulators, cycle-approximate models are of particular interest providing suitable level of accuracy and a wide modeling scope. However, in the context of large-scale manycore architecture exploration, traditional cycle-approximate simulators yet entail slow simulation speed. This calls for alternative approaches capable of providing high simulation speed while preserving the sufficient level of accuracy.

There are various techniques designed to reduce simulation time. They can be classified into two fundamental groups. The first group focuses on increasing computational power [15], i.e. increasing the number of simulated events per second. It is usually achieved by distributing the simulation across multiple host machines. Because of its concurrent nature, distributed simulation faces synchronization issues. To insure simulation consistency, a process running on one host machine might take into consideration the past of other processes. This issue can be addressed either by using looking mechanisms or by allowing synchronization error and applying a rollback procedure [15].

The second group includes approaches designed to reduce the number of simulation events required for accurate results [15]. Trace-driven approach is one of the commonly used solutions. Depending on the target exploration level, it allows abstracting a large number of unnecessary events yet providing relevant results. Namely, for multicore architecture simulation an approach of processor computation abstraction is usually applied. However, such a trace-driven approach has several considerable limitations.

Due to the abstraction of operating system and application execution, synchronization mechanisms dedicated to guarantee data and control flow consistency are left out of consideration. Meanwhile these mechanisms are crucial for manycore architecture exploration.

One more limitation concerns data-dependent applications, i.e. applications in which control flow and memory access pattern are determined by the input datasets. Data-dependent conditionals of such applications cannot be reproduced in the correct order by a trace-driven simulation.

Generally, trace-driven simulation is easy to implement. Nevertheless, the need to deal with the inherent limitations affect its usability. In addition, when computation phase abstraction is used, simulation speedup largely depends on the computation-communication ratio, which is determined by the application nature.

#### 1.2 Thesis objectives and contributions

This thesis is conducted within the Mont-Blanc European project [16]. The main goal of the project is to design a new energy-efficient supercomputer based on the low-power embedded technologies.

This thesis focuses on two interconnected research directions. The first direction aims to develop a fast, flexible and accurate environment for efficient architecture simulation. The second direction is dedicated to multi- and manycore architectures exploration using the proposed simulation environment.

Objective 1 The first objective of this thesis is to answer the following questions:

**Q:** How accurate are performance and power models implemented in cycle-appro ximate full system simulation frameworks? What are the main sources of error in these models? Can these models be used to realistically predict important exploration metrics?

For this purpose, we implement performance models of two multicore SoCs in gem5 cycle-approximate simulation framework [17] and a power model in McPAT simulation framework [18]. These models are then validated against the real hardware. Based on the simulation results we analyze sources of error in the proposed models and summarize whether these models can be used in architecture exploration and under what conditions.

The main contributions of this work are the first-published evaluation and detailed analysis of multicore performance/power models implemented in gem5/McPAT simulation frameworks. Moreover, the evaluated models are made to be freely available online for the research community. This work is supported by the following publications:

- [19] A. Butko, R. Garibotti, L. Ost, and G. Sassatelli. Accuracy evaluation of gem5 simulator system. In Reconfigurable Communication-centric Systems-on-Chip (ReCoSoC), 2012 7th International Workshop on, pages 1–7, July 2012

- [20] A. Butko, A. Gamatié, G. Sassatelli, L. Torres, and M. Robert. Design exploration for next generation high-performance manycore on-chip systems: Application to big.little architectures. In VLSI (ISVLSI), 2015 IEEE Computer Society Annual Symposium on, July 2015

**Objective 2** The second objective of this thesis is to develop a flexible framework enabling fast and yet accurate simulation for manycore architecture exploration. Under this study, we address the following questions:

**Q:** How can simulation time can be reduced while preserving the accuracy level? What are the limitations of the existing approaches and how can they be avoided? Is the proposed approach efficient enough to enable future manycore architecture exploration?

Our contribution differs from all previous works by proposing a novel hybrid traceoriented simulation approach suitable for an efficient exploration of entire manycore system. It includes fully simulated memory infrastructure, trace synchronization technique, trace replication technique and computation phase scaling technique. Altogether, the proposed approach demonstrates significantly reduced simulation time and high accuracy level compared to reference full system simulation. Also, the source code of the proposed approach implementation is freely available on the project webpage [21]. This work is supported by the following publication:

[22] A. Butko, R. Garibotti, L. Ost, V. Lapotre, A. Gamatié, G. Sassatelli, and C. Adeniyi-Jones. A trace-driven approach for fast and accurate simulation of manycore architectures. In *Design Automation Conference (ASP-DAC)*, 2015 20th Asia and South Pacific, pages 707–712, Jan 2015

In addition, the proposed approach has been applied to investigate the performance scalability of alternative memory mappings techniques running on compute accelerators. This work has been presented in the PhD thesis of R. Garibotti [23].

#### Objective 3

The third objective of this thesis is to explore multi- and manycore architectures in terms of performance and energy-efficiency trade-offs using the proposed simulation environment. At this stage, the following questions are raised:

Q: Which configurations of single-ISA heterogeneous architectures can significantly enhance the system energy-efficiency? How can the existing programming models be used to benefit from single-ISA heterogeneous multi- and manycore architectures? How can the proposed simulation environment be used to facilitate the design space exploration of the target architecture?

In this context, we explore single-ISA heterogeneous multicore architectures in terms of performance and energy trade-offs. Based on the detailed analysis and using the described simulation environment, we propose alternative architecture configurations, which demonstrate significant enhancements in energy-efficiency. The publications related to this work are currently under submission.

#### 1.3 Thesis organization

This thesis is organized as follows: Chapter 2 presents the state-of-the-art concerning computer architecture simulation techniques, existing simulation frameworks, accuracy evaluations of performance and power models and existing solutions for large-scale many-core architecture simulations. In Chapter 3 the implementation, validation and analysis of performance and power models are described. The hybrid trace-driven approach, the synchronization and replication techniques and also the computation phase scaling technique are described in Chapter 4. The detailed analysis of existing ARM big.LITTLE SoC and exploration of relevant alternative configurations are presented in Chapter 5. Chapter 6 draws conclusions and discusses possible directions for future work.

### Chapter 2

# State-of-the-art

This chapter presents a survey of the areas relevant for the thesis. Section 2.1 provides a general background of computer architecture simulation techniques. Section 2.2 describes the existing simulation frameworks. The accuracy evaluations of performance and power models are presented in Section 2.3. In Section 2.4 we discuss the existing solutions for large-scale manycore architecture simulations.

#### 2.1 Computer architecture simulation

The computer architecture simulator or architectural simulator is a software tool that models a computer architecture in order to predict a required set of output metrics, e.g. performance, power, architectural statistics, etc. Architectural simulators have been widely used since the beginning of the computer era for many reasons. It allows evaluating various architecture designs without building expensive real hardware systems. Unlimited access to architecture component description provides the possibility to evaluate non-existing implementations. Moreover, a large set of output metrics can be easily obtained by static or dynamic collection. This also greatly simplifies the debugging of the evaluated system.

Time progress management. Talking about simulation, a notion of *simulation time* appears and it inherently differs from the continuous time of reality. There are three conceptual time advancement strategies: activity scanning, event scheduling and process interaction [24].

Under the activity scanning, time is divided into tiny increments and a simulator continuously tracks system dynamics over time. Naturally, for most time increments, no changes in system state will happen and activity tracking will needlessly waste simulation time. For this reason, the activity scanning strategy is very time consuming. Several works however implement this time simulation strategy [25] [26].

In event scheduling which is also known as event-driven simulation [27], time advances discontinuously from one event to another. This time management strategy is more efficient because it does not require computations to be performed during inactive periods. The credibility of the algorithm of next-event scheduling determines the simulation accuracy.

For process interaction paradigm each simulation activity is modeled by a process. Often the process-oriented view is internally implemented on the top of an event-oriented framework [28]. Compared to the event scheduling simulation, it is much slower, and more difficult to implement and debug [26].

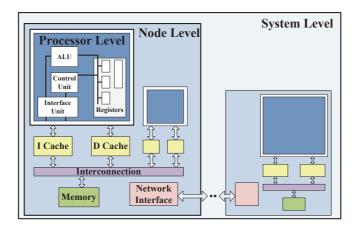

Simulation scope. Depending on the simulator implementation, it can provide a wide range of design exploration features. Processor microarchitecture, multi-level cache hierarchy, complete multicore system including interconnect and memory infrastructure [29] make a part of supported simulation scope. We specify some of them that are used in further simulators analysis.

An instruction set or instruction set architecture specifies a set of basic instructions that a processor supports. It also includes the size of main memory, number of registers and instruction format.

An *instruction set simulator* is used to emulate the processor behavior by using the instruction set and maintaining internal variables which represent processor registers [30].

A full system simulation models the entire system, making target software, e.g. OS and application, believe that it is running on a real physical hardware [31].

**Abstraction level.** Depending on the level of details, architectural simulators are also classified on different abstraction levels. The golden point design is an approach to specify architectures in a very detailed level using hardware description languages like VHDL or Verilog. This limited RTL abstraction gives high timing accuracy, but in turn poses

severe limitations on design space exploration, extremely time consuming and difficult to debug.

Cycle-accurate simulator is a software model, usually coded in a high-level programming language [32]. It reproduces the cycle-by-cycle system behavior. Furthermore, cycle-accurate models facilitate analysis iterations around various architectural options as well as software execution, which gives flexibility to explore more features than in a low-level abstraction model. Such simulators also may contain components with lower accuracy levels. In this case, it is referred as quasi cycle-accurate or cycle-approximate simulator.

Following this direction, there are function-accurate models, instruction-accurate models and others high-level abstraction models, which result in faster simulation at the cost of a loss of accuracy.

An analytical model is a mathematical model which contains a set of equations describing the performance of a computer system. Despite the low level of accuracy, analytical modeling remains a highly practical method of analysis because of its relative simplicity and high simulation speed [33].

#### 2.2 Simulation frameworks

Based on the listed in Section 2.1 simulation characteristics, we provide a detailed analysis of the existing computer architecture simulators. The following criteria are taken into account: accuracy, simulation speed, supported processor architectures, licensing, development activity and simulation scope features. In the context of multi- and manycore architecture exploration, the desired simulation scope includes full system simulation, unmodified OS support, multiprocessing, detailed cache, interconnect and memory architecture. Microarchitecture detailed simulation is advisable, but in the large scale manycore architecture exploration it is unnecessary.

Table 2.1 summarizes the analysis of simulation frameworks. It also presents key features list, which is filled with three types of marks: ' $\checkmark$ ' - fully supported, '\*' - partially supported and ' $\times$ ' - not supported. The 'partially supported' mark is used to identify a simplistic implementation of a feature or in case the relevant information is poorly described in the reference.

PTLsim [34] is a cycle-accurate full system x86 microprocessor simulator that has an out-of-order pipelined model. PTLsim also supports modeling of multiprocessor or simultaneous multithreading machines. The error of PTLsim compared to the reference silicon (AMD Athlon 64 at 2.2 GHz) is within 5% across major parameters. Microoperation (uops) metric differs in 31%. Simulation speed is around 270 KIPS. PTLsim presents two main drawbacks, only x86 architectures are supported and the tool suite is not actively maintained anymore.

MARSSx86 [35] is based on PTLsim with extensive enhancements for improved simulation accuracy and performance. It complements PTLsim key features with unmodified operating system running, detailed models for coherent caches, on-chip interconnections and advanced multiprocessing simulation. Simulation speed is around 200 KIPS. Accuracy validation results are not available. As PTLsim, MARSS focuses only on x86 architecture.

Simics is a functionally-accurate full system simulator that enables unmodified target software (e.g. operating system, applications) to run on the virtual platform similar to the physical hardware [36]. Simics supports a wide range of processor architectures (e.g. Alpha, ARM, MIPS, PowerPC, SPARC, x86), as well as operating systems (e.g. Linux, VxWorks, Solaris, FreeBSD, QNX, RTEMS). Simics is composed of an instruction-set simulator, memory-management units models, as well as all memories and devices found in the memory map of the processors. Simics has two main disadvantages, it is not claimed to be cycle-accurate and a commercial license is required (marketed by Wind River Systems [37]). Besides the general functional-accurate class, other information about accuracy validation is not available. Simulation speed is around 300 KIPS for a detailed out-of-order architecture simulation and 6.6 MIPS for a fast simulation.

Flexus [38] is a computer architecture simulator based on Virtutech Simics. In contrast to Simics, it is open source but supports only SPARC ISA. Simulation speed varies from 20-25 KIPS for a detailed simulation to 30-90 MIPS for a fast simulation. Accuracy validation results are not available.

**SimpleScalar** is an open source infrastructure for simulation and architectural modeling. It supports several processor architectures including Alpha, ARM, PowerPC and

x86. Moreover, it features a large range of CPU models, which varies from simple unpipelined processors to detailed dynamically scheduled microarchitectures with multiple-level memory hierarchies [39]. The IPC accuracy had been validated against the SA-1110 platform and showed 3% of error. It provides two simulation modes, which differ in details and speed. Sim-OutOrder detailed mode runs at 350 KIPS, Sim-Fast mode runs at 10 MIPS simulation speed. SimpleScalar features were widely improved in the past, but it seems that both development and support have slowed down significantly. Indeed, the last update is more than four years ago at the time of this writing. Multiple SimpleScalar extensions have been implemented to support multiprocessing/multithreading and thermal models, e.g. SSMT [40], M-Sim [41], SMTSim [42], HotSpot [43].

Multi2Sim is a CPU-GPU heterogeneous computing simulation framework [44]. It has been developed integrating models for superscalar, multithreaded, multicore CPUs/GPU architectures, as well as cache coherence, multi-level cache hierarchy and interconnection networks. ARM, MIPS, NVIDIA Fermi and AMD GPU models are supported by Multi2Sim. It is classified as application-only emulator that focuses on user-level application execution, removing operating system and device drivers. Thereby, simulation speed is around tens of MIPS. However, neither accuracy validation nor simulation speed results are available.

ESESC, i.e. enhanced SESC [45], is an open source implementation of time-based sampling. Authors claim that the proposed framework is the first to enable sampling in simulation of multicore processors with virtually no limitation in terms of application type, number of cores, homogeneity or heterogeneity of the simulated configuration. It is also the first TBS to enable integrated power and temperature evaluation in statistically sampled simulation of multicore systems [46]. The reported error of performance evaluation is within 5% compared to full system simulation. The power and maximum temperature model errors are 5.5% and 2.4% respectively. The sampling technique allows up to 9 MIPS of simulation speed to be reached. Actually, only ARM architecture is available in the ESESC simulator.

Table 2.1: Simulation frameworks comparison.

| Simulator | ISAs | Accuracy | Speed    | Key Features |    |          |          |    |              |              |

|-----------|------|----------|----------|--------------|----|----------|----------|----|--------------|--------------|

|           |      | (Error)  |          | FS           | os | ${f L}$  | MA       | MP | $\mathbf{C}$ | $\mathbf{M}$ |

| PTLsim    | x86  | CA       | 270 KIPS | <b>√</b>     | *  | <b>√</b> | <b>√</b> | *  | *            | *            |

Continued on next page

Table 2.1 - Continued from previous page

| Simulator    | ISAs    | Accuracy      | Speed         | Key Features |              |              |              |              |              |              |

|--------------|---------|---------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

|              |         | (Error)       |               | FS           | os           | ${f L}$      | MA           | MP           | $\mathbf{C}$ | $\mathbf{M}$ |

|              |         | Cycles -4.3%  |               |              |              |              |              |              |              |              |

|              |         | Uops - 30.99% |               |              |              |              |              |              |              |              |

| MARSS        | x86     | CA            | 200 KIPS      | <b>√</b>     |

| b.o. PTLsim  |         | NA            |               |              |              |              |              |              |              |              |

| Simics       | Alpha   | FA            | F: 6.6 MIPS   | <b>√</b>     | <b>√</b>     | ×            | <b>√</b>     | <b>√</b>     | *            | *            |

|              | ARM     | N/A           | D: 300 KIPS   |              |              |              |              |              |              |              |

|              | MIPS    |               |               |              |              |              |              |              |              |              |

|              | PowerPC |               |               |              |              |              |              |              |              |              |

|              | SPARC   |               |               |              |              |              |              |              |              |              |

|              | x86     |               |               |              |              |              |              |              |              |              |

| Flexus       | SPARC   | FA            | F: 30-60 MIPS | <b>√</b>     | <b>√</b>     | <b>√</b>     | <b>√</b>     | <b>√</b>     | ✓            | <b>√</b>     |

| b.o. Simics  |         | N/A           | D: 20-25 KIPS |              |              |              |              |              |              |              |

| SimpleScalar | Alpha   | CA            | F: 10 MIPS    | ×            | X            | <b>√</b>     | *            | <b>√</b>     | ✓            | *            |

|              | ARM     | IPC - 3%      | D: 350 KIPS   |              |              |              |              |              |              |              |

|              | PowerPC |               |               |              |              |              |              |              |              |              |

|              | x86     |               |               |              |              |              |              |              |              |              |

| Multi2Sim    | ARM     | CA            | N/A           | ×            | ×            | $\checkmark$ | <b>√</b>     | $\checkmark$ | <b>√</b>     | $\checkmark$ |

|              | MIPS    | N/A           |               |              |              |              |              |              |              |              |

|              | x86     |               |               |              |              |              |              |              |              |              |

|              | GPUs    |               |               |              |              |              |              |              |              |              |

| ESESC        | ARM     | CA            | E: 90 MIPS    | ×            | X            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | *            |

| b.o. SESC    |         | $FS \pm 11\%$ | F: 9 MIPS     |              |              |              |              |              |              |              |

|              |         |               | D: 500 KIPS   |              |              |              |              |              |              |              |

| gem5         | Alpha   | CA            | E: 5 MIPS     | <b>√</b>     | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

|              | ARM     | N/A           | F: 25 KIPS    |              |              |              |              |              |              |              |

|              | MIPS    |               | D: 1 KIPS     |              |              |              |              |              |              |              |

|              | PowerPC |               |               |              |              |              |              |              |              |              |

|              | SPARC   |               |               |              |              |              |              |              |              |              |

|              | x86     |               |               |              |              |              |              |              |              |              |

|              | GPUs    |               |               |              |              |              |              |              |              |              |

$\operatorname{CA}$  - cycle-accurate,  $\operatorname{FA}$  - function-accurate,  $\operatorname{N/A}$  - not available

b.o. - based on, E - emulation, F - fast, D - detailed

' $\checkmark$ ' - fully supported, '\*' - partially supported, ' $\boldsymbol{\mathsf{X}}$ ' - not supported

FS - full system, OS - operating system, L - licensing, MA - microarchitecture,

$\mathbf{MP}$  - multiprocessing,  $\mathbf{C}$  - cache hierarchy,  $\mathbf{M}$  - memory infrastructure

gem5 [17] is a modular discrete event-driven full system simulator, under BSD license. This simulator supports different instruction set architectures, such as Alpha, ARM, x86, SPARC, PowerPC and MIPS. The simulator provides a flexible, modular simulation system that makes it possible exploring multiprocessor architecture features by offering a diverse set of CPU models, system execution modes, and memory system models. Moreover, this simulator has an active development and support team. Simulation speed is classified into three classes depending on the simulation mode: 1 KIPS for detailed simulation, 25 KIPS for simplified timing simulation and up to 5 MIPS for fast simulation, e.g. emulation. At the beginning of this thesis, no material has been published that reports gem5 accuracy in terms of performance estimation.

Analyzing the summary table, we observe a considerable advantage of the gem5 simulation framework. Fully supporting all key features, it provides seven ISAs and three simulation speed modes. The only characteristic that has been unclear at the beginning of this thesis was the accuracy evaluation.

# 2.3 Accuracy evaluation of gem5 and McPAT simulation frameworks

In this section, we present the main concepts of simulation accuracy, model validation and an overview of the previously published works concerning gem5 performance and McPAT power models evaluation.

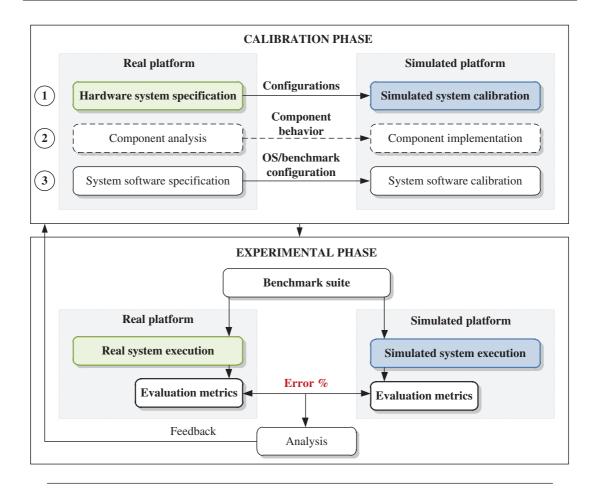

For reliable design space exploration, a three-steps process of preliminary model preparation is required [47]. The first step is model *implementation*. Usually, the most part of architecture components are already available in the simulator. Thus only specific features related to research target need to be implemented. The second step is model *verification* that confirms correct system behavior. The third step is model *validation*. Validation process is aimed to demonstrate that the model is a realistic representation of the architecture under a set of conditions [47]. Validation process includes the comparison to the reference that can be represented by a real hardware in order to identify the error. The accuracy of the simulation framework is a critical aspect for design space exploration. The lack of accuracy knowledge may lead to wrong conclusions. Not only the total runtime error is important, but also the detailed analysis of error sources [14].

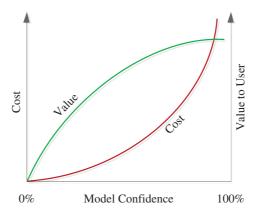

Figure 2.1 illustrates the relationship between model validation cost and value to user. High level of model confidence usually requires more costly efforts for validation.

FIGURE 2.1: Model confidence [13].

Here we present an overview of the previously published works as well as works that are based on the proposed accuracy evaluation and have been published throughout the advancement of this thesis.

Authors in [48] evaluate the accuracy of the M5 full system simulator for TCP/IP based network-intensive workloads, using only two benchmarks that were executed on a single Alpha CPU model. By using a relatively imprecise model they achieve reasonable accuracy - the network bandwidth mismatch against real system is reported within 15%.

Authors in [49] design a gem5 model of CoreTile Express system-on-chip and estimate the accuracy of Cortex-A15 core, memory system and interconnect. They deeply explore the microarchitectural simulation for the homogeneous dual-core system. This work has been done in collaboration with ARM Research in Austin, TX. By thoroughly tuning the ARM CPU model, authors achieve a mean absolute percentage runtime error of 15% (SPEC CPU2006 and PARSEC benchmarks) and an error of 20% on average for several key microarchitectural metrics. Authors conclude that these errors are acceptable and are not a hindrance to evaluating research ideas.

The work presented in [50] deals with the calibration and simulation of Cortex-A8 and Cortex-A9 cores in gem5. A comparison in terms of execution time is achieved against a real hardware execution and based on ten benchmarks. Authors claim that their core

models are more accurate than similar microarchitectural simulators. For both models, the average absolute error is within 17%.

A similar study has been achieved for Cortex-A7 and Cortex-A15 cores in [51] by focusing on the microarchitectural simulation of these cores. The gem5 and McPAT frameworks have been combined to validate area and energy/performance trade-offs against the published datasheet information. However, this work does not aim to evaluate multicore configurations. It only demonstrates the difference between Cortex-A7 and Cortex-A15 cores running single-threaded applications.

Xi et al. in [52] present the first assessment of McPAT's core power and area models. The results show that McPAT's models can provide significant error due to abstraction and modeling errors. They also discuss ways to avoid such errors and improve the architectural power models.

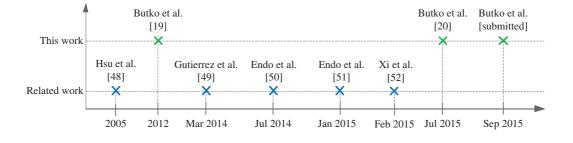

To summarize the related work on accuracy evaluation of gem5 and McPAT, Figure 2.2 depicts the publications appeared throughout the time. This thesis works are also presented in the time scale. In [19], we evaluated the accuracy of the performance model for ARM multicore processors exploration. This work is the first that reports and discusses the accuracy of gem5 framework in terms of performance estimation. The work published in [20] addresses performance model validation of single-ISA heterogeneous big.LITTLE architecture. It covers the comparison of multiple Cortex-A7 in-order implementations as well as multicore simulations in heterogeneous multiprocessing mode. The future publication, which is currently under submission complements the ARM big.LITTLE exploration with power modeling.

FIGURE 2.2: The related work on accuracy evaluation.

#### 2.4 Approaches to accelerate the simulation

Traditional cycle-approximate simulation frameworks entail slow simulation speed, therefore limiting its scope of applicability for systems with hundreds of cores. This calls for alternative approaches capable of providing high simulation speed while preserving accuracy. Over the past decades, various simulation speedup approaches have been presented by researches. All existing techniques can be classified into two fundamental groups depending on the main principle of simulation time reduction approach [53].

The first group focuses on the increasing of computational power, e.g. increasing the number of simulated events per second. Usually it is achieved by running the simulation distributed across multiple host machines [38], [54], [55].

**Distributed simulation.** Graphite [56] is a distributed simulator using dynamic binary translation to deal with functional behavior. It minimizes synchronization overhead by abstracting away events ordering along the simulation. Therefore, while decreasing simulation costs, such a relaxed synchronization vision limits architectural explorations such as communication bottlenecks.

ZSIM [57] improves simulation speed by parallelizing the simulation on x86 multicore hosts performing CPU work using instruction-driven timing models that rely on dynamic binary translation. Authors claim about 2/3 and 4 orders of magnitude speedup than respectively Graphite and gem5. ZSIM supports only x86 ISA-compatible microprocessors.

More generally, the use of distributed simulators is delicate in the sense that users have to carefully deal with simulation partitioning and synchronization among available CPUs, which limits simulation speedup.

JIT dynamic binary translation. The other approach to accelerate the simulation is just-in-time dynamic binary translation, e.g. OVP [58] and QEMU [59]. JIT-based simulators are instrumented with timing models so that basic architecture block models and their inter-operations can be driven according to the annotated timing information. For instance, in the pipeline model included in QEMU [60], authors propose a two-phase approach to estimate the application performance. In the offline phase, a cycle pre-estimation of the application execution time is performed. It is then exploited

adaptively in the *online* phase according to the CPU status and execution time of critical instructions, improving the approach accuracy with a mismatch around 10%. A similar approach [61] combines worst-case execution time analysis and QEMU. Here, the offline phase is composed of four steps producing a timing database used online. These approaches miss expressive modeling supports such as those related to cache hierarchies and coherency protocols. Such simulators can achieve speeds close to thousands MIPS [62] at the cost of a limited accuracy. They often focus on functional validation rather than those of architectural exploration.

The second group includes approaches designed to reduce the number of simulation events required for accurate results. It concentrates on optimizing component descriptions (e.g. CPUs, interconnect infrastructure) following the transaction-level modeling strategy [63] or by using trace-driven simulation [64].

Transaction-level modeling. TLM approach abstracts communications to accelerate system simulation speed and often demonstrates a significant loss in accuracy [65]. In TLM, details of communication are separated from the details of computation components. Communication is modeled as channels usually using SystemC interface classes. Communication requests are performed by calling interface functions [63]. There are a number of works that focus on TLM accuracy problem [66] [67] [68].

Trace-driven modeling. Trace-driven modeling is a relevant approach in high-performance and embedded computing for reducing simulation cost. A various number of works have been proposed over the past decades. They target different system components evaluation, e.g. processor microarchitecture, cache hierarchy, network interconnect, multi-/manycore platforms.

**Processor simulation:** ReSim is a trace-driven reconfigurable ILP processor simulator [69]. It achieves simulation speed up to 28 MIPS and demonstrates an enhancement by at least a factor of 5 enhancement over the reported ILP processor hardware simulators [70] [71].

Cache simulation: An uniprocessor cache simulator based on trace-driven approach has been proposed in [72]. It has been developed to simulate a memory hierarchy consisting of various caches. The simulator produces a set of performance metrics, such as traffic

to and from memory. In [73] Dinero IV has been used to predict the performance of a 3D processor-memory chip stack.

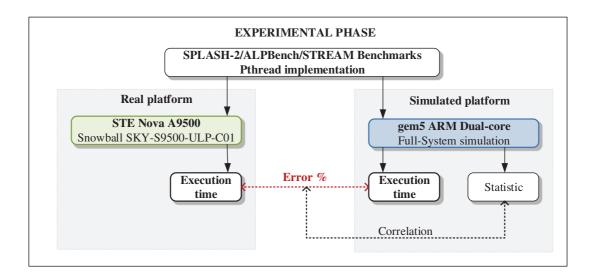

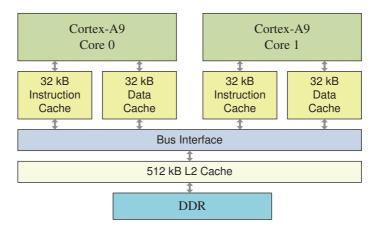

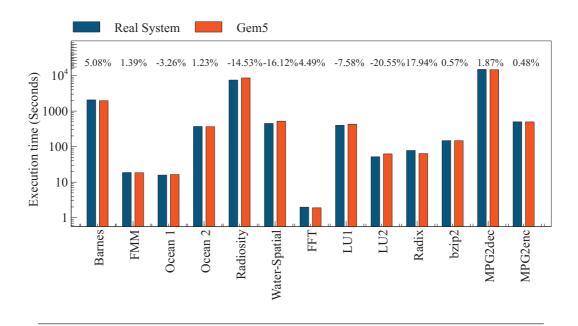

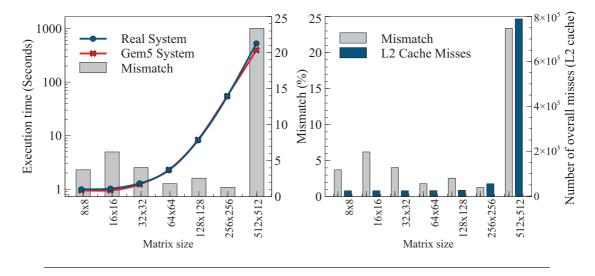

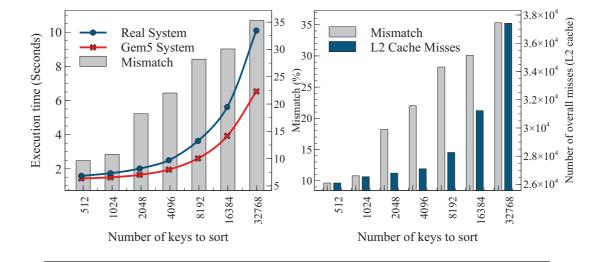

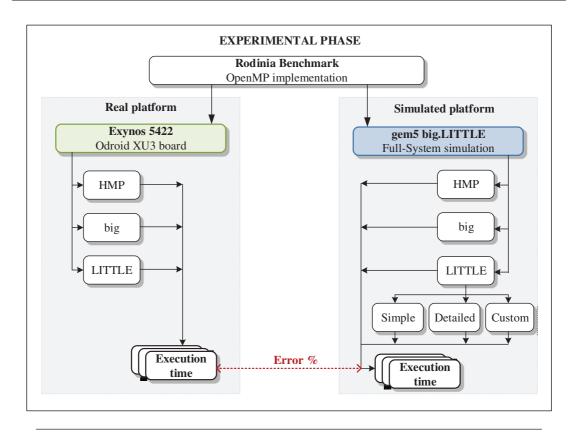

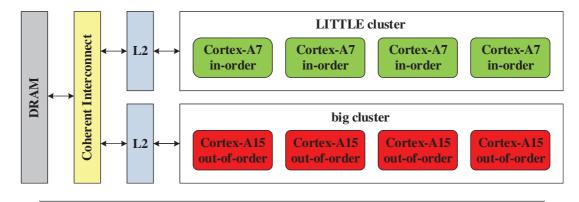

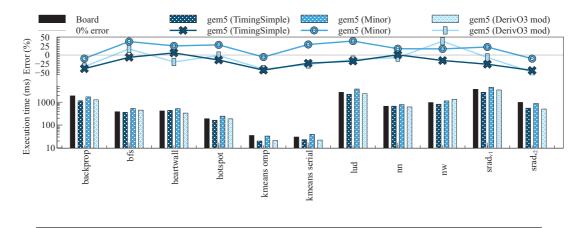

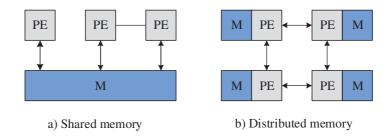

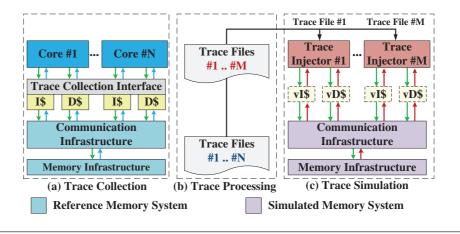

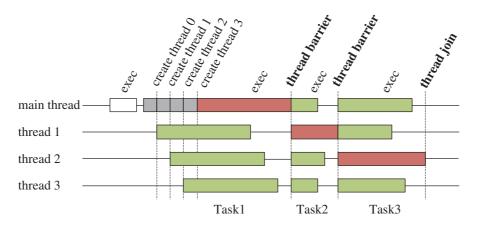

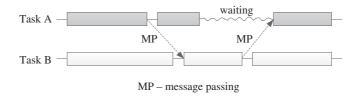

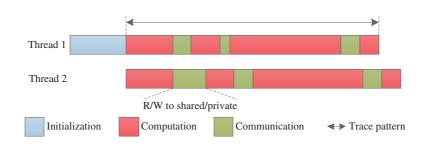

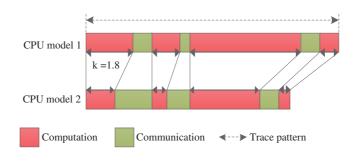

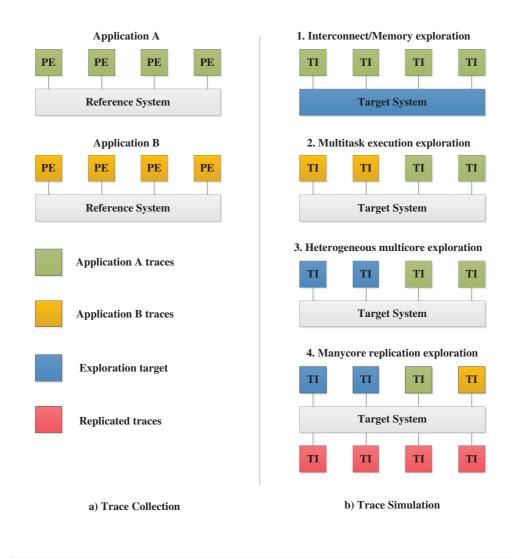

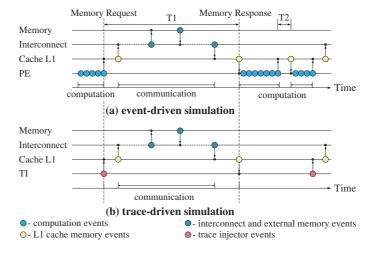

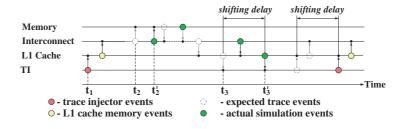

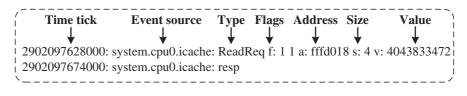

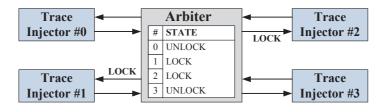

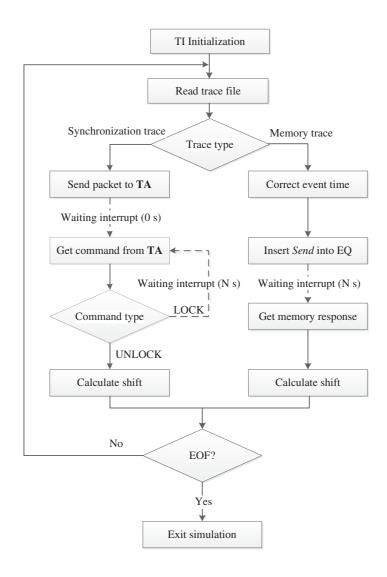

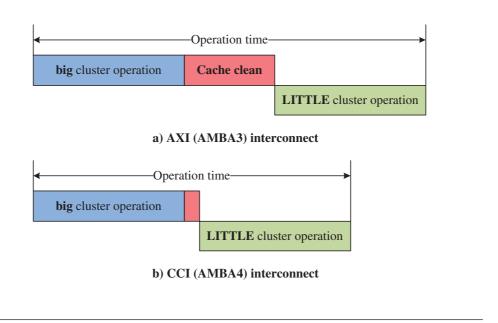

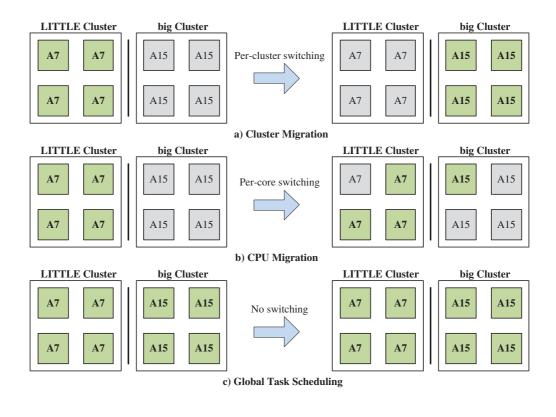

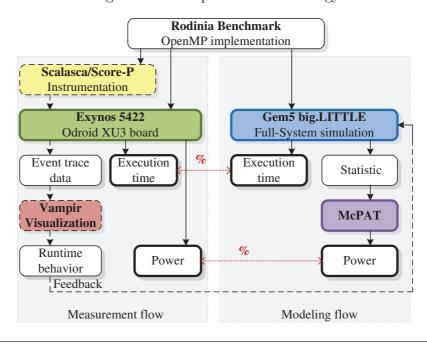

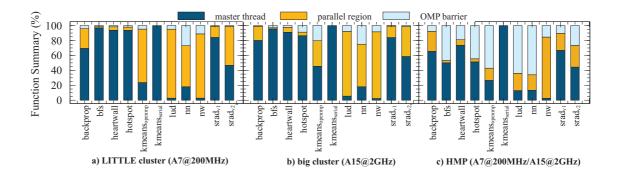

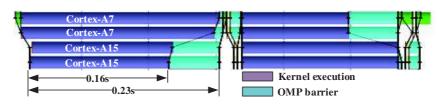

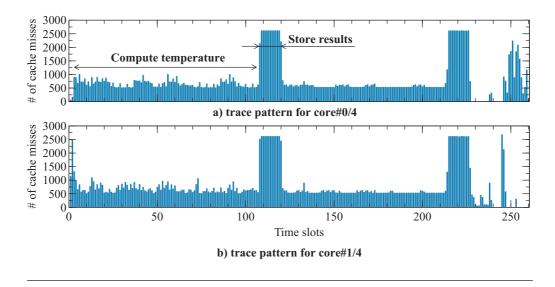

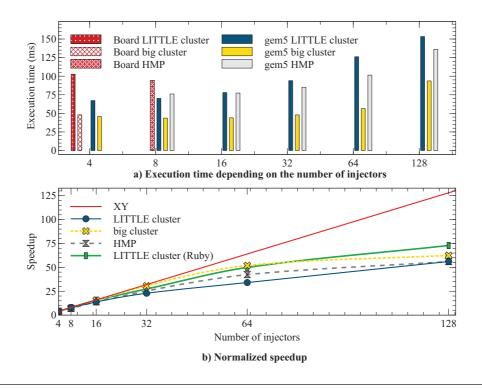

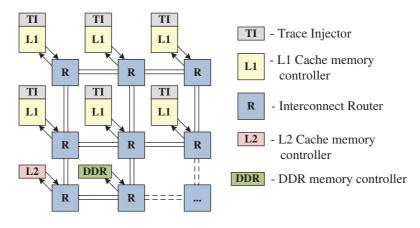

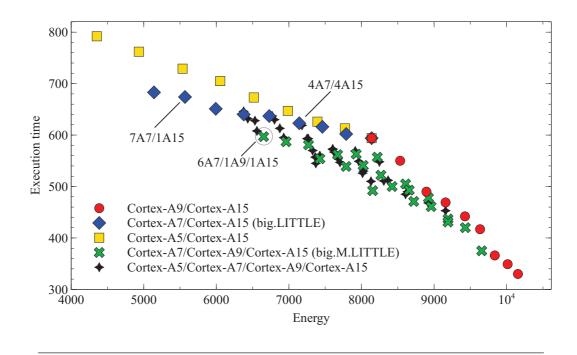

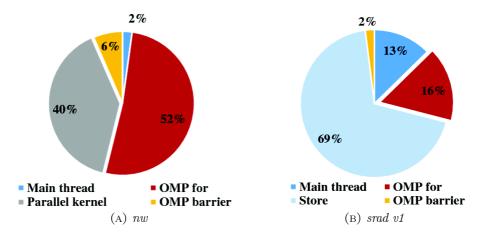

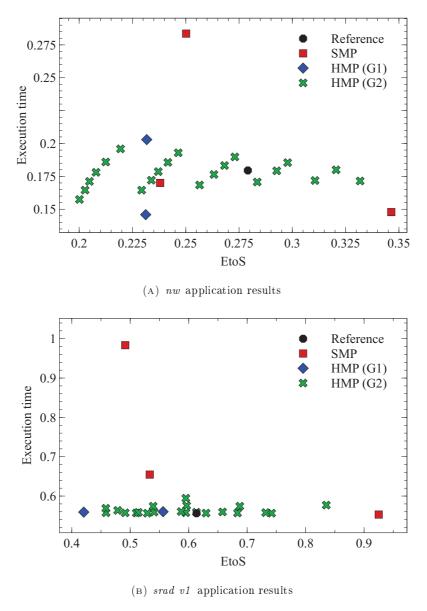

The work in [74] presents a trace-driven tool for cache simulation and memory performance studies. Authors report performance improvements of MetaSim Tracer [75] by using techniques developed in SimPoint [76]. The work reduces the cache simulation overhead by decreasing the number of instructions that must be reproduced during the simulation.