# Systèmes intégrés adaptatifs ultra basse consommation pour l'Internet des Objets

Guillaume Patrigeon

#### ▶ To cite this version:

Guillaume Patrigeon. Systèmes intégrés adaptatifs ultra basse consommation pour l'Internet des Objets. Micro et nanotechnologies/Microélectronique. Université de Montpellier, 2020. Français. NNT: . tel-02947275

## HAL Id: tel-02947275 https://hal-lirmm.ccsd.cnrs.fr/tel-02947275v1

Submitted on 23 Sep 2020

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE POUR OBTENIR LE GRADE DE DOCTEUR DE L'UNIVERSITÉ DE MONTPELLIER

En SyAM - Systèmes Automatiques et Micro-électroniques

École doctorale I2S - Information, Structures et Systèmes

Unité de recherche LIRMM

# Systèmes intégrés adaptatifs ultra basse consommation pour l'Internet des Objets

## Présentée par Guillaume Patrigeon Le 16/07/2020

Sous la direction de Pascal Benoit

## Devant le jury composé de

| Jean-Michel PORTAL  | Professeur à l'Université Aix-Marseille             | Rapporteur         |

|---------------------|-----------------------------------------------------|--------------------|

| Sébastien PILLEMENT | Professeur à l'Université de Nantes                 | Rapporteur         |

| Tanguy RISSET       | Professeur à l'INSA Lyon                            | Examinateur        |

| Laurent LATORRE     | Professeur à l'Université de Montpellier            | Examinateur        |

| Lionel Torres       | Professeur à l'Université de Montpellier            | Examinateur        |

| Pascal Benoit       | Maître de Conférences à l'Université de Montpellier | Directeur de thèse |

Systèmes intégrés adaptatifs ultra basse consommation pour l'Internet des Objets

# Table des matières

| Table des ma   | ıtières                                                     | V   |

|----------------|-------------------------------------------------------------|-----|

| Liste des figu | ıres                                                        | VII |

| Liste des tabl | leaux                                                       | IX  |

| 1. Introd      | uction générale                                             | 1   |

| 1.1. Con       | ntexte                                                      | 1   |

|                | jectif de la thèse                                          |     |

| 1.3. Pro       | jet de recherche en lien avec la thèse                      | 3   |

| 2. Conte       | xte, état de l'art et problématique                         | 5   |

| 2.1. Into      | ernet des Objets, réseaux de capteurs sans fils             | 5   |

| 2.1.1.         | Définition, domaines d'application et architecture          | 5   |

| 2.1.2.         | Nœud capteur                                                |     |

| 2.1.3.         | Stratégies pour l'économie d'énergie                        | 14  |

| 2.2. Tec       | chnologies émergentes                                       | 21  |

| 2.2.1.         | FD-SOI 28 nm                                                | 21  |

| 2.2.2.         | Mémoires non-volatiles                                      | 22  |

| 2.2.3.         | Mémoires magnétiques                                        | 25  |

| 2.3. Éva       | luation des technologies émergentes pour les nœuds capteurs | 33  |

| 2.3.1.         | Évaluation des nœuds capteurs                               | 33  |

| 2.3.2.         | Programmes applicatifs de référence                         | 34  |

| 2.3.3.         | Architectures ultra-basse consommation                      | 36  |

| 2.3.4.         | Évaluation du contrôleur                                    | 38  |

| 2.4. Con       | nclusion                                                    | 40  |

| 3. Métho       | dologie d'évaluation de nœuds de capteurs                   | 43  |

| 3.1. Con       | nception d'une architecture de microcontrôleur              | 44  |

| 3.1.1.         | Spécifications                                              | 45  |

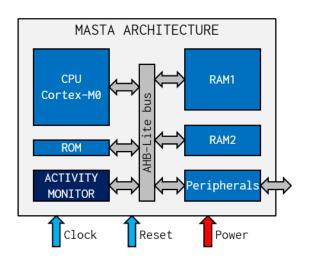

| 3.1.2.         | Architecture MASTA                                          | 50  |

| 3.1.3.         | Interface logicielle                                        | 58  |

| 3.2. Env       | vironnement de validation                                   | 62  |

| 3.2.1.         | Plateforme de prototypage                                   | 63  |

| 3.2.2.         | Prototypage sur FPGA                                        |     |

| 3.2.3.         | Utilisation des ressources                                  | 69  |

| 3.3.      | Implémentation en technologie FD-SOI 28 nm | 71  |

|-----------|--------------------------------------------|-----|

| 3.3       | .1. Cellules propres à la technologie      | 72  |

| 3.3.      | 2.2. Réalisation du circuit                | 77  |

| 3.4.      | Conclusion                                 | 81  |

| 4. Exp    | ploration et résultats                     | 83  |

| 4.1.      | Validation                                 | 83  |

| 4.1.      | .1. Microcontrôleur de référence           | 84  |

| 4.1.      | .2. Différences entre les architectures    | 85  |

| 4.1.      | .3. Résultats                              | 87  |

| 4.2.      | Hybridation des mémoires principales       | 88  |

| 4.2.      | 2.1. Modification de la hiérarchie mémoire | 88  |

| 4.2.      | 2.2. Étude de cas                          | 89  |

| 4.2       | 2.3. Évaluation                            | 91  |

| 4.3.      | Simulation du microcontrôleur FD-SOI 28 nm | 95  |

| 4.3.      | .1. Extraction de l'activité du circuit    | 95  |

| 4.3       | 2.2. Estimation                            | 95  |

| 4.3       | 3.3. Observations                          | 97  |

| 4.4.      | Conclusion                                 | 98  |

| 5. Co     | onclusion et perspectives                  | 101 |

| Bibliogra | ıphie                                      | 105 |

| Liste des | publications                               | 114 |

# Liste des figures

| Figure 1-1 : Historique et projection de 2019 du nombre d'objects connectés dans le monde [1] 1                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2-1 : Représentation de l'architecture typique d'un réseau de capteurs sans fil                                                                                                                                                                                                                                    |

| Figure 2-2 : (a) architecture typique d'un microcontrôleur (simplifié) ; (b) architecture typique d'un microporcesseur à quatre cœurs et deux niveaux de cache (simplifié)                                                                                                                                                |

| Figure 2-3 : Composition d'un nœud                                                                                                                                                                                                                                                                                        |

| Figure 2-4 : Représentation du comportement le plus simple d'un nœud capteur                                                                                                                                                                                                                                              |

| Figure 2-5 : Exemple de stratégie d'économie d'énergie par la réduction du nombre de messages envoyés                                                                                                                                                                                                                     |

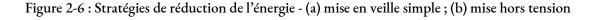

| Figure 2-6 : Stratégies de réduction de l'énergie - (a) mise en veille simple ; (b) mise hors tension 17                                                                                                                                                                                                                  |

| Figure 2-7 : Stratégie de réduction d'énergie - Système normalement éteint                                                                                                                                                                                                                                                |

| Figure 2-8 : Représentation d'une bascule hybride [27]                                                                                                                                                                                                                                                                    |

| Figure 2-9 : (a) transistor Flash à grille flottante [34] [35] ; (b) programmation de la mémoire Flash ; (c) effacement de la mémoire Flash                                                                                                                                                                               |

| Figure 2-10 : (a) composant mémoire ferroélectrique ; (b) transistor ferroélectrique (FeFET) 24                                                                                                                                                                                                                           |

| Figure 2-11 : Composant mémoire à changement de phase (PCM)25                                                                                                                                                                                                                                                             |

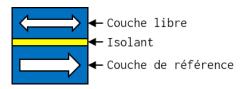

| Figure 2-12 : Perturbation par un champ magnétique des électrons traversant un matériau ferromagnétique, selon leur spin                                                                                                                                                                                                  |

| Figure 2-13 : Magnétorésistance géante (GMR) - (a) état antiparallèle (AP) ; (b) état parallèle (P). 26                                                                                                                                                                                                                   |

| Figure 2-14 : Schéma simplifié d'une jonction magnétique à effet tunnel (MTJ)27                                                                                                                                                                                                                                           |

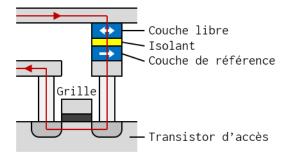

| Figure 2-15 : Cellule mémoire composée d'une MTJ et de son transistor d'accès ; la ligne rouge indique le chemin du courant de lecture [49]27                                                                                                                                                                             |

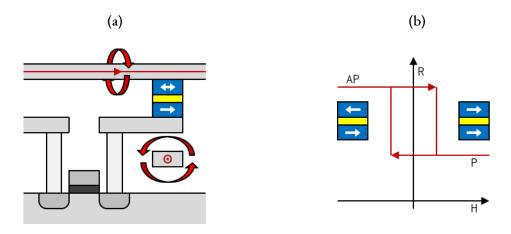

| Figure 2-16 : (a) magnétisation de la couche libre à l'aide de champs magnétiques externes [49] ; (b) cycle d'hystérésis représentant le comportement de la MTJ28                                                                                                                                                         |

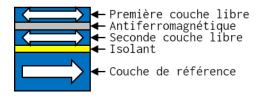

| Figure 2-17 : « Toggle MTJ »                                                                                                                                                                                                                                                                                              |

| Figure 2-18 : Séquence pour faire basculer l'état d'une MTJ de type « toggle », vue de dessus [50] ; les lignes verticales et horizontales représentent les lignes de métal générant les champs magnétiques, les flèches rouges symbolisent le passage du courant, les autres flèches la magnétisation des couches libres |

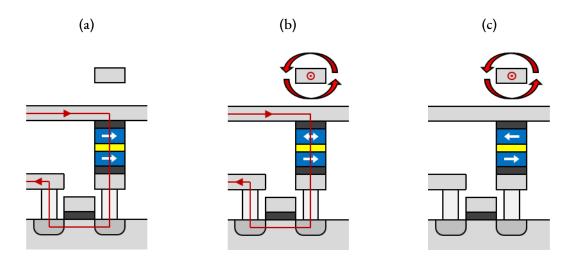

| Figure 2-19 : Séquence d'écriture d'une MTJ avec assistance thermique (TAS) [51] ; (a) chauffage ; (b) écriture ; (c) refroidissement                                                                                                                                                                                     |

| Figure 2-20 : (a) SOT-MTJ ; (b) chemin de lecture ; (c) chemins d'écriture [54]                                                                                                                                                                                                                                           |

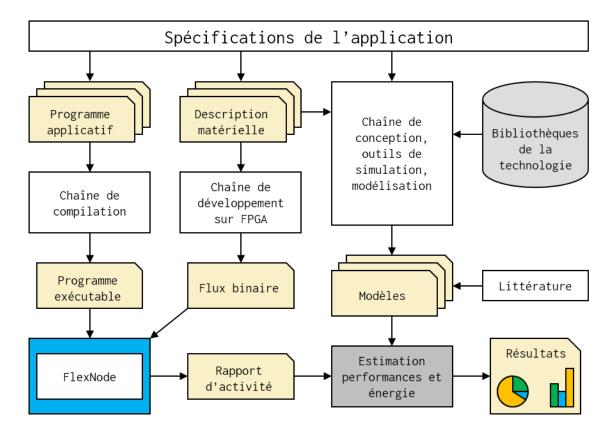

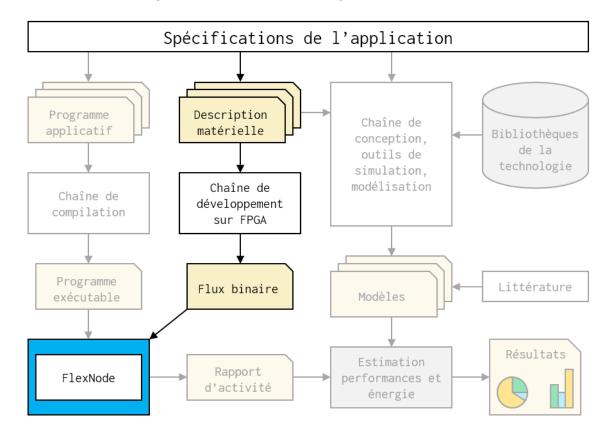

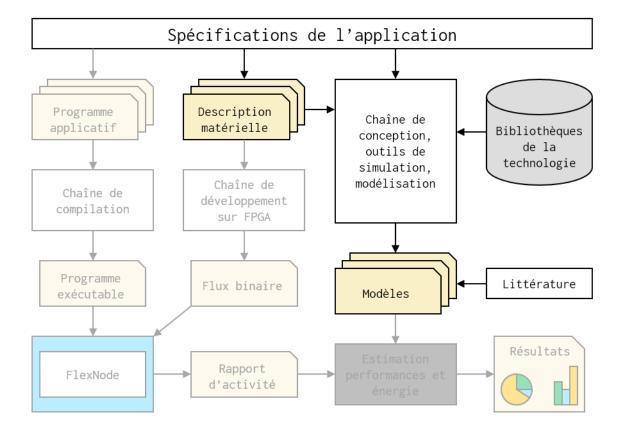

| Figure 3-1 : Flot d'évaluation                                                                                                                                                                                                                                                                                            |

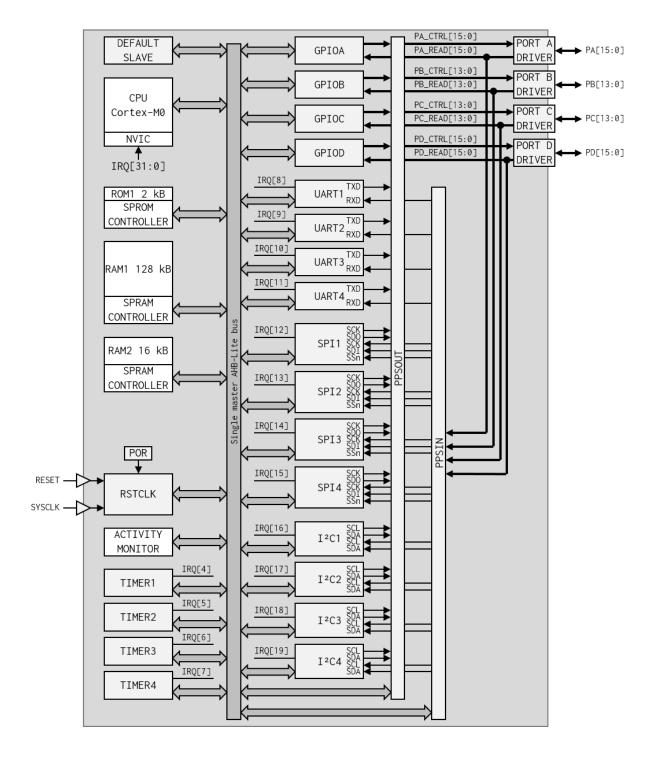

| Figure 3-2 : Architecture du microcontrôleur                                                                                                                                        | 51 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

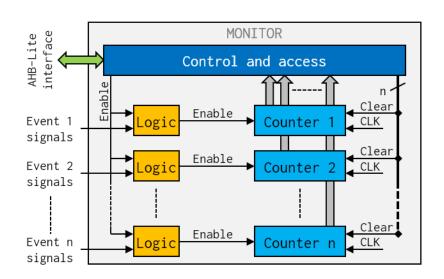

| Figure 3-3 : Architecture du moniteur d'activité                                                                                                                                    | 54 |

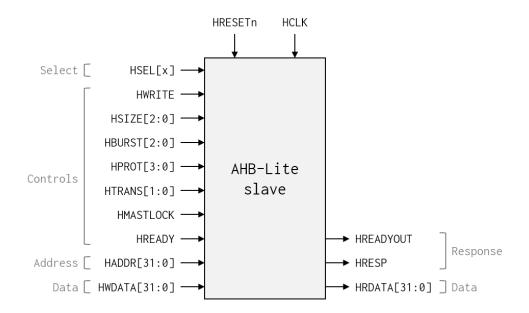

| Figure 3-4 : Interface esclave type AHB-Lite                                                                                                                                        | 55 |

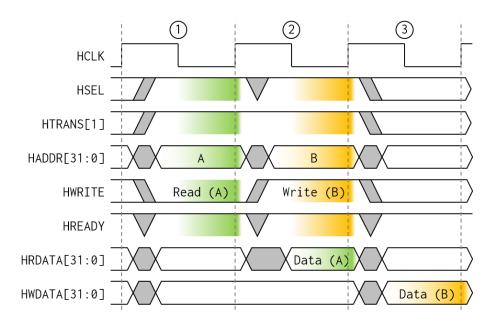

| Figure 3-5 : Chronogramme d'un transfert - Cycle (1) : phase d'adresse A ; cycle (2) : phase de donnée A et phase d'adresse B ; cycle (3) : phase de donnée B                       | 57 |

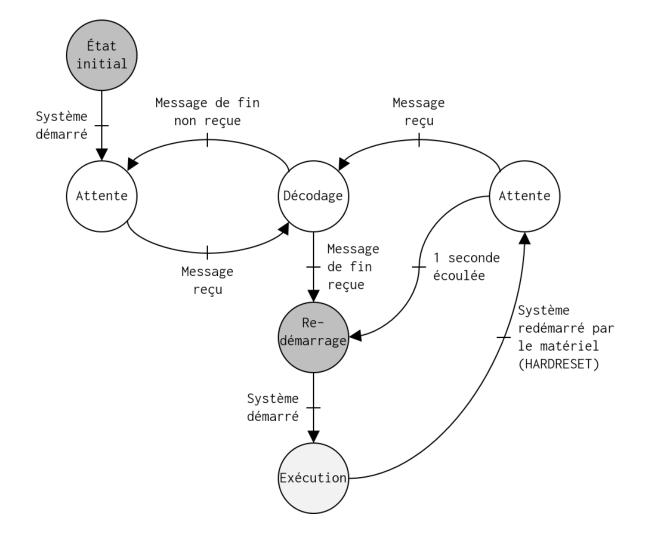

| Figure 3-6 : Comportement du programme d'amorçage                                                                                                                                   | 59 |

| Figure 3-7 : Flot d'évaluation - Implémentation sur FPGA                                                                                                                            | 62 |

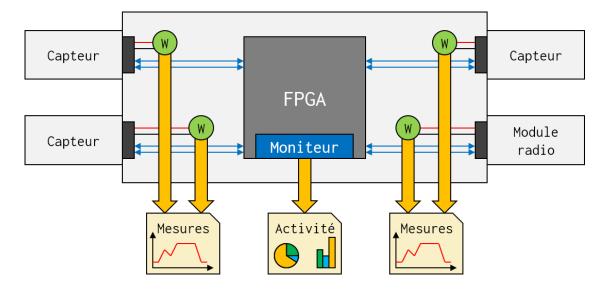

| Figure 3-8 : Schéma de la plateforme de prototypage de nœud capteur                                                                                                                 | 63 |

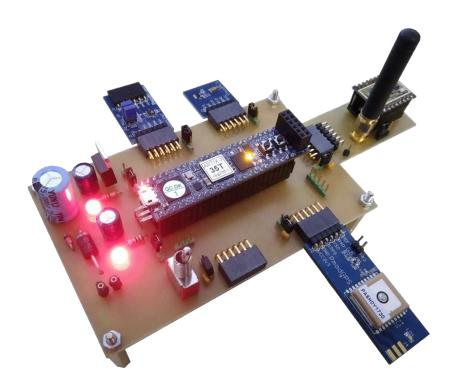

| Figure 3-9 : La première version du FlexNode, avec au centre le Cmod A7                                                                                                             | 64 |

| Figure 3-10 : La seconde version du FlexNode, intégrant les périphériques                                                                                                           | 65 |

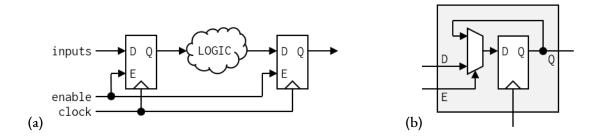

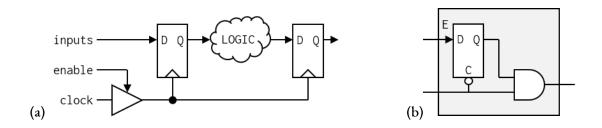

| Figure 3-11 : (a) Exemple de circuit avec un signal d'activation d'horloge ( <i>enable</i> ) ; (b)  Représentation de la bascule avec signal d'activation utilisée dans (a)         | 68 |

| Figure 3-12 : (a) Exemple de circuit avec un signal d'horloge commandé par porte ; (b)<br>Représentation de la cellule utilisée pour la commande du signal d'horloge du circuit (a) | 68 |

| Figure 3-13 : Schéma fonctionnel du microcontrôleur validé sur FPGA                                                                                                                 | 70 |

| Figure 3-14 : Flot d'évaluation - Modélisation                                                                                                                                      | 72 |

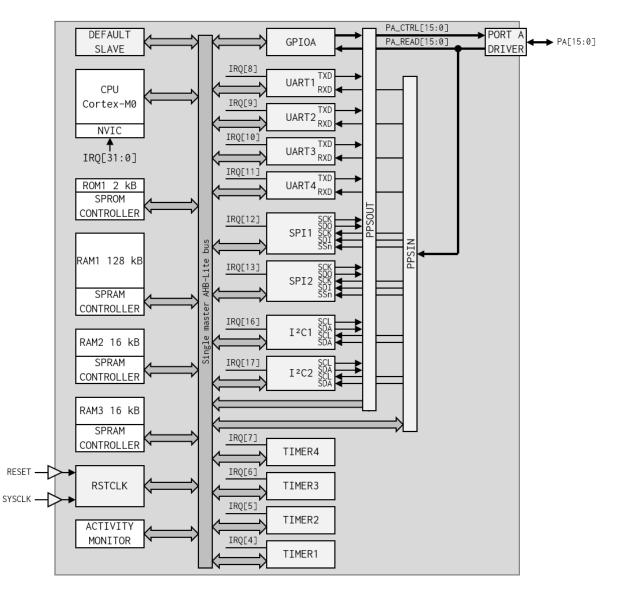

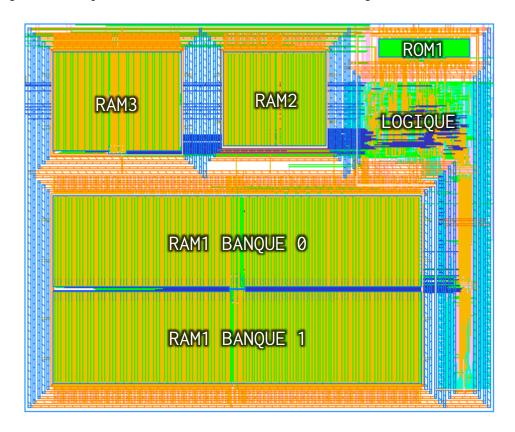

| Figure 3-15 : Schéma fonctionnel du microcontrôleur implémenté                                                                                                                      | 77 |

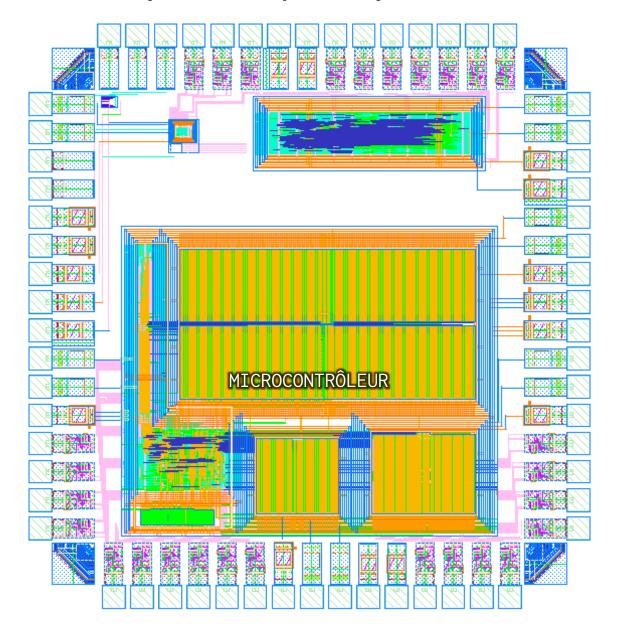

| Figure 3-16 : Représentation du microcontrôleur avant son intégration dans le circuit final                                                                                         |    |

| Figure 3-17 : Circuit complet en technologie FD-SOI 28 nm                                                                                                                           | 81 |

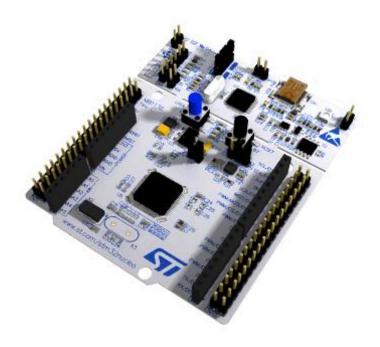

| Figure 4-1 : Carte d'évaluation STM32F072 Nucleo-64                                                                                                                                 | 84 |

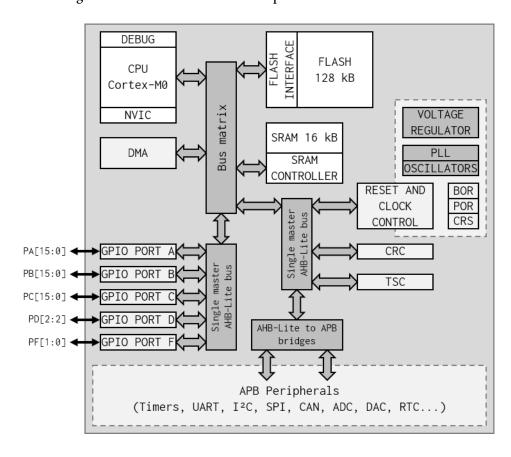

| Figure 4-2 : Schéma fonctionnel simplifié de la STM32F072RBT6                                                                                                                       | 85 |

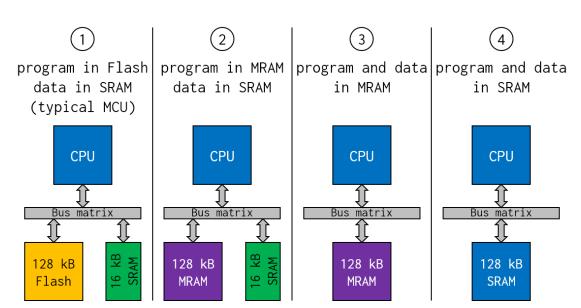

| Figure 4-3 : Représentation de l'architecture du système pour les quatre configurations                                                                                             | 90 |

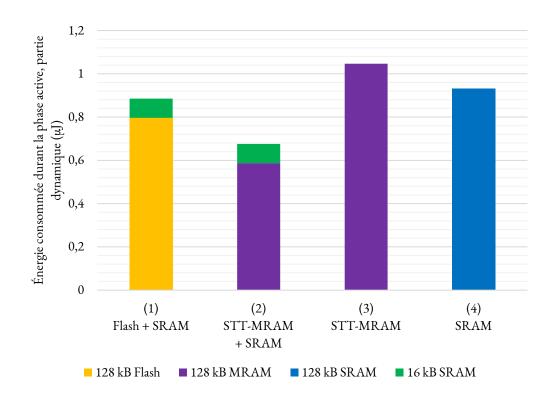

| Figure 4-4 : Partie dynamique de l'énergie consommée par les mémoires durant la phase active                                                                                        | 93 |

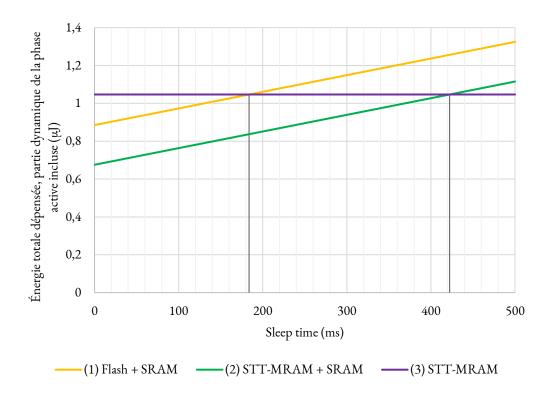

| Figure 4-5 : Énergie perdue par les mémoires durant la phase de sommeil                                                                                                             | 94 |

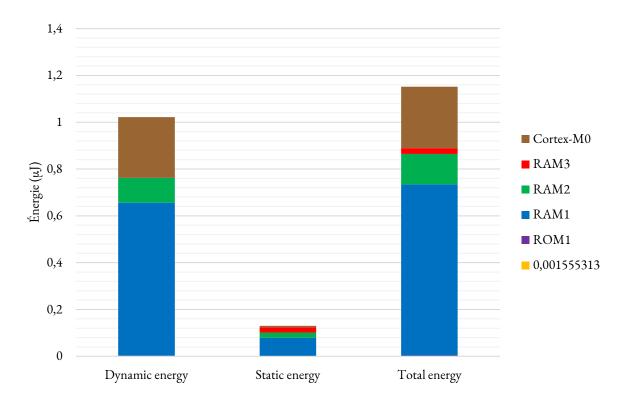

| Figure 4-6 : Estimation de la consommation d'énergie obtenue par simulation                                                                                                         | 96 |

# Liste des tableaux

| Tableau 2-1 : Comparaison des différentes technologies de mémoire magnétique [55]                                                              | 32          |

|------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Tableau 2-2 : Comparaison des différentes technologies mémoires [56]                                                                           | 33          |

| Tableau 2-3 : Caractéristiques de microncontrôleurs ultra-basse consommation intégrant des technologies émergentes                             | 37          |

| Tableau 3-1 : Architecture mémoire des microcontrôleurs 32 bits très basse consommation du commerce                                            | <b> 4</b> 7 |

| Tableau 3-2 : Architecture mémoire de prototypes de microcontrôleurs 32 bits très basse consommation                                           | 48          |

| Tableau 3-3 : Spécifications de l'architecture MASTA                                                                                           | 50          |

| Tableau 3-4 : Organisation mémoire du moniteur d'activité                                                                                      | 61          |

| Tableau 3-5 : Registre de contrôle (CR, <i>Control Register</i> ) du moniteur d'activité                                                       | 61          |

| Tableau 3-6 : Resources du FPGA utilisé par le microcontrôleur                                                                                 | 71          |

| Tableau 3-7 : Caractérisiques de la banque STT-MRAM de SPINTEC                                                                                 | 74          |

| Tableau 3-8 : Configuration des contrôleurs d'entrées/sorties                                                                                  | 75          |

| Tableau 3-9 : Caractéristiques des implémentations FPGA et ASIC du microcontrôleur                                                             | 76          |

| Tableau 4-1 : Comparaison des caractéristiques et des résultats obtenus entre le microcontrôleur implémenté sur FPGA et le STM32F072 Nucleo-64 |             |

| Tableau 4-2 : Coût énergétique par opération pour chaque mémoire                                                                               | 91          |

| Tableau 4-3 : Détails des opérations mémoires lors de la phase active de l'application de référence                                            | e 92        |

# 1. Introduction générale

## 1.1. Contexte

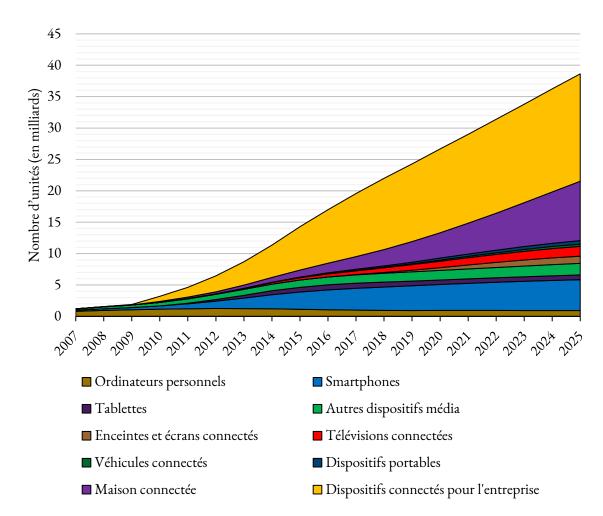

38,6 milliards, c'est le nombre d'objets connectés dans le monde en 2025 selon les prédictions de Strategy Analytics réalisées en mai 2019 [1]. De plus en plus de circuits électroniques et micro-électroniques prennent place dans notre quotidien et leur nombre ne cesse d'augmenter (Figure 1-1).

Figure 1-1 : Historique et projection de 2019 du nombre d'objects connectés dans le monde [1]

Si leur nombre augmente, la taille de ces dispositifs quant à elle tend à diminuer, afin qu'ils soient moins intrusifs et plus facilement intégrables dans leur milieu d'évolution, grâce aux avancées technologiques réalisées ces dernières années. Mais cette réduction de la taille amène à la réduction d'une partie de ressources disponibles sur ces produits, et plus particulièrement l'énergie, point très critique pour les applications de l'Internet des Objets. En parallèle, les circuits embarqués deviennent de plus en plus complexes, afin d'y intégrer plus de sécurité, plus de fonctionnalités, et de les rendre

plus fiables. Cette augmentation de la complexité se traduit par une augmentation de la capacité à traiter l'information, et par conséquent un besoin en énergie plus grand. La technologie CMOS a toutefois évolué elle aussi, permettant de répondre à cette augmentation de la complexité tout en étant plus efficace énergétiquement. Cependant, cette amélioration progressive n'est pas éternelle et des limites de la technologie semi-conducteur ont été atteintes : les performances des processeurs augmentent difficilement depuis quelques années, si bien qu'ils sont mis en parallèle pour gagner en performances de calcul ; les effets parasites comme la résistance et l'effet capacitif des lignes de métal sont trop importants ; la densité de puissance augmente ; le nombre de défauts lors de la fabrication est plus important. Le développement des circuits intégrés est alors ralenti : pour réduire la proportion de circuits défaillants en sortie de production, le nombre de règles de conception augmente, allongeant alors le temps nécessaire à leur vérification.

La technologie CMOS traditionnelle n'est alors plus suffisante pour répondre aux contraintes posées par une grande partie des applications. Des solutions alternatives sont alors envisagées pour compléter ou remplacer la technologie traditionnelle et permettre la conception de circuits intégrés toujours plus rapides, plus petits, plus fiables, plus efficaces énergétiquement et moins coûteux. Deux points clefs sont ciblés : les éléments de mémorisation et la technologie transistor.

Différents types d'éléments dédiés à l'entreposage des données sont utilisés dans la hiérarchie mémoire des systèmes sur puces embarqués. Des registres du processeur et de ses périphériques aux mémoires principales, différentes solutions sont aujourd'hui utilisées selon les besoins exprimés en tous points de cette hiérarchie : temps de lecture, temps d'écriture, énergie nécessaire pour chaque opération, débit maximum, énergie statique, capacité, encombrement, non-volatilité, accès direct, procédé de fabrication, coût. Chaque solution présente des caractéristiques différentes, avec ses points forts mais également des contraintes. Ainsi, la technologie mémoire utilisée pour entreposer un programme applicatif n'est pas la même que celle utilisée pour contenir l'état du processeur. Aucune des solutions actuelles ne pouvant idéalement remplacer chaque élément de mémorisation d'un système sur puce sans contraintes, c'est un assemblage de différentes technologies qui permet d'obtenir une hiérarchie mémoire optimisée, mais certes pas encore idéale.

Afin d'améliorer l'efficacité énergétique de ces circuits, des stratégies d'économie d'énergie sont mises en place pour réduire leur consommation en courant, plus particulièrement en limitant ou en supprimant les pertes dues à des éléments internes ou à des parties de ces derniers lorsqu'ils sont inactifs, et ce grâce à des techniques de régulation dynamique de l'alimentation et de la performance des éléments concernés (DVFS, *Dynamic Voltage and Frequency Scaling*). Mais plus la stratégie est agressive en terme d'économie d'énergie, plus elle est contraignante : augmentation de la complexité des circuits, de leur temps de conception et de réalisation; temps de réaction plus long face à un événement selon le mode d'économie d'énergie utilisé; gestion des différentes stratégies pas toujours évidente; temps de développement plus long...

L'utilisation de solutions alternatives est nécessaire pour outrepasser les limites des technologies actuelles. Si différentes options sont envisagées, l'intégration d'une technologie mémoire magnétique dans les systèmes embarqués est une solution prometteuse qui apporterait une nouvelle façon de gérer de l'énergie pour les applications de type Internet des Objets.

## 1.2. Objectif de la thèse

De nouvelles stratégies et solutions techniques sont proposées pour améliorer l'efficacité énergétique des dispositifs sans fils utilisés pour de nombreuses applications de l'Internet des Objets; les solutions traditionnelles n'étant plus suffisantes pour une partie des applications. La combinaison de deux technologies sera à l'étude au cours de cette thèse: la technologie FD-SOI (silicium sur isolant) et les mémoires magnétiques, plus particulièrement de type STT. Le premier objectif de la thèse est de définir et mettre en place les outils nécessaires à l'évaluation de ces nouvelles solutions intégrées dans les microcontrôleurs, et de définir une méthodologie d'évaluation adaptée et tenant compte du contexte applicatif. Les technologies mémoires non-volatiles permettent de mettre en place de nouvelles stratégies pour la gestion de l'énergie, en particulier la réalisation de circuits dits normalement éteints; le second objectif de la thèse est la mise en place et l'adaptation de ces stratégies grâce à ces technologies émergentes, d'optimiser l'intégration et l'utilisation de celles-ci, et de les évaluer dans le but de qualifier leurs apports et leurs limitations pour les applications embarquées.

## 1.3. Projet de recherche en lien avec la thèse

Cette thèse a été menée dans le cadre du projet de recherche collaborative internationale intitulé MASTA (*MRAM Based Design, Test and Reliability for Ultra-Low-Power SoC*, conception, test et fiabilisation d'architectures à base de mémoires magnétiques pour les systèmes sur puce à très faible puissance), financé par l'Agence Nationale de la Recherche (bourse ANR-15-CE24-003-01). Ce projet fait intervenir trois laboratoires de recherche : l'Institut Technologique de Karlsruhe (KIT, www.kit.edu), situé à Karlsruhe, en Allemagne ; SPINTEC (www.spintec.fr) situé à Grenoble, en France ; et le LIRMM.

L'objectif de ce projet de recherche est l'investigation, la conception, le développement et l'analyse d'architectures hybrides pour les calculateurs dits normalement éteints où les mémoires magnétiques sont utilisées dans l'ensemble de la hiérarchie mémoire (registres, caches, mémoires principales...) en complément de la technologie CMOS traditionnelle (www.lirmm.fr/masta).

## 2. Contexte, état de l'art et problématique

## 2.1. Internet des Objets, réseaux de capteurs sans fils

Depuis la création des premiers réseaux informatiques à grande échelle dans les années 1960, qui après plusieurs décennies d'évolution, a permis d'obtenir le réseau de communication mondial « internet » tel qu'on le connaît aujourd'hui, l'interconnexion de capteurs et de détecteurs à ces réseaux pour la récupération d'informations à distance a toujours suscité un grand intérêt. Initialement filaires, l'utilisation de réseaux sans fils pour ce type de dispositifs a rapidement été motivée par des frais de déploiement et de maintenance élevés [2]. Il faudra toutefois attendre la toute fin des années 1990 avant de voir les premiers réseaux de capteurs sans fil connectés aux réseaux informatiques conventionnels, en particulier grâce aux projets Smart Dust [3], [4] et WINS (Wireless Integrated Network Sensors) [5]. Dès les débuts du projet Smart Dust, les plus grandes difficultés rencontrées étaient liées à l'énergie, et les participants au projet ont mis en évidence l'importance de l'efficacité énergétique des systèmes intégrés, jusqu'alors mise au second plan par les concepteurs en faveur des performances seules de ces systèmes. L'utilisation de récupérateurs d'énergie, en particulier des cellules photovoltaïques, était déjà envisagée pour répondre au problème de la densité énergétique du produit [3]. Aujourd'hui, plusieurs milliards de dispositifs sans fil sont connectés à internet et peuvent communiquer entre eux ou avec d'autres composants du réseau mondial, dans le cadre de ce qu'on appelle l'Internet des Objets. Si les différentes technologies utilisées pour réaliser ces dispositifs ont évolué au fil des années, la principale source de contraintes des premiers réseaux de capteurs sans fil, l'énergie, reste encore aujourd'hui le problème majeur. C'est cette question de l'optimisation de l'efficacité énergétique des systèmes sur puce très basse consommation pour l'Internet des Objets qui nous a motivé à réaliser ce projet.

## 2.1.1. Définition, domaines d'application et architecture

L'Internet des Objets est défini par l'Union Internationale des Télécommunication (UIT, ou ITU pour *International Telecommunication Union*) comme une infrastructure mondiale pour la société d'information interconnectant des objets, qu'ils soient physiques ou virtuels, grâce aux technologies de l'information et de la communication, pour disposer de services évolués [6]. Les objets sont dotés de dispositifs capables d'agir (actionneurs), de saisir une information (capteurs), de la traiter et/ou de la transmettre. Les technologies mises en œuvre, les supports et protocoles de communications, les types de dispositifs utilisés et leur comportement sont choisis pour répondre aux services et aux contraintes imposées par une application donnée.

Au-delà de l'Internet des Objets, dans le cas de déploiement de dispositifs sans fils servant essentiellement à la saisie d'informations relatives à un objet ou à un milieu, on parle plus

spécifiquement de réseau de capteurs sans fils (WSN, *Wireless Sensors Network*), où ces dispositifs sont appelés « nœuds capteur ». Un réseau de capteurs sans fil n'est pas nécessairement connecté au niveau mondial ni au niveau régional. Quel que soit l'échelle de ces réseaux, l'utilisation de telles infrastructures est présente dans de nombreux domaines, pour une très grande diversité d'application :

- dans la sécurité civile, pour la prévention et la gestion des catastrophes, d'origines naturelles ou humaines, la surveillance des personnes à risques ou encore la localisation de victimes après une catastrophe [7];

- dans l'agriculture, pour le suivi des événements météorologiques, la bonne utilisation et l'optimisation des ressources, le contrôle de maturité, la détection de maladies ou d'invasion de parasites et de nuisibles; dans l'élevage, pour le suivi des animaux domestiques, de leur santé, la détection de parturition et de ponte, la détection d'attaque de prédateurs [8];

- dans les villes (mais aussi bien au-delà), pour la gestion et l'optimisation du trafic urbain, des emplacements de stationnement, de l'acheminement et du traitement des eaux usées et des déchets, de la distribution de l'eau et de l'énergie, des services de livraison, des transports en commun, de la navigation des véhicules d'urgence et de secours, la surveillance des infrastructures routières et des bâtiments [9];

- dans la santé, pour le suivi à distance des conditions physiques des personnes, pour la détection de malaises, de chutes, d'évanouissements et autres situations de détresse, pour l'aide au diagnostic, pour la détection et le suivi d'épidémies, pour la détection de la contamination de l'eau et des produits comestibles, pour le suivi de la chaîne de froid des médicaments, des aliments et autres produits sensibles à la température [10];

- dans l'industrie, pour l'identification, la localisation, le suivi et la protection des objets, des outils, des marchandises et des personnes, pour l'optimisation des ressources, pour le diagnostic, la prise de décision et la reconfiguration automatisés, pour l'optimisation de la production en général [11];

- dans le secteur militaire, pour la détection, la localisation et le suivi de troupes, de véhicules de missiles et de drones, pour la détection de substances chimiques, d'armes biologiques et explosives, pour des services de navigation et de guidage [12].

On constate d'après cette liste non-exhaustive que les applications usant de réseaux de capteurs sans fil sont très nombreuses et ont des objectifs très différents. Les solutions techniques utilisées le sont aussi, si bien qu'il n'y a pas de solution générale couvrant tous les cas. Parmi les contraintes majeures, on retrouve :

- la taille des produits ;

- la capacité de transport des données, le débit, la latence, le taux d'échec et l'encombrement des réseaux de communication, quel que soit le type;

- les performances de calcul et de traitement des données ;

- l'entreposage des données;

- la sécurité des données, des biens et des personnes ;

- la fiabilité de l'application, dépendante de celle des nœuds et des autres acteurs ;

- l'autonomie, en terme de services et de gestion ;

- la flexibilité de l'architecture quant à son évolution, comme l'ajout de nœuds sur le réseau et

l'ajout de nouveaux services;

- le bilan énergétique, et dans le cas des produits sur récupérateur d'énergie et/ou sur accumulateurs d'énergie, l'autonomie en énergie.

Ce sont les spécifications de l'application et les contraintes techniques qu'elle impose qui vont guider le choix vers la solution la plus adaptée à la situation, voir adapter une solution existante et l'optimiser pour l'application.

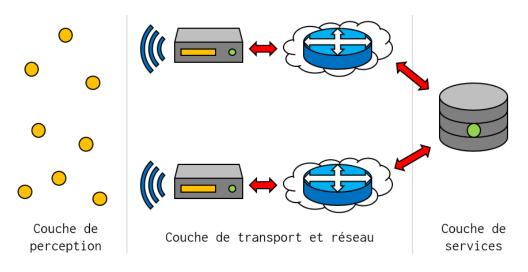

S'il n'y a pas de solution unique pour couvrir tous les cas, on retrouve toutefois, dans un grand nombre d'applications impliquant des réseaux de capteurs sans fil, une architecture typique, illustrée par la Figure 2-1, qui peut être décomposée en trois couches :

- la couche de perception, composée de nœuds au contact des objets ou de l'environnement à suivre;

- la couche de transport et de réseau, assurant la circulation des informations entre les différents acteurs du réseau, parfois capable de réaliser un traitement et/ou un entreposage local des données;

- la couche de services, réalisant l'entreposage, le traitement des données et la prise de décision.

Un réseau de capteurs sans fil fait intervenir de nombreux acteurs. Du nœud capteur qui récupère l'information jusqu'au serveur qui la transforme, en passant par les passerelles (gateways) et l'infrastructure réseau qui la transporte, chaque élément de la chaîne a une fonction qui lui est propre, avec son lot de contraintes techniques plus ou moins fortes. En effet, les éléments constituant la couche de services sont typiquement soumis à une charge de travail assez importante, afin de traiter le flot de données, plus ou moins important selon l'application, qui remonte jusqu'à eux. Les solutions techniques utilisées pour cette couche sont plutôt orientées performances de calcul et grande capacité d'entreposage des données. Les serveurs dédiés pour la gestion des services sont généralement placés dans des salles prévues, disposant d'une source d'énergie continue. Les éléments de la couche de transport n'ont pas toujours besoin d'une performance de calcul aussi grande que ceux de la couche de services, mais un traitement et un entreposage local des informations au niveau des passerelles est possible; cela doit être pris en compte au moment du choix de la solution. Si la

Figure 2-1: Représentation de l'architecture typique d'un réseau de capteurs sans fil

plupart des éléments réalisant la fonction réseau disposent d'une source d'énergie continue, les passerelles sont dans certains cas alimentées par batterie, et parfois associées à un récupérateur d'énergie (par exemple, des cellules photovoltaïques).

Quant aux éléments de la couche de perception, les nœuds capteurs, ceux-ci ne disposent pas d'une source d'énergie continue (dans le cadre d'un réseau de capteurs sans fil), et doivent nécessairement recourir à l'utilisation d'un ou plusieurs accumulateurs d'énergie (pile, batterie, super condensateur...) et parfois d'un ou plusieurs récupérateurs d'énergie. Cette contrainte technique impose une puissance consommée adaptée et une bonne gestion de l'énergie afin d'assurer une durée de vie longue du produit, et ainsi éviter des maintenances coûteuses trop régulières qui feraient rapidement grimper le coût total de l'application. Pour certaines d'entre-elles, notamment lorsqu'un dispositif doit être placé au près, sur ou dans un être vivant, humain comme animal, on demande également à ce que ces nœuds capteurs soient de petite taille, afin d'être le moins intrusif et/ou le plus discret possible. Or, cette dernière contrainte limite la taille des accumulateurs d'énergie et des récupérateurs d'énergie, ce qui rend la gestion de l'énergie encore plus critique. Concernant la puissance de calcul, celle-ci n'a pas besoin d'être très grande puisque la charge de travail d'un nœud capteur reste pour la plupart des applications très légère par rapport aux autres éléments de la chaîne. Cependant, cette charge de travail varie beaucoup d'une application à une autre, même à cette échelle, et va grandement impacter le choix du contrôleur et impacter la consommation en énergie du produit final.

Il est important de noter que la sécurité dans les applications de l'Internet des Objets suscite de plus en plus d'intérêt [13], et que les méthodes de sécurisation des données, qu'elles soient matérielles ou logicielles, nécessitent l'utilisation de ressources supplémentaires (calcul, capacité mémoire, modules de chiffrement, générateur de nombres aléatoires) et par conséquent plus d'énergie. De

(b)

même, certains services gourmands en ressources sont de plus en plus présents en tout point de la chaîne, tel que la mise à jour à distance des produits [14], service utile pour faire évoluer, pour corriger et pour assurer de manière générale une partie de la maintenance d'un produit sans avoir à intervenir physiquement sur celui-ci (opération onéreuse et pas réalisable sur tous les produits).

Si les dispositifs de la couche de perception, bien que très contraints par l'aspect énergétique, ont également besoin de plus de ressources pour intégrer plus de sécurité et de services, les éléments de la couche de services, qui nécessitent de grandes performances de calcul et une grande capacité d'entreposage des données, sont eux aussi soumis à la question de l'énergie, pour des raisons économiques, écologiques et de durée de vie du matériel.

Pour les nœuds capteurs à très basse consommation d'énergie, on préférera prendre des microcontrôleurs comme unité principale : ces derniers sont généralement de petite taille, à faible coût, consommant peut d'énergie et embarquant un maximum de fonctions nécessaires, évitant alors l'ajout de composants supplémentaires qui, la plupart du temps, augmenteraient l'encombrement, le coût et/ou l'énergie consommée du produit final. Comme illustré par la Figure 2-2 (a), la plupart des microcontrôleurs du commerce intègrent un processeur à jeu d'instruction réduit (RISC, Reduced Instruction Set Computer), au moins une mémoire non-volatile (utilisée principalement pour contenir le programme et les données statiques), une mémoire volatile (utilisée pour les données dynamiques), un régulateur de tension associé à un module de gestion de puissance, un ou plusieurs

Figure 2-2 : (a) architecture typique d'un microcontrôleur (simplifié) ; (b) architecture typique d'un microporcesseur à quatre cœurs et deux niveaux de cache (simplifié)

(a)

TYPICAL MICROCONTROLLER TYPICAL MICROPROCESSOR **UART CPU CPU** CPU **CPU CPU** SPI I2C Bus matrix Cache(s) TIMER Flash L2 cache Internal Bus matrix peripherals Independent peripherals External memories External peripherals

oscillateurs pour générer des signaux d'horloge, des contrôleurs d'entrées/sorties, des modules de communication, et parfois des périphériques pour le traitement de signaux analogiques. Puisqu'il n'y a actuellement pas une seule solution adaptée à l'ensemble des applications existantes, les fabricants offrent une très large gamme de microcontrôleurs avec des options bien différentes (type et puissance du processeur, périphériques, options d'économie d'énergie, type et capacité mémoire...) pour répondre aux besoins du marché; la Figure 2-2 (a) ne présente qu'une version simple de microcontrôleur.

Pour la couche de services, on préférera l'utilisation de contrôleurs de type micro-processeurs pour leurs performances de calculs, voir l'utilisation d'architectures dédiées ou reconfigurables, afin d'accélérer les calculs et les mouvements de données [15]. Illustrés par la Figure 2-2 (b), les micro-processeurs peuvent contenir un ou plusieurs processeurs, des antémémoires (aussi appelées mémoires caches, elles permettent d'accélérer l'accès aux données en limitant les mouvements de celles-ci, économisant ainsi du temps et de l'énergie) et quelques périphériques internes. Contrairement aux microcontrôleurs, les micro-processeurs n'intègrent typiquement pas les éléments de régulation de puissance ou de génération de signaux d'horloges, ces derniers étant externes, comme les mémoires principales (non-volatiles et volatiles) et une grande partie des périphériques.

La grande diversité des applications amène à une grande diversité des solutions; toutes sont soumises à la question de l'énergie; toutefois nous nous intéressons plus particulièrement aux applications où la contrainte énergétique est la plus forte : les réseaux de capteurs sans fils, et plus particulièrement les nœuds capteurs très basse puissance équipés de microcontrôleurs eux aussi à très faible consommation d'énergie.

## 2.1.2. Nœud capteur

#### a) Composition

Un nœud capteur est un dispositif intégrant plusieurs composants dont le rôle principal est de convertir une ou plusieurs informations relatives à un objet en informations numériques, de les mettre en forme, éventuellement de réaliser un traitement sur celles-ci, puis de les transmettre. Il dispose typiquement d'un microcontrôleur, d'un ou plusieurs modules radio (au moins un émetteur; la présence de récepteurs est optionnelle) et peut être équipé d'un ou plusieurs capteurs (et d'actionneurs dans les cas particuliers), d'un ou plusieurs accumulateurs d'énergie et dans certains cas d'un ou plusieurs récupérateurs d'énergie (Figure 2-3). La quantité et la nature de chacun de ces composants sont définies dans les spécifications de l'application.

Différents types d'accumulateurs d'énergie électriques sont utilisés pour alimenter les nœuds capteurs. Ils sont caractérisés par la technologie utilisée, leur tension nominale, la quantité de charge (et par extension la quantité d'énergie) qu'ils peuvent accumuler, le débit de charge (si rechargeable)

TYPICAL END NODE

COMMUNICATION (RADIO)

SENSORS

ACTUATORS

CONTROL

STORAGE

MICROCONTROLLER

Figure 2-3: Composition d'un nœud

et de décharge maximale, leur impédance interne, leur encombrement, leur capacité à être rechargés, leur dégradation en fonction de leur utilisation, leur perte naturelle d'énergie, et bien d'autres métriques. Plusieurs accumulateurs d'un même type peuvent être regroupés sous forme de batteries pour ajuster une partie de leurs caractéristiques (par exemple, la tension, la capacité en énergie, le débit maximum...) afin de les faire correspondre aux besoins de l'application. Le choix de l'accumulateur est très important car il est en relation directe avec la durée de vie du nœud. Il est également très dépendant de l'environnement dans lequel il va évoluer : les caractéristiques de l'accumulateur sont fonction des conditions de température et de pression. Leur tension, leur capacité, leur débit maximal, leur impédance interne, leur courant de fuite naturel varient au cours de leur existence ; ces variations doivent être prises en compte lors de l'estimation de l'autonomie du nœud capteur. L'utilisation de récupérateurs d'énergie et le remplacement de l'accumulateur ne sont pas toujours possibles ; il faut dans ces cas prévoir une solution capable de tenir suffisamment longtemps pour respecter les consignes de durée de vie du nœud capteur. Même si la récupération d'énergie ou le remplacement de l'accumulateur sont réalisables, la mise en place de ces solutions est parfois trop complexe pour être retenue.

### b) Comportement

L'énergie disponible sur un nœud capteur est limitée, et de nombreuses contraintes vont restreindre l'utilisation d'une partie des solutions techniques actuellement disponibles. La gestion de l'énergie est un point critique de l'application : il est nécessaire d'adapter le comportement du nœud et de mettre en place une stratégie pour optimiser la consommation d'énergie afin de garantir la durée de vie de l'application à moindre coût.

La mission principale d'un nœud capteur est de mesurer une grandeur physique et/ou de capturer un événement relatif à un objet, un environnement, afin de transmettre cette information. En fonction de la nature de l'information à relever et des besoins de l'application, le nœud capteur peut

avoir un comportement bien différent. Beaucoup d'applications n'ont pas besoin de réaliser un relevé d'information en continu, soit parce que l'information à relever possède une certaine inertie (par exemple, la température ambiante) et un échantillonnage trop fréquent générerait une redondance, soit parce que les besoins de l'application n'imposent pas un temps de réaction immédiat ou une fréquence d'échantillonnage élevée. Pour une partie des applications, le nœud capteur n'a besoin de travailler que dans une plage horaire spécifique, ou sur demande explicite d'une autre entité.

Le comportement du nœud capteur peut être dans la plupart des cas découpé en plusieurs phases : celles où il est actif, appelées phases d'activité; et celles où il est en attente d'un événement (synchrone, comme le signal d'une horloge, ou asynchrone), appelées phases de sommeil. Durant les phases d'activité, il est amené à mesurer une grandeur physique et/ou capturer en événement, transformer l'information, la mettre en forme, l'entreposer et/ou la transmettre [16]. Ces fonctions constituent typiquement les tâches principales d'un nœud capteur, mais d'autres services peuvent également être implémentés, par exemple : la mise à jour du programme applicatif; le diagnostic du système; une mise en veille prolongée...

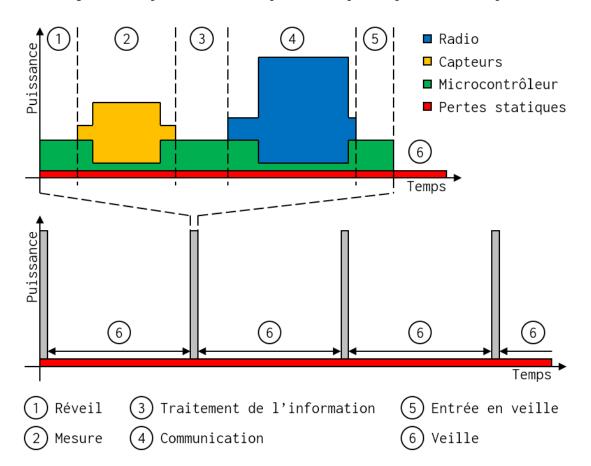

La Figure 2-4 présente le comportement le plus simple d'un nœud capteur au cours du temps, décomposé en six étapes, dont cinq réalisées durant la phase active : réveil (1); mesure d'une ou plusieurs grandeurs physiques et/ou capture d'événements (2); transformation, mise en forme et/ou entreposage de l'information (3); transmission de l'information (4); préparation à la phase de sommeil (5); et enfin la phase de sommeil (6).

L'utilisation d'un périphérique externe au microcontrôleur, par exemple un capteur ou un module de communication radio, peut également nécessiter plusieurs étapes nécessaires pour réaliser la fonction voulue avec celui-ci : mise en puissance, configuration, opération, récupération de données, arrêt... La gestion de ces composants est influencée par la stratégie de gestion de l'énergie.

Le réveil du nœud peut être synchrone, c'est-à-dire déclenché par un événement dont la fréquence d'apparition est connue. Cet événement est très souvent généré par une horloge dite temps-réel (RTC, *Real Time Clock*), un module pouvant être intégré dans le contrôleur du nœud capteur, assurant son réveil après une période de sommeil définie. Souvent dotés d'une fonction calendrier, les modules RTC peuvent être programmés pour réveiller un nœud à une heure et/ou à une date précise. Ces périphériques sont généralement indépendants, même intégrés au contrôleur ; de ce fait, ils peuvent continuer à opérer si ce dernier est dans un état de sommeil profond (cet état est détaillé dans la partie suivante). L'événement synchrone peut également être généré par un compteur interne au contrôleur, parfois par une composante du réseau si la solution de communication le permet [17].

Le réveil du nœud peut aussi être asynchrone, c'est-à-dire déclenché par un événement dont l'apparition n'est pas contrôlée et ne peut être prédite. Certains capteurs peuvent effectuer une mesure ou une capture en continu et générer un signal de réveil pour sortir le contrôleur de sa phase de sommeil. Ce dernier peut alors lancer une procédure spécifique suite à l'événement déclencheur, par exemple, lancer une alerte sur le réseau ou réaliser des mesures complémentaires et/ou plus précises. Cela permet d'augmenter la réactivité du nœud face à un événement en évitant d'augmenter la fréquence de réveil de celui-ci, permettant dans certains cas d'optimiser sa consommation d'énergie. Comme pour le réveil synchrone, un réveil asynchrone peut être demandé par le réseau.

Dans beaucoup d'applications, les deux types de réveils, synchrone et asynchrone, sont combinés. Cela permet au nœud d'être réactif à un ou plusieurs événements tout en assurant une activité minimale régulière, même si aucun événement n'a été capturé durant la période programmée. Ce comportement est souvent utilisé pour garantir une certaine sûreté de fonctionnement de l'application : si sa tâche périodique implique de communiquer avec le reste du réseau, il est possible de détecter si un nœud est déconnecté de celui-ci. Il peut alors être déclaré comme défaillant, et ce changement d'état est un événement pouvant faire l'objet d'une alerte.

Figure 2-4: Représentation du comportement le plus simple d'un nœud capteur

Quel que soit l'événement qui réveil le contrôleur, le nœud capteur peut passer une très grande partie de son temps dans sa phase de sommeil. Comme illustré par la Figure 2-4, le nœud consomme toujours un peu de puissance même s'il est inactif. Cette perte de courant, appelée fuite (*leakage*), peut être responsable d'une perte non négligeable de l'énergie disponible sur le nœud et réduire sa durée de vie. La part d'énergie perdue par la consommation statique d'un circuit est même d'autant plus grande que le nœud technologique est petit, et si le rapport temps actif sur temps inactif est suffisamment bas, cette consommation statique peut représenter la perte d'énergie majoritaire [18]. Pour limiter cette perte, différentes stratégies sont utilisées.

## 2.1.3. Stratégies pour l'économie d'énergie

La gestion de l'énergie disponible sur les nœuds capteurs est l'un des points critiques de l'application. Afin de réduire la consommation d'énergie d'un nœud capteur, plusieurs solutions disponibles sont employées.

#### a) Réduire la consommation d'énergie des périphériques externes

Comme introduit précédemment, le comportement du nœud capteur est divisé en phases d'activité et de sommeil. Durant les phases de sommeil, certains composants du nœud ne sont pas utilisés. S'ils disposent d'un mode d'économie d'énergie, la première solution revient à utiliser ce mode pour réduire le courant résiduel qui traverse ces composants. Au-delà des phases de sommeil, ce mécanisme, ainsi que tous les autres mécanismes suivants peuvent aussi être utilisés durant la phase d'activité lorsqu'un composant n'est pas utilisé.

Pour réduire encore l'énergie qu'ils consomment durant la phase de sommeil, l'alimentation de ces composants inactifs peut, dans une partie des cas et à l'exception du contrôleur principal, être coupée afin de supprimer le courant résiduel qui les traverse, même désactivés [19]. Pour que cette action soit efficace, il est nécessaire que le temps de sommeil soit suffisamment long pour que l'économie d'énergie faite pour chaque composant compense l'énergie nécessaire au redémarrage de celui-ci, l'énergie nécessaire à sa reconfiguration et à la sauvegarde de ses paramètres si besoin, et l'énergie perdue dans le système de gestion de sa ligne d'alimentation. En effet, il est parfois nécessaire d'ajouter des composants, qui consomment une certaine puissance en continu, pour gérer les lignes d'alimentation des autres composants. Bien évidemment, il faut que le gain sur la consommation d'énergie du nœud entier soit significatif pour justifier l'ajout de nouveaux composants, qui ont un coût financier et spatial.

Une autre stratégie consiste à différer des actions, comme un calcul ou le travail d'un composant, afin de réduire leur part de consommation d'énergie [20]. En effet, certaines actions n'ont pas besoin d'être réalisées à chaque réveil du nœud.

Dans la plupart des applications, l'information relevée n'a pas besoin d'être transmise dans l'immédiat aux autres objets du réseau. Il est alors possible de regrouper des données recueillies sur plusieurs minutes, plusieurs heures ou plusieurs jours et de n'envoyer qu'un seul message au réseau comportant l'ensemble des données de cette période, comme illustré par la Figure 2-5. Un message radio a un coût initial en énergie non négligeable à cause des différentes couches de protocole ajoutant chacune des informations nécessaires à l'infrastructure réseau (ces informations sont dépendantes des solutions techniques choisies; on retrouve dans la plupart des cas un signal de synchronisation, un identifiant, parfois un destinataire, un code de vérification ou de correction d'erreurs...), augmentant ainsi la taille du message, et donc son coût énergétique [21]. Certains protocoles radios imposent également une taille de message minimale et/ou l'utilisation de symboles non sécables pour représenter une taille fixe de données. Envoyer une donnée de petite taille n'est donc pas rentable car le coût énergétique de l'envoi est principalement dû à son encapsulation; si l'envoi des données peut être différé, il est préférable de réduire le nombre de messages envoyés en les regroupant. Cette méthode permet également de réduire la charge du réseau.

Figure 2-5 : Exemple de stratégie d'économie d'énergie par la réduction du nombre de messages envoyés

## b) Modes d'économie d'énergie dans les microcontrôleurs classiques

S'il n'est pas possible de couper directement l'alimentation en puissance du contrôleur, il est possible de réduire l'énergie qu'il consomme lorsqu'il n'est pas utilisé grâce aux différents mécanismes qu'il intègre. Les microcontrôleurs intègrent de nombreux mécanismes plus ou moins agressifs pour répondre au mieux aux différents cas, permettant ainsi aux développeurs d'optimiser l'énergie disponible dans leurs produits (quelques exemples : [22] [23] [24]) :

- arrêt du processeur ;

- arrêt des périphériques inutilisés (typiquement l'arrêt du rafraîchissement sur front d'horloge, mais leur alimentation peut aussi être coupée dans certains microcontrôleurs);

- arrêt d'un oscillateur externe (lorsqu'implémenté), qui consomme généralement plus qu'un oscillateur interne (typiquement de type RC); arrêt des boucles à verrouillage de phase (PLL, Phase Locked Loop) et autres synthétiseurs de signaux d'horloge; arrêt d'un oscillateur interne; plus généralement, diminution de la fréquence de fonctionnement;

- réduction de la tension d'alimentation interne en fonctionnement (limite la fréquence maximale et force l'arrêt de certains blocs comme la PLL en dessous d'une certaine tension);

- réduction de la tension d'alimentation interne à l'arrêt (mode rétention);

- mise en mode rétention des mémoires volatiles (interdisant alors leur utilisation);

- arrêt des régulateurs de tension principaux (à l'exception de certains périphériques dédiés notamment pour sortir le microcontrôleur de ce mode d'économie agressif, tous les blocs internes ne sont plus alimentés et les registres perdent leur contenu, de même pour les mémoires volatiles qui ne sont pas en mode rétention, alimentées par leur propre régulateur).

Il est possible d'utiliser plusieurs de ces mécanismes en même temps pour optimiser les gains, même de sélectionner des méthodes différentes en fonction des contraintes de chaque situation d'inactivité que le microcontrôleur peut rencontrer lors du déroulement de l'application (phase d'inactivité très courte, besoin d'une réactivité élevée, nécessité de garder une partie du système actif lors de l'attente d'un périphérique interne ou externe, durant une communication...). Certains mécanismes ne sont pas immédiats et ont un impact sur le fonctionnement du microcontrôleur, sur l'entrée et/ou sur la sortie d'un mode d'économie d'énergie. Les régulateurs de tension ne peuvent pas fournir la tension voulue instantanément après un changement de consigne; le temps nécessaire pour l'atteindre retarde l'utilisation de composants internes et/ou un changement de la fréquence de fonctionnement (typiquement quelques microsecondes). Le démarrage d'un générateur de signal d'horloge peut prendre du temps s'il est nécessaire d'attendre sa stabilisation (par exemple, un générateur à quartz, une PLL...). Si l'alimentation d'un bloc est coupée, celui-ci doit être reconfiguré après la remise sous tension. De manière générale, plus le mode d'économie d'énergie est agressif, plus le délai avant le rétablissement à un mode normal ou même à un mode moins agressif sera long. Dans

le cas de la perte du contenu des registres ou des mémoires, il est parfois nécessaire de relancer le programme applicatif depuis le début, ou de déplacer ce contenu soit dans une mémoire non-volatile, soit dans une mémoire volatile qui ne perdra pas son contenu lors du changement de mode (gardée fonctionnelle ou placée en mode rétention). C'est pourquoi ces modes doivent être utilisés judicieusement afin que, d'une part, l'énergie dépensée après une étape de sommeil courte, en prenant en compte l'entrée dans ce mode, le retour à l'état voulue et l'énergie dépensé durant le sommeil, ne soit pas plus grande que celle nécessaire à un mode moins agressif, et que, d'autre part, les contraintes de réactivité de l'application soient respectées. Le temps de réactivité requis par les applications communes peut varier de quelques microsecondes à quelques secondes; et leur fréquence de réveil, qui détermine le temps pouvant être passé en sommeil, peut lui varier de quelques millisecondes à plusieurs heures, voire plusieurs jours [25]. Certaines stratégies ne sont tout simplement pas applicables pour des fréquences de réveil trop élevées.

La Figure 2-6 illustre la différence entre une stratégie de mise en veille simple d'un système (a), réduisant fortement la puissance consommée par celui-ci, et une stratégie de mise hors tension (b), plus agressive quant à la réduction des courants résiduels mais demandant des opérations de démarrage et d'arrêt plus longues.

Pour une application dont les réveils sont uniquement synchrones, c'est-à-dire connus et prévisibles, le choix de la stratégie optimale peut être étudiée. Mais dans le cas où des réveils asynchrones sont requis pour l'application, ce choix devient beaucoup plus complexe, car certains événements sont trop imprévisibles pour tenter une adaptation dynamique de la stratégie d'économie d'énergie. La grande variété des mécanismes dédiés à la réduction de la consommation d'énergie, leurs différentes combinaisons possibles et l'incertitude liée au comportement du nœud capteur et des événements extérieurs sont autant de facteurs qui compliquent le choix d'une stratégie d'économie d'énergie pour les développeurs de nœuds capteurs.

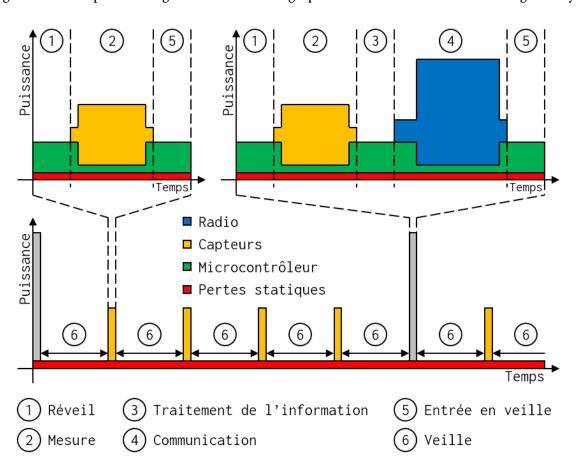

#### c) Systèmes normalement éteints

Afin de pouvoir profiter du gain d'énergie offert en coupant l'alimentation du processeur et des autres composants internes aux microcontrôleurs sans avoir à redémarrer entièrement l'application, il est possible de sauvegarder leur état dans des éléments mémoires prévus à cet effet. Ces mémoires peuvent être de nature volatile et seront alors placées en mode rétention, consommant toujours un peu d'énergie et nécessitant un régulateur de tension dédié ; ou bien non-volatile, permettant une coupure de l'alimentation de tous ces modules. Dans ce dernier cas, on parle de système normalement éteint (*Normally-Off Computing*) car son alimentation est coupée lors de son état stable, la phase de sommeil [20]. À la remise sous tension du processeur et des autres composants internes, l'état précédent la mise hors tension est restauré sans avoir à relancer la totalité du programme applicatif. Cette méthode, illustrée par la Figure 2-7, est dans la plupart des cas plus rapide et plus économe en énergie qu'un redémarrage complet du système [26].

Restore

Backup

Backup

Dynamic

Backup

Backup

Backup

Figure 2-7: Stratégie de réduction d'énergie - Système normalement éteint

Dans la hiérarchie mémoire du microcontrôleur, plusieurs éléments contiennent l'état du système : les mémoires principales (programme et données), les registres du processeur et les registres des périphériques. La mémoire programme est typiquement de technologie Flash, donc non-volatile. Elle pourrait toutefois être remplacée par une autre technologie mémoire non-volatile. La mémoire

de données est quant à elle volatile (typiquement SRAM), il est donc nécessaire d'utiliser une mémoire non-volatile à la place ou de sauver son contenu dans une mémoire non-volatile, dans la mémoire programme par exemple, mais cette opération de copie prendrait du temps et de l'énergie. Pour la sauvegarde du contenu des registres, ceux du processeur ou ceux des périphériques, cela va dépendre de la solution utilisée et de la pertinence de cette opération, dépendant de la fonction de chaque bascule de ces composants.

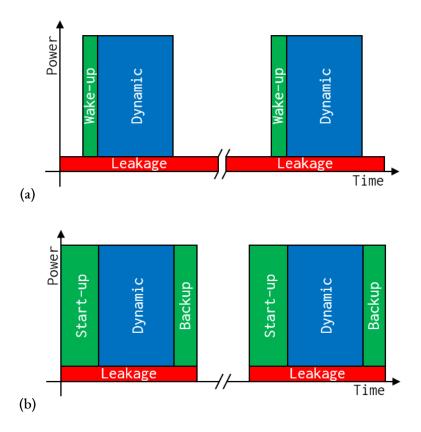

Il existe deux méthodologies pour la sauvegarde de l'état d'un système : la sauvegarde implicite, réalisée à chaque changement d'état ; et la sauvegarde explicite, événementielle, demandée soit par le matériel soit par le logiciel. Dans le premier cas, celui de la sauvegarde implicite, des bascules et des verrous purement non-volatiles sont utilisés. Dans le second cas, la sauvegarde explicite, plusieurs solutions sont possibles : l'utilisation de bascules hybrides, le transfert du contenu des bascules dans une matrice mémoire dédiée ou le transfert dans la mémoire principale.

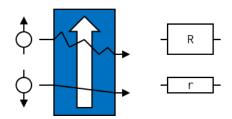

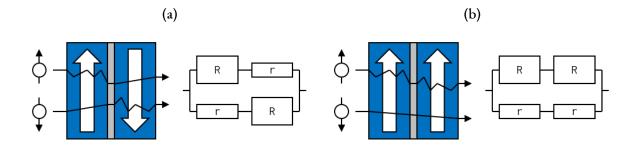

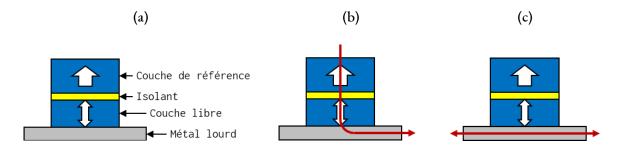

Un verrou ou une bascule non-volatile entrepose directement son contenu dans des éléments non-volatiles (un seul verrou non-volatile typiquement pour la bascule ; l'autre est volatile). Une bascule hybride possède une partie volatile, fonctionnant comme une bascule classique, et une partie non-volatile qui va copier ou restaurer le contenu de la partie volatile sur commande externe (comme précédemment, un seul des deux verrous voit son contenu sauvegardé par la partie non-volatile) [27] [28]. Il existe également des éléments semi-volatiles, c'est-à-dire qui ne maintiennent leur contenu que pour une durée généralement fixée à la conception. Ne permettant pas de sauver des données sur le long terme, ils sont toutefois utilisés pour maintenir un état lors de microcoupures. La Figure 2-8 représente le fonctionnement d'une bascule hybride.

Figure 2-8: Représentation d'une bascule hybride [27]

Les signaux de commandes d'écriture et de lecture de la partie non-volatile des cellules hybrides, ainsi que la logique générant ces signaux sont mutualisés entre plusieurs bascules afin de réduire la taille et la consommation d'énergie du contrôleur qui leur est dédié. Chacune de ces actions est alors parallélisée entre les bascules mais il est parfois nécessaire de découper la sauvegarde du système complet en plusieurs cycles. En effet, l'écriture d'un trop grand nombre de bascules en parallèle peut

provoquer un pic de consommation de courant trop grand pour les lignes d'alimentations internes. Il est parfois nécessaire de répartir cette charge dans la durée, et le nombre de bascules positionnées sur une même ligne doit être limité lors du placement des cellules dans le circuit [27].

Les cellules non-volatiles sont plus compactes que les cellules hybrides et ne nécessitent pas de circuit de contrôle dédié; toutefois, selon la solution technologique retenue, les éléments non-volatiles peuvent être responsables d'une performance moindre ou une consommation d'énergie plus élevée que des bascules volatiles classiques, c'est pourquoi la solution hybride est un bon compromis : durant l'écoulement normal du programme, la partie volatile est utilisée. Celle-ci étant comparable à une cellule classique, le processeur obtient des performances similaires à son implémentation volatile; la partie volatile n'est utilisée que pour sauver et restaurer son état.

Toutes les informations qui décrivent l'état d'un système n'ont pas besoin d'être sauvées pour être disponibles au réveil du microcontrôleur. En effet, certaines d'entre elles sont inutiles au réveil car erronées ou remplacées. Par exemple, les différents étages du processeur sont nettoyés et rechargés au redémarrage pour assurer la cohérence de leur contenu; la synchronisation avec les opérations de lecture et d'écriture en mémoire doit être faite avant l'entrée en phase de sommeil, l'état du bus et des contrôleurs des banques mémoires est donc réinitialisé; l'état des registres à décalage des modules de communication sont obsolètes au réveil... Le remplacement des bascules volatiles par leurs homologues hybrides doit dans l'idéal être fait au cas-par-cas afin d'optimiser l'énergie de la sauvegarde et de la restauration de leur état, et potentiellement optimiser le temps de ces opérations si elles nécessitent plus d'un cycle, mais ce n'est pas toujours une tâche aisée, en particulier à cause du grand nombre de bascules présent dans ces architectures.

Pour que cette stratégie soit efficace d'un point de vue énergétique, il est nécessaire que le temps de sommeil soit suffisamment long pour que la perte d'énergie due à la puissance statique consommée  $P_{Leakage}$  (alors non dépensée) soit plus grande que l'énergie nécessaire à la sauvegarde  $E_{Backup}$  et à la restauration  $E_{Restore}$  de l'état du système [29] (on néglige dans ce cas  $E_{Startup}$  correspondant à l'énergie de remise sous tension du système):

$$E_{Sleep} \ge E_{Backup} + E_{Restore}$$

2-1

On peut en déduire le temps de sommeil  $T_{Sleep}$  minimal pour que l'opération soit efficace :

$$T_{Sleep} \ge \frac{E_{Backup} + E_{Restore}}{P_{Leakage}}$$

2-2

Lorsque le microcontrôleur peut être réveillé par des événements externes à celui-ci, il n'est pas toujours possible de prédire la durée des phases de sommeil, c'est pourquoi ce temps minimal  $T_{Sleep}$  doit être le plus petit possible. Pour cela, les opérations de sauvegarde et de restaurations doivent non seulement être rapides mais aussi les plus économes en énergie.

Pour intégrer cette stratégie dans des microcontrôleurs, il est nécessaire de réaliser une évaluation en profondeur de cette dernière, afin de quantifier les gains potentiels et les possibles contraintes, mais aussi pour l'optimiser et ainsi profiter au mieux des bénéfices de celle-ci.

## 2.2. Technologies émergentes

Les différentes stratégies présentées dans la partie précédente ciblent en premier lieu la réduction de l'énergie perdue par les courants de fuite des composants. Bien qu'elles aient une certaine efficacité contre ces pertes d'énergie, elles imposent un développement supplémentaire pour être mises en place et ne sont pas toujours sans contrainte (compromis entre efficacité énergétique, réactivité et complexité de chaque solution). C'est pourquoi l'intégration de technologies émergentes dans les systèmes sur puces en complément ou en remplacement des technologies traditionnelles est étudiée.

### 2.2.1. FD-SOI 28 nm

En effet, les limitations de la technologie traditionnelle CMOS sur substrat massif (bulk) sont devenues une réelle contrainte quant à l'évolution des systèmes sur puces ces dernières années. Si la réduction de la taille du transistor, rendue possible grâce à l'amélioration de la finesse de gravure, a permis d'augmenter la densité et les performances des systèmes sur puces, la densité de puissance a quant à elle augmenté [30]. Cette augmentation de la densité de puissance, à laquelle les courants de fuite contribuent plus que l'activité dynamique lorsque les largeurs de grille de transistor sont inférieures à une trentaine de nanomètres, pose d'importants problèmes de dissipation thermique. D'autres problèmes de fiabilité et de rentabilité du processus de fabrication n'encouragent également pas la poursuite d'une finesse de gravure toujours plus grande dans cette technologie [31]. En réponse à ces limitations de la technologie CMOS sur substrat massif, d'autres architectures CMOS sont développées. Les principales alternatives sont le FinFET (Fin-shaped Field Effect Transistor, transistor à effet de champ en forme d'ailette), orienté hautes performances; et la FD-SOI (Fully-Depleted Silicon On Insulator, silicium sur isolant à déplétion complète), dynamiquement ajustable entre performances et basse consommation énergétique.

L'innovation principale de la technologie FD-SOI consiste à introduire une couche d'oxyde afin d'isoler le substrat du canal, du drain et de la source du transistor. Cette isolation, même si pas parfaite, va d'une part permettre de réduire grandement les courants de fuite du transistor entre ces zones (canal, drain et source) et le substrat, et d'autre part permettre des polarisations de ce dernier plus importantes et alors plus intéressantes que ce qui peut être fait avec la technologie classique sur substrat massif, limitée par des effets diodes internes. Par conséquent, l'ajustement dynamique du seuil du transistor est plus facile et bien plus grand, permettant une optimisation accrue de l'efficacité énergétique des circuits intégrés et de leurs performances [32].

#### 2.2.2. Mémoires non-volatiles

Au-delà de la partie logique, les mémoires embarquées font aussi l'objet d'études depuis plusieurs années pour être remplacées par des technologies plus rapides, plus flexibles et moins gourmandes en énergie [33]. Dans la hiérarchie du microcontrôleur, plusieurs types d'éléments mémoires sont utilisés : les bascules et par extension les registres ; la mémoire de données et la mémoire programme. Chaque élément de cette hiérarchie est une piste d'amélioration qui doit être explorée afin d'optimiser au mieux l'énergie consommée par le contrôleur. Typiquement, les bascules sont volatiles, de même que la mémoire de données ; la mémoire programme elle est non-volatile. Pour obtenir l'un des modes d'économie d'énergie les plus agressifs, un système normalement éteint, il est nécessaire que les éléments mémoires volatiles ne le soient plus. Différentes technologies mémoires non-volatiles sont étudiées pour être intégrées dans les microcontrôleurs, soit pour compléter soit pour remplacer les solutions actuelles.

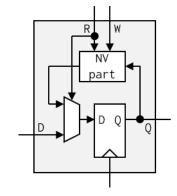

#### a) Mémoire Flash

Les mémoires Flash, et plus particulièrement celles de type NOR, sont déjà présentes dans la plupart des microcontrôleurs en particulier comme mémoire programme [34]. Une cellule mémoire est composée d'un transistor, similaire à un transistor MOSFET classique mais disposant d'une « seconde grille » dite flottante, c'est-à-dire qui n'est pas connectée à l'un des terminaux du composant comme illustré par la Figure 2-9 (a). Cette grille située dans l'oxyde isolant de la première grille (alors appelée grille de contrôle) modifie la tension de seuil du transistor en fonction des charges qui y sont emprisonnées. La tension nécessaire à appliquer sur la grille de contrôle pour ouvrir le canal entre la source et le drain du transistor est donc dépendante de l'état de la grille flottante ; c'est grâce à cette variation que la valeur « enregistrée » est lue. Pour charger la grille flottante, une forte tension est appliquée sur la grille de contrôle et le drain, forçant alors un fort courant à traverser le canal du transistor et augmentant sa température. Les électrons traversent alors l'isolant ; ce phénomène est appelé « injection de charges chaudes » (HCI, *Hot Carrier Injection*, Figure 2-9 (b)) [35]. Pour la décharger, une forte tension doit être appliquée entre le drain et la grille de contrôle (la source reste ouverte) ; un effet tunnel décharge la grille flottante (Figure 2-9 (c)).

Il existe deux types d'agencement de mémoire Flash très répandues : le type NOR (« non ou ») et le type NAND (« non et »). Ces noms font référence à l'architecture utilisée pour chacune de ces mémoires. Cette différence dans l'implémentation de banque mémoire Flash permet d'optimiser une partie de leurs métriques : le type NAND a une bien meilleure densité, des temps de programmation et d'effacement plus courts et un coût de fabrication moins élevé que le type NOR ; cependant le temps d'accès en lecture est beaucoup plus grand et il ne supporte pas la méthode d'accès aléatoire en lecture [36] [37]. Les microcontrôleurs ont besoin d'accéder à leur mémoire programme

(typiquement Flash) rapidement et de façon aléatoire, c'est pourquoi le type NOR est utilisé dans ces composants.

Figure 2-9 : (a) transistor Flash à grille flottante [34] [35] ; (b) programmation de la mémoire Flash ; (c) effacement de la mémoire Flash

Cependant, cette technologie a ses contraintes. Les mémoires Flash de type NOR, même si plus rapides que le type NAND sur ce point, sont limitées en vitesse de lecture (typiquement quelques dizaines de mégahertz). Des cycles d'attentes sont nécessaires pour opérer à des cadences plus élevées, entraînent une dégradation des performances (due à une réduction du nombre d'instructions par cycle). Ce type de mémoire ne supporte pas l'écriture directe. Il n'est pas possible d'effacer une valeur isolée sans affecter une partie de la mémoire. Pour effacer une valeur, il faut effacer la page où elle se situe, et donc potentiellement effacer d'autres données. Cette opération est coûteuse en temps et en énergie, en plus de la programmation ou reprogrammation de chaque donnée, et l'endurance des mémoires Flash est limitée.

#### b) Mémoires ferroélectriques

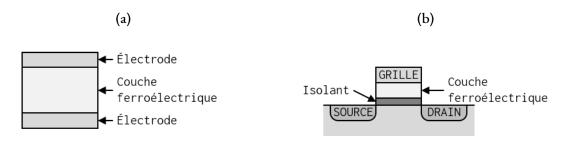

Les mémoires ferroélectriques (lorsqu'on parle de banque, FeRAM ou FRAM) utilisent des cellules composées d'un condensateur ferroélectrique, servant à entreposer une information, et d'un transistor MOS classique, servant à isoler l'élément mémoire des autres cellules logiques d'un système. Le condensateur ferroélectrique utilise un matériau ferroélectrique et non pas un isolant diélectrique comme la plupart des condensateurs classiques [38] (Figure 2-10 (a)). Ce matériau ferroélectrique est polarisé lorsqu'il est soumis à un champ électrique suffisamment fort, champ électrique généré lorsqu'une tension est appliquée entre les deux électrodes du condensateur. Pour lire la valeur inscrite, le contenu de la cellule est effacé : la réaction en courant est différente en fonction de la polarisation de la couche ferroélectrique ; elle permet de déterminer cette valeur. La lecture est par conséquent destructrice, et la donnée doit être réécrite s'il est nécessaire de la conserver [39]. Pour contourner cette contrainte, des transistors FeFET (Ferroelectric Field Effect Transistor) utilisant un matériau ferroélectrique entre la grille et le substrat sont développés (Figure 2-10 (b));

Figure 2-10 : (a) composant mémoire ferroélectrique ; (b) transistor ferroélectrique (FeFET)

leur fonctionnement est similaire à celui de la technologie Flash et il est possible de les réaliser dans un nœud technologique avancé [40] [41].

Plus flexible que la technologie Flash, la solution ferroélectrique ne l'a cependant pas (encore) remplacée : la structure des matériaux ferroélectriques est complexe et rend son intégration et la miniaturisation des cellules mémoires difficiles à réaliser [42]. Toutefois cette technologie est toujours étudiée aujourd'hui, et des microcontrôleurs très basse consommation utilisant celle-ci sont commercialisés depuis quelques années : Texas Instrument, au travers de sa série de microcontrôleurs MSP430 [43], met en avant les avantages de la FRAM par rapport à la mémoire Flash (plus flexible car à accès direct, meilleure endurance, permettant d'obtenir une meilleure efficacité énergétique des produits sur batterie) pour les applications de type nœuds capteurs à contraintes énergétiques fortes.

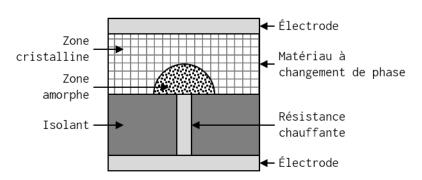

#### c) Mémoires à changement de phase

Les mémoires à changement de phase (PCM, *Phase Change Memory*, parfois PCRAM) utilisent les propriétés de matériaux tel que les verres de chalcogénure. La résistance de ce matériau change en fonction de sa structure : c'est cette propriété qui est utilisée pour entreposer une donnée. Cette structure est sensible à la température : à l'aide d'une résistance traversée par un courant plus ou moins fort, le matériau à changement de phase est chauffé à une température précise et durant un temps suffisamment long pour rendre sa structure cristalline où sa résistance est la plus faible, ou amorphe où sa résistance est la plus élevée. Il n'est pas nécessaire de rendre la structure du matériau complétement amorphe ; créer une région assez grande pour obtenir la variation de résistance désirée est suffisant (Figure 2-11).

La mesure de sa résistance permet de lire la valeur [44]. Comme pour beaucoup d'autres technologies, elle peut être associée à un transistor pour l'isoler du circuit. En comparaison à la mémoire Flash, les banques de mémoire à changement de phase ont une meilleure endurance, sont plus rapides en lecture et en écriture, et supportent l'accès aléatoire.