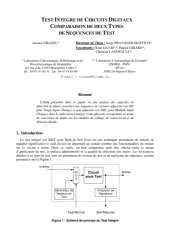

Test Intégré de Circuits Digitaux : Comparaison de deux types de Séquences de Test

Résumé

L'étude présentée dans ce papier est une analyse des capacités de détection de fautes associées aux séquences de vecteurs adjacents (ou SIC pour Single Input Change) et non adjacents (ou MIC pour Multiple Input Change), dans le cadre du test intégré. Cette efficacité est exprimée en terme de couverture de fautes sur les modèles de collage, de court-circuit et de délai de chemin.

Fichier principal

TEST_INTEGRE_DE_CIRCUITS_DIGITAUX_COMPARAISON_DE_D.pdf (68.27 Ko)

Télécharger le fichier

TEST_INTEGRE_DE_CIRCUITS_DIGITAUX_COMPARAISON_DE_D.pdf (68.27 Ko)

Télécharger le fichier

| Origine | Fichiers produits par l'(les) auteur(s) |

|---|

Loading...